- •Перечень сокращений

- •Предисловие

- •Введение

- •Часть 1. Архитектура и аппаратные средства микроконтроллера LPC214x

- •1.1 Общие сведения о микроконтроллерах LPC214x

- •1.2 Программистская модель процессорного ядра ARM7TDMI

- •1.2.1 Режимы работы ядра ARM7

- •1.2.2 Система регистров

- •1.2.3 Слово состояния программы

- •1.2.4 Организация памяти

- •1.3 Система команд

- •1.3.1 Команды арифметической и логической обработки

- •1.3.2 Команды умножения

- •1.3.3 Команды регистровой пересылки

- •1.3.4 Команды загрузки и сохранения регистров

- •1.3.5 Команды пакетного обмена с памятью

- •1.3.6 Команды передачи управления

- •1.3.7 Команды обращения к слову состояния программы

- •1.4 Методы адресации

- •1.4.1 Непосредственная адресация

- •1.4.2 Регистровая адресация

- •1.4.3 Косвенная адресация

- •1.4.4 Индексная адресация

- •1.5 Процедура начальной загрузки и режимы отображения памяти

- •1.6 Обработка исключительных ситуаций

- •1.7 Система тактирования

- •1.7.1 Выбор тактовой частоты микроконтроллера

- •1.7.2 Настройка тактирования периферийных устройств

- •1.8 Модуль ускорения памяти

- •1.9 Внешние выводы микроконтроллера

- •1.9.1 Служебные контакты

- •1.9.2 Программно-управляемые линии ввода-вывода

- •1.9.3 Альтернативные функции линий ввода вывода

- •1.10 Цифровые порты ввода-вывода

- •1.10.1 Управление портом через низкоскоростную шину

- •1.10.2 Управление портом через высокоскоростную шину

- •1.11 Система прерываний

- •1.11.1 Назначение системы прерываний

- •1.11.2 Процесс обработки прерываний IRQ

- •1.11.3 Процесс обработки быстрых прерываний FIQ

- •1.11.4 Регистры управления системой прерываний

- •1.11.5 Порядок настройки прерывания IRQ

- •1.11.6 Порядок настройки быстрого прерывания FIQ

- •1.11.7 Процедура обработки прерывания

- •1.11.8 Задержка обработки прерывания

- •1.12 Внешние прерывания

- •1.12.1 Регистры управления блоком внешних прерываний

- •1.12.2 Порядок настройки блока внешних прерываний

- •1.13 Таймеры-счетчики

- •1.13.1 Режим таймера и схема совпадения

- •1.13.2 Режим счетчика

- •1.13.3 Схема захвата

- •1.13.4 Управляющие регистры

- •1.13.5 Формирование интервалов времени через систему прерываний

- •1.13.6 Измерение периода и длительности импульса с помощью устройства захвата

- •1.13.7 Подсчет числа импульсов в единицу времени

- •1.14 Широтно-импульсный модулятор

- •1.14.1 Основы функционирования

- •1.14.2 Дополнительные возможности

- •1.14.3 Регистры управления ШИМ

- •1.14.4 Порядок настройки ШИМ

- •1.15 Аналого-цифровые преобразователи

- •1.15.1 Краткие сведения о встроенных АЦП

- •1.15.2 Общие рекомендации по использованию АЦП

- •1.15.3 Управляющие регистры

- •1.15.4 Порядок настройки АЦП

- •1.15.5 Программный запуск аналого-цифрового преобразователя

- •1.15.6 Запуск аналого-цифрового преобразователя по таймеру

- •1.15.7 Программный опрос готовности АЦП

- •1.15.8 Опрос готовности АЦП по прерыванию

- •1.15.9 Считывание и масштабирование результата АЦП

- •1.16 Цифро-аналоговый преобразователь

- •1.16.1 Регистр управления ЦАП

- •1.16.2 Рекомендации по применению ЦАП

- •1.17 Последовательный синхронный приемо-передатчик SPI

- •1.17.1 Назначение и основы функционирования интерфейса SPI

- •1.17.2 Управляющие регистры

- •1.17.3 Передача и прием данных в режиме ведущего

- •1.17.4 Передача и прием данных в режиме ведомого

- •1.18 Последовательный синхронный приемо-передатчик I2С

- •1.18.1 Назначение и основы функционирования интерфейса I2С

- •1.18.2 Управляющие регистры

- •1.18.3 Настройка модуля I2C

- •1.18.4 Типовые циклы обмена данными по шине I2C

- •1.19 Последовательный асинхронный приемопередатчик UART

- •1.19.1 Назначение и основы функционирования порта UART

- •1.19.2 Управляющие регистры

- •1.19.3 Настройка порта UART

- •1.19.4 Прием байта с опросом флага

- •1.19.5 Передача байта с опросом флага

- •1.19.6 Прием и передача данных с использованием прерываний

- •1.19.7 Прием и передача пакетов данных

- •1.19.8 Диагностика ошибок

- •1.19.9 Автоматическая настройка скорости

- •1.20 Часы реального времени

- •1.20.1 Основные возможности часов реального времени

- •1.20.2 Управляющие регистры

- •1.20.3 Рекомендации по применению

- •1.21 Управление питанием и идентификация источников сброса

- •1.21.1 Краткие сведения о мониторе питания

- •1.21.2 Управляющие регистры

- •Часть 2. Разработка и отладка программ с помощью современных инструментальных средств

- •2.1 Форматы представления чисел

- •2.1.1 Основные коды представления целых чисел

- •2.1.2 Форматы представление целых чисел, приятные в языке Си

- •2.1.3 Форматы чисел c плавающей точкой стандарта IEEE754

- •2.2 Основы программирования на языке Си

- •2.2.1 Структура программы

- •2.2.2 Числовые константы

- •2.2.3 Переменные и именованные константы

- •2.2.4 Оператор присваивания, выражения и операции

- •2.2.5 Условный оператор

- •2.2.6 Приведение и преобразование типов

- •2.2.7 Массивы

- •2.2.8 Строки символов

- •2.2.9 Структуры

- •2.2.10 Объединения

- •2.2.11 Указатели

- •2.2.12 Ветвление

- •2.2.13 Множественное ветвление

- •2.2.14 Цикл со счетчиком

- •2.2.15 Циклы с предусловием и постусловием

- •2.2.16 Функции

- •2.2.17 Некоторые директивы компилятора

- •2.2.18 Библиотека математических функций MATH.h

- •2.2.19 Функция создания форматированных строк SNPRINTF

- •2.2.20 Ассемблер в Си-программах

- •2.3 Интегрированная среда разработки Keil µVision 4

- •2.3.1 Создание проекта

- •2.3.2 Создание файла программы

- •2.3.3 Настройка проекта

- •2.3.4 Набор текста программы

- •2.3.5 Компиляция программы

- •2.3.6 Отладка программы

- •2.3.7 Основные отладочные инструменты среды Keil µVision 4

- •2.3.8 Управление распределением памяти

- •2.4 Методика отладки программ

- •2.4.1 Быстрый поиск ошибок

- •2.4.2 Ввод и вывод дискретных сигналов

- •2.4.3 Таймер-счетчик. Формирование интервалов времени

- •2.4.4 Таймер-счетчик. Формирование внешних сигналов совпадения

- •2.4.5 Таймер-счетчик. Счетчик внешних событий

- •2.4.6 Таймер-счетчик. Устройство захвата

- •2.4.7 Широтно-импульсный модулятор

- •2.4.8 Аналого-цифровой преобразователь

- •2.4.9 Цифро-аналоговый преобразователь

- •2.4.10 Приемопередатчик SPI

- •2.4.11 Приемопередатчик I2C

- •2.4.12 Приемопередатчик UART

- •2.4.13 Часы реального времени

- •2.5 О программировании ARM7 на ассемблере

- •2.5.1 Основные правила записи программ на ассемблере

- •2.5.2 Псевдокоманды

- •2.5.3 Директивы ассемблера

- •2.5.4 Макросы

- •2.5.5 Пример простой программы

- •2.6 Распространенные средства разработки и отладки

- •2.6.1 Демонстрационные платы EA-EDU-001 и EA-EDU-011

- •2.6.2 Внутрисхемный отладчик J-Link

- •2.6.3 Утилиты программирования ПЗУ LPC Flash Utility и FlashMagic

- •2.6.4 Программа-терминал 232Analyzer

- •2.6.5 Низкоуровневый редактор диска DMDE

- •Часть 3. Решение типовых задач локального управления

- •3.1 Формирование временной задержки с помощью цикла

- •3.1.1 Задание

- •3.1.2 Общие рекомендации

- •3.1.3 Алгоритм программы

- •3.1.4 Отладка

- •3.1.5 Дополнительные сведения о формировании временной задержки

- •3.2 Формирование дискретного сигнала с помощью таймера

- •3.2.1 Задание

- •3.2.2 Общие рекомендации

- •3.2.3 Алгоритм программы

- •3.3 Опрос дискретного датчика или кнопки

- •3.3.1 Задание

- •3.3.2 Общие рекомендации

- •3.3.3 Алгоритм программы

- •3.3.4 Отладка

- •3.4 Опрос состояния механических контактов с подавлением дребезга

- •3.4.1 Задание

- •3.4.2 Общие рекомендации

- •3.4.3 Алгоритм программы

- •3.4.4 Отладка

- •3.5 Опрос клавиатуры с автоповтором

- •3.5.1 Задание

- •3.5.2 Общие рекомендации

- •3.5.3 Алгоритм программы

- •3.5.4 Отладка

- •3.6 Формирование импульсного управляющего сигнала с помощью модуля ШИМ

- •3.6.1 Задание

- •3.6.2 Общие сведения

- •3.6.3 Алгоритм программы

- •3.6.4 Отладка

- •3.6.5 Синхронизация внешним сигналом

- •3.7 Формирование сигналов специальной формы с помощью ЦАП

- •3.7.1 Задание

- •3.7.2 Основы

- •3.7.3 Алгоритм программы

- •3.7.4 Повышение точности генерирования частоты

- •3.7.5 Выбор числа дискрет

- •3.8 Управление двухфазным шаговым двигателем

- •3.8.1 Задание

- •3.8.2 Общие сведения

- •3.8.3 Алгоритм программы

- •3.9 Применение ШИМ для формирования низкочастотных аналоговых сигналов

- •3.9.1 Задание

- •3.9.2 Основные сведения

- •3.9.3 Алгоритм основной программы

- •3.9.4 Алгоритм процедуры обработки прерывания

- •3.10 Управление символьным жидкокристаллическим индикатором

- •3.10.1 Задание

- •3.10.2 Управление модулем жидкокристаллической индикации

- •3.10.3 Разработка функции управления ЖКИ с ожиданием готовности

- •3.10.4 Функция вывода строки символов

- •3.10.5 Разработка функции инициализации модуля ЖКИ

- •3.10.6 Разработка тестовой программы

- •3.10.7 Управление ЖКИ с опросом флага готовности

- •3.10.8 Программирование произвольных символов

- •3.11 Управление матричным светодиодным индикатором

- •3.11.1 Задание

- •3.11.2 Основные рекомендации

- •3.11.3 Алгоритм основной программы

- •3.11.4 Алгоритм процедуры обработки прерывания

- •3.11.5 Реализация движения строки

- •3.12 Управление матричным жидкокристаллическим дисплеем

- •3.12.1 Управление дисплеем на основе контроллера PCF8833

- •3.12.2 Построение простейших геометрических фигур

- •3.13 Измерение постоянного напряжения

- •3.13.1 Задание

- •3.13.2 Основные рекомендации

- •3.13.3 Алгоритм основной программы

- •3.13.4 Алгоритм процедуры обработки прерывания от АЦП

- •3.13.5 АЦП с циклическим опросом нескольких каналов

- •3.13.6 Автоматический выбор пределов измерения

- •3.14 Измерение параметров уровня переменного напряжения

- •3.14.1 Задание

- •3.14.2 Основные рекомендации

- •3.14.3 Алгоритм основной программы

- •3.14.4 Алгоритм процедуры обработки прерывания

- •3.15 Измерение ускорения с помощью трехосевого акселерометра

- •3.16 Измерение интервалов времени с помощью таймера

- •3.16.1 Задание

- •3.16.2 Общие рекомендации

- •3.16.3 Алгоритм основной программы

- •3.16.4 Алгоритм процедуры обработки прерывания

- •3.16.5 Повышение разрешающей способности путем усреднения

- •3.16.6 Введение поправок

- •3.17 Измерение частоты с помощью счетчика

- •3.17.1 Задание

- •3.17.2 Основные рекомендации

- •3.17.3 Алгоритм программы

- •3.17.4 Повышение точности измерений

- •3.18 Опрос цифрового датчика температуры. Интерфейс I2C

- •3.18.1 Задание

- •3.18.2 Общие рекомендации

- •3.18.3 Алгоритм программы

- •3.20 Обмен данными с электрически перепрограммируемым ПЗУ

- •3.20.1 Задание

- •3.20.2 Общие сведения о микросхемах EEPROM

- •3.20.3 Адресация в микросхемах EEPROM

- •3.20.4 Порядок чтения EEPROM

- •3.20.5 Порядок записи EEPROM

- •3.20.6 Разработка программы чтения EEPROM

- •3.20.7 Разработка функции записи блока данных в EEPROM

- •3.21 Интерфейс RS-232. Прием и передача простых команд

- •3.21.1 Задание

- •3.21.2 Алгоритм программы

- •3.21.3 Автоматическая настройка скорости

- •3.22.1 Задание

- •3.22.2 Основные рекомендации

- •3.22.3 Алгоритм программы

- •3.23 Интерфейс RS-232. Прием пакета переменной длины

- •3.23.1 Задание

- •3.23.2 Основы реализации

- •3.23.3 Алгоритм программы

- •3.24 Обмен данными с картой памяти Secure Digital

- •3.24.1 Задание

- •3.24.2 Общие сведения о карах FLASH-памяти SD/MMC

- •3.24.3 Команды SD/MMC

- •3.24.4 Процедура инициализации карты

- •3.24.5 Чтение и запись данных

- •3.24.6 Обработка ошибок

- •3.24.7 Комментарии к алгоритму и программе

- •Алфавитный указатель управляющих регистров

- •Список литературы

- •Содержание

4.Если необходимо, разрешить «пробуждение» микроконтроллера по запросу внешнего прерывания через регистр INTWAKE. Если режим отключения питания не используется, то настройка не производится.

5.Разрешить внешнее прерывание через регистры VICVectAddr0–15, VICVectCntl0–15 и VICIntEnable.

Процедура обработки прерывания должна содержать команду сброса флага путем записи единицы в соответствующий разряд регистра EXTINT.

1.13 Таймеры-счетчики

Таймеры-счетчики применяются для формирования и измерения интервалов времени или для подсчета числа внешних импульсов. Таймерсчетчик представляет собой программируемый суммирующий счетчик с возможностью выбора источника счетных импульсов. Микроконтроллер LPC2148 оснащен двумя абсолютно идентичными по функциональным возможностям 32-разрядными таймерами-счетчиками. Содержимое таймеровсчетчиков доступно для чтения и записи через регистры TC0 и TC1.

1.13.1 Режим таймера и схема совпадения

В зависимости от источника счетных импульсов различают режим таймера или счетчика. В режиме таймера ведется счет внутренних тактовых импульсов микроконтроллера  . При максимальной тактовой частоте 60 МГц разрядность позволяет продолжать счет без переполнения в течение

. При максимальной тактовой частоте 60 МГц разрядность позволяет продолжать счет без переполнения в течение  с. Формирования или измерение бóльших интервалов времени возможно с использованием 32-разрядных предварительных счетчи- ков-делителей c произвольным модулем счета в пределах разрядности (регистры TxPC). Каскадное соединение таймера и предварительного делителя практически бесконечно расширяет диапазон временных интервалов. При тактовой частоте 60 МГц переполнение произойдет почти через 10 тысяч лет.

с. Формирования или измерение бóльших интервалов времени возможно с использованием 32-разрядных предварительных счетчи- ков-делителей c произвольным модулем счета в пределах разрядности (регистры TxPC). Каскадное соединение таймера и предварительного делителя практически бесконечно расширяет диапазон временных интервалов. При тактовой частоте 60 МГц переполнение произойдет почти через 10 тысяч лет.

Временные интервалы формируются схемой совпадения, которая сравнивает содержимое таймера с пороговыми регистрами TxMR0–TxMR3. В момент равенства возможно выполнение следующих действий: сброс таймера в ноль, остановка таймера, запрос прерывания, изменение логического уровня на портовой линии. Четыре схемы совпадения позволяют выполнять разные действия при достижении таймером каждого из четырех пороговых значений.

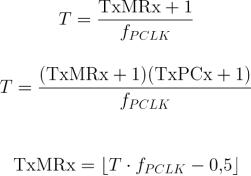

Длительность временного интервала при увеличении таймера от 0 до TxMRx без предварительно делителя ( ) составляет

) составляет

. |

(1.13.1) |

С предварительным делителем ( )

)

. (1.13.2)

Следовательно, значение порогового регистра, обеспечивающего задержку  (без предварительного делителя) определяется выражением

(без предварительного делителя) определяется выражением

. (1.13.3)

50

Здесь  — ближайшее к

— ближайшее к  целое, не превосходящее

целое, не превосходящее  , а

, а  — округленная до ближайшего целого величина

— округленная до ближайшего целого величина  .

.

1.13.2 Режим счетчика

В режиме счетчика подсчитываются импульсы напряжения, поступающие на портовые линии CAPx.0–CAPx.3. Максимальная частота на счетном входе составляет 30 МГц.

1.13.3 Схема захвата

Схема захвата позволяет «запомнить» в регистрах TxCR0–TxCR3 текущее состояние таймера-счетчика в момент появления сигнала на входных портовых линиях CAPx.0–CAPx.3. Захват состояния осуществляется с минимально возможной временной задержкой в один машинный цикл.

1.13.4 Управляющие регистры

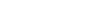

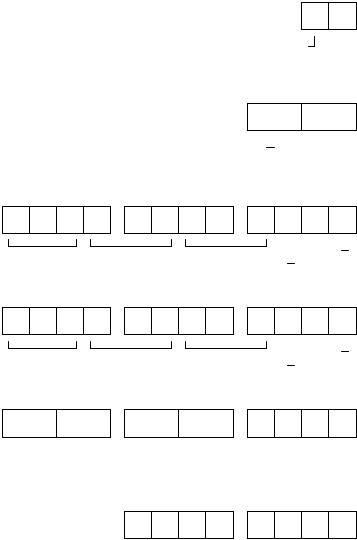

Схема регистров управления таймерами-счетчиками приведена на ри-

сунке 1.13.1.

Регистры TxIR (T0TCR, T1TCR) содержат флаги прерываний от схем совпадения и захвата. Установленный флаг должен сбрасываться в процедуре обработки прерывания путем записи единицы в соответствующий разряд. Запись нуля не оказывает влияния.

●Биты 0–3 (MR0I–MR3I) — флаги прерываний от выходов схемы совпадения MAT0–MAT3.

●Биты 4–7 (CR0I–CR3I) — флаги прерываний от выходов схемы захвата CAP0–CAP3. Регистры TxTCR (T0TCR, T1TCR) предназначены для запуска и сброса таймеров-счетчиков МК. Каждый из них содержит только два управляющих бита.

●Бит 0 (ENABLE). Установка единицы разрешает счет, сброс в ноль запрещает счет.

●Бит 1 (RESET). Установка единицы приводит к сбросу таймерасчетчика в ноль. Счет будет продолжен после сброса бита RESET в ноль.

Регистры TxCTCR (T0CTCR, T1CTCR) предназначены для настройки режимов работы встроенных таймеров-счетчиков.

●Биты 0–1 (MODE). Отвечают за выбор режима работы таймерасчетчика (таблица 1.13.1).

●Биты 2–3 (InputSelect). Отвечают за выбор линии CAPx.0–CAPx.3, которая служит счетным входом или входом захвата. Номер линии (0–3) совпадает с двоичным кодом в InputSelect (00–11). Значение этих битов не важно

врежиме таймера ( ), когда внешние сигналы не используются.

), когда внешние сигналы не используются.

Таблица 1.13.1 – Режимы работы таймеров-счетчиков МК LPC2148

MODE |

Режим таймера-счетчика |

00 |

Режим таймера. Инкремент по фронту внутреннего сигнала PCLK |

01 |

Режим счетчика. Инкремент по фронту внешнего сигнала CAP. |

10 |

Режим счетчика. Инкремент по срезу внешнего сигнала CAP. |

11 |

Режим счетчика. Инкремент по фронту и срезу сигнала CAP. |

51

TxTCR – настройка таймеров-счетчиков |

|

|

|

|||

15 |

11 |

8 |

7 |

2 |

1 |

0 |

|

|

T |

|

E |

|

S |

|

|

RE |

|

|

Сброс

EN ВКЛ

TxCTCR – настройка режима счета |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

15 |

|

|

|

|

|

|

|

|

|

|

|

|

|

8 |

7 |

|

|

|

|

|

|

|

4 |

|

3 |

|

2 |

1 |

0 |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Input |

MODE |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Select |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

TxMCR – настройка схемы совпадения |

|

|

|

|

|

|

Выбор входа |

|

|

|

Режим |

||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

15 |

12 |

11 |

10 |

|

9 |

|

8 |

7 |

|

6 |

|

5 |

4 |

|

3 |

|

2 |

1 |

0 |

||||||||||||||||||

|

|

|

|

S |

|

|

|

R |

|

|

|

I |

|

S |

|

R |

|

|

|

I |

|

|

S |

|

R |

|

|

|

I |

|

S |

|

|

R |

|

I |

|

|

|

|

3 |

|

|

3 |

|

|

3 |

R2 |

R2 |

|

|

2 |

|

1 |

R1 |

|

|

1 |

R0 |

0 |

0 |

||||||||||||||

|

|

R |

|

|

R |

|

|

|

R |

|

|

R |

|

R |

|

|

R |

|

R |

|

|

R |

|||||||||||||||

|

|

M |

|

|

M |

|

|

|

M |

|

|

M |

|

M |

|

M |

|

|

M |

|

|

M |

|

M |

|

|

M |

M |

|

|

M |

||||||

|

|

|

|

|

|

3 |

|

|

|

|

|

|

2 |

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

Сброс |

|

Прерывание |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TxCCR – настройка схемы захвата |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Остановка |

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

15 |

12 |

11 |

10 |

|

9 |

|

8 |

7 |

|

6 |

|

5 |

4 |

|

3 |

|

2 |

1 |

0 |

||||||||||||||||||

|

|

|

|

3 |

|

|

|

3 |

|

|

3 |

|

2 |

P2 |

|

|

2 |

|

|

1 |

P1 |

|

|

1 |

0 |

|

0 |

0 |

|||||||||

|

|

P |

|

P |

|

|

P |

|

P |

|

P |

|

P |

|

P |

|

AP |

P |

|

P |

|||||||||||||||||

|

|

A |

|

I |

A |

|

|

E |

A |

|

E |

A |

I |

A |

E |

A |

|

E |

A |

|

I |

A |

E |

A |

|

E |

CA |

|

E |

CA E |

|||||||

|

|

C |

|

C |

|

|

|

C |

|

|

C |

C |

C |

|

|

C |

|

C |

C |

|

|

C I |

|

||||||||||||||

|

|

|

|

|

|

|

F |

|

|

R |

|

|

|

F |

|

|

R |

|

|

|

|

F |

|

|

R |

|

|

F |

|

R |

|||||||

|

|

|

|

|

|

3 |

|

|

|

|

|

|

2 |

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

Срез |

|

Фронт |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TxEMR – настройка сигналов совпадения |

|

|

|

|

|

|

|

|

|

|

|

|

|

Прерывание |

|||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||

15 |

12 |

11 |

10 |

|

9 |

|

8 |

7 |

|

6 |

|

5 |

4 |

|

3 |

|

2 |

1 |

0 |

||||||||||||||||||

|

|

EMC3 |

EMC2 |

EMC1 |

EMC0 |

EM3 EM2 EM1 EM0 |

|||||||||||||||||||||||||||||||

|

|

Режим |

|

|

Режим |

Режим |

Режим |

|

|

|

|

Состояние |

|

|

|||||||||||||||||||||||

TxIR – флаги прерываний |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

15 |

|

|

|

|

|

|

|

|

|

|

|

|

|

8 |

7 |

|

6 |

|

5 |

4 |

|

3 |

|

2 |

1 |

0 |

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

I |

|

|

|

I |

|

|

I |

|

I |

|

|

|

I |

|

I |

|

|

I |

|

I |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

3 |

|

|

2 |

|

1 |

|

0 |

|

|

3 |

2 |

|

1 |

0 |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

R |

CR |

|

R |

R |

|

R |

|

R |

R |

|

R |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

C |

|

|

C |

|

|

C |

|

M |

|

|

M |

M |

|

|

M |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Флаги прерываний |

Флаги прерываний |

||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

от схемы захвата |

от схемы совпадения |

||||||||||||||||||||

Рисунок 1.13.1 – Схема регистров управления таймерами-счетчиками

Регистры TxPR (T0PR, T1PR) содержат предельные 32-разрядные значения предварительных счетчиков-делителей.

Регистры TxTC (T0TC, T1TC) содержат 32-х разрядный код, накопленный в таймере-счетчике.

Регистры TxPС (T0PС, T1PС) — содержимое 32-разрядных предварительных счетчиков-делителей. Таймер-счетчик увеличивается на единицу при достижении счетчиком-делителем TxPС предельного значения, заданного в TxPR. Если  , то в режиме таймера инкремент будет происходить каждый такт PCLK; если

, то в режиме таймера инкремент будет происходить каждый такт PCLK; если  , каждый второй такт и т. д. (1.13.2).

, каждый второй такт и т. д. (1.13.2).

Регистры TxMRx (T0MR0–T0MR3, T1MR0–T1MR3) — пороговые регистры, с которыми сравнивается содержимое таймеров счетчиков. При совпадении генерируются события, заданные регистром TxMCR.

Регистры TxMCR (T0MCR, T1MCR).

52

● Биты 0–11 (MR0I–MR3I, MR0R–MR3R, MR0S–MR3S) задают реак-

ции на совпадение таймера с каждым из пороговых регистров TxMR0– TxMR3 (см. таблицу 1.13.2).

Таблица 1.13.2 – Реакции на совпадение таймера-счетчика с TxMR0–TxMR3

Управляющие биты |

Назначение |

MR0I–MR3I |

Разрешить/запретить запрос прерывания |

MR0R–MR3R |

Разрешить/запретить сброс таймера-счетчика в ноль |

MR0S–MR3S |

Разрешить/запретить остановку счета |

Регистры TxCRx (T0CR0–T0CR3, T1CR0–T1CR3) содержат состоя-

ния таймеров счетчиков, захваченные при событии CAP0–CAP3. Регистры TxCCR (T0CCR, T1CCR) — настройка схемы захвата.

● Биты 0–3 (CAP0RE–CAP3RE, CAP0FE–CAP3FE, CAP0I–CAP3I) за-

дают событие, на которое реагирует каждая из четырех схем захвата, а также указывают на необходимость прерывания по захвату (таблица 1.13.3).

Таблица 1.13.3 – Реакции на сигнал захвата CAPx.0–CAPx.3

Управляющие биты |

Назначение |

CAP0RE–CAP3RE |

Захват по фронту сигнала CAPx.0–CAPx.3 |

CAP0FE–CAP3FE |

Захват по срезу сигнала CAPx.0–CAPx.3 |

CAP0I–CAP3I |

Запрос прерывания по событию захвата |

Регистры TxEMR (T0EMR, T1EMR).

●Биты 0–3 (EM0–3) отражают состояние логических уровней на вы-

ходах MATx.0–MATx.3

●Биты 4–5 (EMC0–EMC3). Биты управляют формированием внешнего сигнала по совпадению таймера-счетчика с каждым из пороговых регистров TxMR0–TxMR3 (в соответствии с таблицей 1.13.4).

Таблица 1.13.4 – Способы формирования внешнего сигнала совпадения

ECx |

Реакция на совпадение |

|

00 |

Не изменять внешний сигнал MATx.0 |

|

01 |

Установить на выходе MATx.0 |

сигнал «логический ноль» |

10 |

Установить на выходе MATx.0 |

сигнал «логическая единица» |

11 |

Инвертировать сигнал на выходе MATx.0 |

|

1.13.5 Формирование интервалов времени через систему прерываний

Чаще всего формирование временного интервала осуществляется с помощью процедуры обработки прерывания, вызываемой схемой совпадения. При этом рекомендуется придерживаться следующего порядка настройки аппаратуры микроконтроллера.

1. Настроить работу схемы совпадения через регистр TxMCR. Обычно требуется включить сброс счетчика и запрос прерывания по совпадению с одним из пороговых регистров, например, TxMR0. Для этого достаточно установить единицы в битах MR0R, MR0I регистра TxMСR. Запрос прерывания необходимо разрешить, даже если предполагается программный опрос флага.

53