Экзамен,чтоб тебя

.pdf10. BIOS. Структура и предназначение

BIOS (англ. basic input/output system — «базовая система ввода-вывода») — реализованная в виде микропрограмм часть системного программного обеспечения, которая предназначается для обеспечения операционной системы API (/* Windows API (англ. application programming interfaces) — общее наименование целого набора базовых функций интерфейсов программирования приложений операционных систем семейств Windows и Windows NT; является самым прямым способом взаимодействия приложений с Windows*/) доступа к аппаратуре компьютера и подключенным к нему устройствам.

В персональных IBM PC-совместимых компьютерах, использующих микроархитектуру x86, BIOS представляет собой набор записанного в микросхему EEPROM (ПЗУ) персонального компьютера микропрограмм (образующих системное программное обеспечение), обеспечивающих начальную загрузку компьютера и последующий запуск операционной системы.

Базовая система ввода-вывода – это комплекс программ, состоящих из следующих частей: 1.Дополнительные микрокоды

2.POST состоит из секций, каждая из которых отвечает за определенное состояние компьютера -Базовое тестирование -Тестирование системного контроллера, который обеспечивает взаимодействие ЦП и ОЗУ.

-Тестирование и инициализация системного контроллера, проверка видео (64 кб). -тестирование ОЗУ

-тест южного моста

3.Комплекс программ обеспечивающий взаимодействие ЦП со всеми устройствами компьютера ( все типы контроллеров и УУ)

4.CMOS – базовые программы – часы, календарь – батарейка 128 байт

Назначение BIOS материнской платы

Инициализация и проверка работоспособности аппаратуры

Большую часть BIOS материнской платы составляют микропрограммы инициализации контроллеров на материнской плате, а также подключённых к ней устройств, которые в свою очередь могут иметь управляющие контроллеры с собственными BIOS.

Сразу после включения питания компьютера, во время начальной загрузки компьютера, при помощи программ записанных в BIOS, происходит самопроверка аппаратного обеспечения компьютера — POST. В случае сбоя во время прохождения POST, BIOS может выдать информацию, позволяющую выявить причину сбоя. Кроме вывода сообщения на монитор, используется звуковой сигнал, воспроизводимый при помощи встроенного динамика.

Входе POST, BIOS проверяет работоспособность контроллеров на материнской плате, задаёт низкоуровневые параметры их работы (например, частоту шины и параметры центрального микропроцессора, контроллера оперативной памяти,

контроллеров шин FSB, AGP, PCI, USB).

Загрузка операционной системы

Если POST удался, BIOS ищет на доступных носителях загрузчик операционной системы и передаёт управление операционной системе. Операционная система по ходу работы может изменять большинство настроек, изначально заданных в BIOS.

Внекоторых реализациях BIOS позволяет производить загрузку операционной системы через интерфейсы, изначально для этого не предназначенные (USB и IEEE 1394) а также производить загрузку по сети (применяется, например, в т. н. «тонких клиентах»).

Утилиты, доступные без загрузки ОС

Старые IBM PC/XT, которые не имели полноценной операционной системы, либо её загрузка не была необходимой пользователю, вызывали встроенный интерпретатор языка Бейсик. В некоторых BIOS’ах реализуется дополнительная функциональность:

Воспроизведение аудио-CD или DVD-дисков. Обновление самого BIOS’а (обычно с дискет). Простейший драйвер

IBM-совместимые компьютеры изначально конструировались как предельно расширяемые. Поэтому работа с дисками и экраном, в более ранних системах выполнявшаяся через порты ввода-вывода и блоки памяти, были реализованы через функции BIOS. Заодно BIOS содержит несколько ценных интерфейсов, упрощающих программирование — такие, как работа с экраном в телетайпном режиме или сканирование клавиатуры — что также обусловливает расшифровку её названия: basic — «базовая».

Современные ОС, такие, как Windows и Linux, имеют свои драйверы, не использующие BIOS. Однако функциями BIOS широко пользуются простейшие ОС (такие, как DOS) — а также все ОС в момент загрузки и в «аварийных» режимах.

С развитием компьютерных систем в BIOS продолжали использоваться устаревшие технологии: прежде всего «реальный режим» работы процессора x86; для принципиальной замены BIOS рядом производителей вычислительных систем (Unified EFI Forum, UEFI) предложена и внедряется технология EFI.

AMI, Phoenix, Award

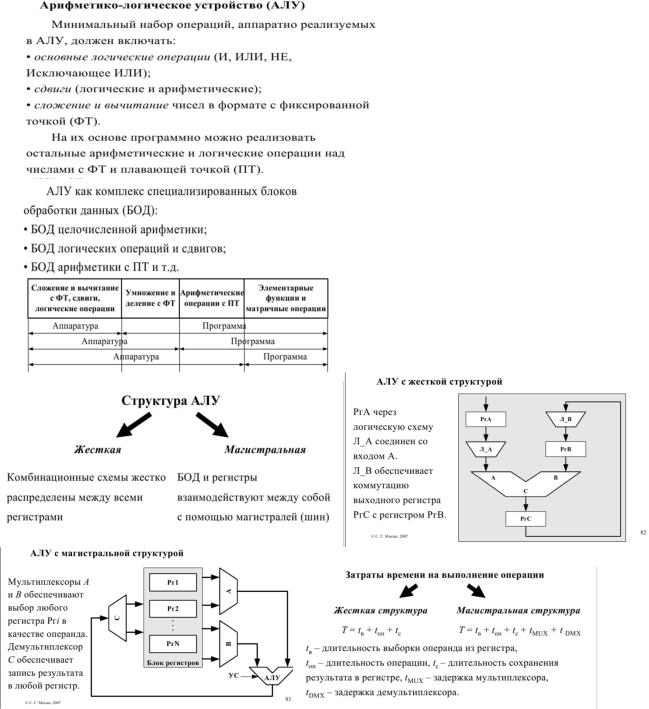

11.Назначение, принципы построения и характеристики арифметическо-логических устройств (АЛУ).

ри метико- о и еское стройст о (англ. arithmetic and logic unit, ALU) — блок процессора, который под управлением устройства управления (УУ) служит для выполнения арифметических и логических преобразований (начиная от элементарных) над данными, представляемыми в виде машинных слов, называемыми в этом случае операндами.

Одноразрядное двоичное бинарное (двухоперандное) АЛУ с бинарным (двухразрядным) выходом может выполнять до двоичных бинарных (двухоперандных) функций (операций) с бинарным (двухразрядным) выходом.

Одноразрядное троичное бинарное (двухоперандное) АЛУ с унарным (одноразрядным) выходом (полуАЛУ) может выполнять до троичных бинарных (двухоперандных) функций (операций) с унарным (одноразрядным) выходом. Одноразрядное троичное бинарное (двухоперандное) АЛУ с бинарным (двухразрядным) выходом может выполнять до троичных бинарных (двухоперандных) функций (операций) с бинарным (двухразрядным) выходом. Арифметико-логическое устройство в зависимости от выполнения функций можно разделить на две части:

-микропрограммное устройство (устройство управления), задающее последовательность микрокоманд (команд);

-операционное устройство (АЛУ), в котором реализуется заданная последовательность микрокоманд (команд). Операционные устройства можно классифицировать по виду обрабатываемой информации, по способу её обработки и по логической структуре. Более подробная классификация указана на рис.3.

Такая сложная логическая структура АЛУ может характеризоваться количеством отличающихся друг от друга микроопераций, которые необходимы для выполнения всего комплекса задач, поставленных перед арифметикологическим устройством. На входе каждого регистра собраны соответствующие логические схемы, обеспечивающие такие связи между регистрами, что позволяет реализовать заданные микрооперации. Выполнение операций над словами сводится к выполнению определённых микроопераций, которые сводятся в свою очередь … управляют передачей слов в АЛУ и действиями по преобразованию слов. Порядок выполнения микрокоманд определяется алгоритмом выполнения операций. То есть, связи между регистрами АЛУ и их функциями зависят в основном от принятой методики выполнения логических операций, в том числе арифметических или специальной арифметики.

Операции в АЛУ Все выполняемые в АЛУ операции являются логическими операциями (функциями), которые можно разделить на следующие группы:

-операции двоичной арифметики для чисел с фиксированной точкой;

-операции двоичной (или шестнадцатеричной) арифметики для чисел с плавающей точкой;

-операции десятичной арифметики;

-операции индексной арифметики (при модификации адресов команд);

-операции специальной арифметики;

-операции над логическими кодами (логические операции);

-операции над алфавитно-цифровыми полями.

Современные ЭВМ общего назначения обычно реализуют операции всех приведённых выше групп, а малые и микроЭВМ, микропроцессоры и специализированные ЭВМ часто не имеют аппаратуры арифметики чисел с плавающей точкой, десятичной арифметики и операций над алфавитно-цифровыми полями. В этом случае эти операции выполняются специальными подпрограммами. К арифметическим операциям относятся сложение, вычитание, вычитание модулей («короткие операции») и умножение и деление («длинные операции»). Группу логических операций составляют операции дизъюнкция (логическое ИЛИ) и конъюнкция (логическое И) над многоразрядными двоичными словами, сравнение кодов на равенство. Специальные арифметические операции включают в себя нормализацию, арифметический сдвиг (сдвигаются только цифровые разряды, знаковый разряд остаётся на месте), логический сдвиг (знаковый разряд сдвигается вместе с цифровыми разрядами). Обширна группа операций редактирования алфавитно-цифровой информации. Каждая операция в АЛУ является логической функцией или последовательностью логических функций описываемых двоичной логикой для двоичных ЭВМ, троичной логикой для троичных ЭВМ, четверичной логикой для четверичных ЭВМ, …, десятичной логикой для десятичных ЭВМ и т. д… Классификация АЛУ

По способу действия над операндами АЛУ делятся на последовательные и параллельные. В последовательных АЛУ операнды представляются в последовательном коде, а операции производятся последовательно во времени над их отдельными разрядами. В параллельных АЛУ операнды представляются параллельным кодом и операции совершаются параллельно во времени над всеми разрядами операндов.

По способу представления чисел различают АЛУ:

-для чисел с фиксированной точкой;

-для чисел с плавающей точкой;

-для десятичных чисел.

По характеру использования элементов и узлов АЛУ делятся на блочные и многофункциональные. В блочном АЛУ операции над числами с фиксированной и плавающей точкой, десятичными числами и алфавитно-цифровыми полями выполняются в отдельных блоках, при этом повышается скорость работы, так как блоки могут параллельно выполнять соответствующие операции, но значительно возрастают затраты оборудования. В многофункциональных АЛУ операции для всех форм представления чисел выполняются одними и теми же схемами, которые коммутируются нужным образом в зависимости от требуемого режима работы.

По своим функциям АЛУ является операционным блоком, выполняющим микрооперации, обеспечивающие приём из других устройств (например, памяти) операндов, их преобразование и выдачу результатов преобразования в другие устройства. Арифметико-логическое устройство управляется управляющим блоком, генерирующим управляющие сигналы, инициирующие выполнение в АЛУ определённых микроопераций. Генерируемая управляющим блоком последовательность сигналов определяется кодом операции команды и оповещающими сигналами.

Минимальный набор операций аппратано реализуемых АЛУ должен включать 1) основные логические операции (и, или, ксор) 2) сдвиги (логические и арифметические) 3) сложение и вычитание чисел в форме с фиксированной точкой.

12.Дисковые массивы и уровни RAID

Так же как и для оперативной памяти для дисковой памяти важнейшими характеристиками являются скорость обмена данными и их сохранность. Ввиду большого объема дисковой памяти потеря хранящихся в ней данных из-за сбоя или отказа оборудования является более серьезной проблемой, чем потеря информации оперативной памяти, поэтому к дисковой памяти предъявляются более высокие требования по отказоустойчивости. Одним из способов повышения отказоустойчивости дисковой памяти является организация избыточного дискового массива, позволяющего восстановить исходные данные при сбоях и отказах. Одна из технологий повышения отказоустойчивости получила название RAID (избыточный массив недорогих дисков). Технология RAID базируется на трех основных методах записи и защиты информации:

1.Распределение последовательности сегментов данных по дискам с определенной циклической очередностью.

2.Зеркальное отображение дисков

3.Вычисление контрольных сумм

Поочередное размещение позволяет создавать тома памяти большого объема и ускорять выполнение операций записи и чтения данных так как предполагает запись первого сегмента данных на первый диск, второго на второй и т.д. В этом случает производительность массива повышается, поскольку процессор или контроллер ввода/вывода начинает записывать очередной сегмент данных на следующий диск до того, как закончил запись предыдущего сегмента. Зеркальное отображение накопителей и вычисление контрольных сумм приводит к появлению избыточной информации, обеспечивающей восстановление утерянных из-за сбоя или отказа оборудования данных.

Различные схемы реализации дисковых массивов получили названия – уровней RAID.

1. RAID система ро ня 0 но ь

Данная система не является отказоустойчивой и довольно часто такую организацию дисковой памяти вообще не относят к RAID массивам. В системах RAID-0 осуществляет только поочередное размещение сегментов данных на дисках, они применяются когда повышенная надежность хранения данных не имеет очень большого значения, поскольку выход из строя одного диска приводит к потере всей хранящейся в массиве информации. Такая организация дисковой памяти используется например для задач редактирования изображений и разного рода приложений, требующих большой емкости массива и высокой скорости выполнения операций ввода/вывода.

2. Отказоустойчивость системы дисковой памяти реализуется по технологии RAID-1, которая представляет собой зеркальное отображение дисков, т.е. данные записываются на 2 или большее число дисков одновременно при этом образуется более одной копии данных, а уровень информационной избыточности при записи на 2 диска уже составляет 100%. При сбое или выходе из строя одного диска данные считываются с его зеркального отображения. Недостатком RAID-1 является высокая избыточность оборудования и возможные проблемы с заменой вышедшего из строя диска, если функциональность RAID -1 реализуется программно, а не с помощью специального контроллера.

3. Технология RAID-2, коммерческие реализации которой практически отсутствует, предусмотрены защита данных с помощью корректирующих кодов Хэймонда. Записываемые данные распределяются по нескольким дискам, а контрольные разряды записываются на один или несколько, предназначенных специально для этого дисков. Недостатком RAID-2 является большая доля таких дисков в массиве, что делает реализацию данной архитектуры довольно дорогостоящей. Кроме того контроллеры современных дисковых устройств часто уже имеют встроенные схемы коррекции ошибок.

4. RAID-3. данные распределяются по информационным дискам и для совокупности сегментов данных, расположенных в одних и тех же секторах разных физических дисках, определяется контрольная сумма или код честности, которые записываются на отдельный диск. Массивы RAID-3 обеспечивают высокую скорость передачи данных при выполнении операций чтения/записи и по сравнению с массивами RAID-2 им требуется меньшее количество дисков для хранения контрольных сумм. Недостатком этого уровня является его достаточная сложность и возможность реализации только аппаратным способом.

5.Масси RAID-4 повышает производительность передачи небольших объемов данных за счет параллелизма, давая возможность выполнять более одного обращения по вводу-выводу к группе в единицу времени. Логические блоки информации в RAID-4 не распределяются между отдельными дисками, а каждый индивидуальный блок попадает на отдельный диск. Это дает возможность выполнять несколько разных запросов на чтение одновременно.

6.В масси ах RAID-5 как и в RAID-4 на дисках поочередно размещаются большие блоки данных, но в отличие от системы предыдущего уровня, контрольная информация распределяется по всем дискам массива. Это небольшое изменение оказывает огромное влияние на производительность записи небольших массивов информации, если операции записи могут быть спланированы так, чтобы обращаться за данными и соответствующими им блоками четности к разным дискам. Появляется возможность параллельного выполнения n/2 записей, где n – число дисков в группе. Данная организация имеет одинаково высокую производительность при записи и при считывании как небольших, так и больших объемов информации.

Следующие уровни RAID разработаны с целью повышения надежности хранения данных. Их реализация обходится довольно дорого, основывается, как правило на предыдущих уровнях RAID или является фирменным решением компании разработчика.

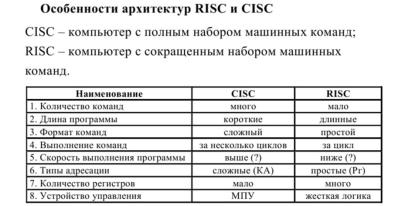

13. Классификация процессоров (CISC и RISC). Их краткая характеристика

CISC (англ. сomplex instruction set computing, или англ. complex instruction set computer — компьютер с полным набором команд) — концепция проектирования процессоров, которая характеризуется следующим набором свойств:

-нефиксированное значение длины команды;

-арифметические действия кодируются в одной команде;

-небольшое число регистров, каждый из которых выполняет строго определённую функцию.

Недостатки CISC архитектуры:

-высокая стоимость аппаратной части;

-сложности с распараллеливанием вычислений.

RISC (англ. Restricted (reduced) instruction set computer — компьютер с упрощённым набором команд) — архитектура процессора, в которой быстродействие увеличивается за счёт упрощения команд, чтобы их декодирование было проще, а время выполнения — короче. Первые RISC-процессоры даже не имели команд умножения и деления. Это также облегчает повышение тактовой частоты и делает более эффективной суперскалярность (распараллеливание команд между несколькими исполнительными блоками).

Концепция RISC сводится к следующим положениям:

1.Выполнение всех команд за один цикл (75%).

2.Стандартная однословная длина всех команд равная естественной длине слова и ширине шины данных и допускающая унифицированную обработку всех команд.

3.Малое количество команд (лимит 2*(7)), малое количество форматов команд (не более 4) малое число способов адресации (не более 4)

4.Доступ памяти только по средствам команд чтения и записи

5.Все команды,за исключением команды чтения и записи используют внутрипроцессорные межрегистровые пересылки

6.Устройство управления с жесткой логикой

7.Регистров общего назначения может быть более 500,не менее 32

14. Простейшая организация конвейера и оценка его производительности. Привести пример.

Что такое конвейерная обработка

Разработчики архитектуры компьютеров издавна прибегали к методам проектирования, известным под общим названием "совмещение операций", при котором аппаратура компьютера в любой момент времени выполняет одновременно более одной базовой операции. Этот общий метод включает два понятия: параллелизм и конвейеризацию. Хотя у них много общего и их зачастую трудно различать на практике, эти термины отражают два совершенно различных подхода. При параллелизме совмещение операций достигается путем воспроизведения в нескольких копиях аппаратной структуры. Высокая производительность достигается за счет одновременной работы всех элементов структур, осуществляющих решение различных частей задачи.

Конвейеризация (или конвейерная обработка) в общем случае основана на разделении подлежащей исполнению функции на более мелкие части, называемые ступенями, и выделении для каждой из них отдельного блока аппаратуры. Так обработку любой машинной команды можно разделить на несколько этапов (несколько ступеней), организовав передачу данных от одного этапа к следующему. При этом конвейерную обработку можно использовать для совмещения этапов выполнения разных команд. Производительность при этом возрастает благодаря тому, что одновременно на различных ступенях конвейера выполняются несколько команд. Конвейерная обработка такого рода широко применяется во всех современных быстродействующих процессорах.

Простейшая организация конвейера и оценка его производительности

Для иллюстрации основных принципов построения процессоров мы будем использовать простейшую архитектуру, содержащую 32 целочисленных регистра общего назначения (R0,...,R31), 32 регистра плавающей точки (F0,...,F31) и счетчик команд PC. Будем считать, что набор команд нашего процессора включает типичные арифметические и логические операции, операции с плавающей точкой, операции пересылки данных, операции управления потоком команд и системные операции. В арифметических командах используется трехадресный формат, типичный для RISCпроцессоров, а для обращения к памяти используются операции загрузки и записи содержимого регистров в память. Выполнение типичной команды можно разделить на следующие этапы:

выборка команды - IF (по адресу, заданному счетчиком команд, из памяти извлекается команда);

декодирование команды / выборка операндов из регистров - ID;

выполнение операции / вычисление эффективного адреса памяти - EX;

обращение к памяти - MEM;

запоминание результата - WB.

На рис. 5.1 представлена схема простейшего процессора, выполняющего указанные выше этапы выполнения команд без совмещения. Чтобы конвейеризовать эту схему, мы можем просто разбить выполнение команд на указанные выше этапы, отведя для выполнения каждого этапа один такт синхронизации, и начинать в каждом такте выполнение новой команды. Естественно, для хранения промежуточных результатов каждого этапа необходимо использовать регистровые станции. На рис. 5.2 показана схема процессора с промежуточными регистровыми станциями, которые обеспечивают передачу данных и управляющих сигналов с одной ступени конвейера на следующую. Хотя общее время выполнения одной команды в таком конвейере будет составлять пять тактов, в каждом такте аппаратура будет выполнять в совмещенном режиме пять различных команд.

Работу конвейера можно условно представить в виде сдвинутых во времени схем процессора (рис. 5.3). Этот рисунок хорошо отражает совмещение во времени выполнения различных этапов команд. Однако чаще для представления работы конвейера используются временные диаграммы (рис. 5.4), на которых обычно изображаются выполняемые команды, номера тактов и этапы выполнения команд.

Конвейеризация увеличивает пропускную способность процессора (количество команд, завершающихся в единицу времени), но она не сокращает время выполнения отдельной команды. В действительности, она даже несколько увеличивает время выполнения каждой команды из-за накладных расходов, связанных с управлением регистровыми станциями. Однако увеличение пропускной способности означает, что программа будет выполняться быстрее по сравнению с простой неконвейерной схемой.

Тот факт, что время выполнения каждой команды в конвейере не уменьшается, накладывает некоторые ограничения на практическую длину конвейера. Кроме ограничений, связанных с задержкой конвейера, имеются также ограничения, возникающие в результате несбалансированности задержки на каждой его ступени и из-за накладных расходов на конвейеризацию. Частота синхронизации не может быть выше, а, следовательно, такт синхронизации не может быть меньше, чем время, необходимое для работы наиболее медленной ступени конвейера. Накладные расходы на организацию конвейера возникают из-за задержки сигналов в конвейерных регистрах (защелках) и из-за перекосов сигналов синхронизации. Конвейерные регистры к длительности такта добавляют время установки и задержку распространения сигналов. В предельном случае длительность такта можно уменьшить до суммы накладных расходов и перекоса сигналов синхронизации, однако при этом в такте не останется времени для выполнения полезной работы по преобразованию информации.

В качестве примера рассмотрим неконвейерную машину с пятью этапами выполнения операций, которые имеют длительность 50, 50, 60, 50 и 50 нс соответственно (рис. 5.5). Пусть накладные расходы на организацию конвейерной обработки составляют 5 нс. Тогда среднее время выполнения команды в неконвейерной машине будет равно 260 нс. Если же используется конвейерная организация, длительность такта будет равна длительности самого медленного этапа обработки плюс накладные расходы, т.е. 65 нс. Это время соответствует среднему времени выполнения команды в конвейере. Таким образом, ускорение, полученное в результате конвейеризации, будет равно:

Среднее время выполнения команды в неконвейерном режиме = 260 Среднее время выполнения команды в неконвейерном режиме 65 = 4

Конвейеризация эффективна только тогда, когда загрузка конвейера близка к полной, а скорость подачи новых команд и операндов соответствует максимальной производительности конвейера. Если произойдет задержка, то параллельно будет выполняться меньше операций и суммарная производительность снизится. Такие задержки могут возникать в результате возникновения конфликтных ситуаций. В следующих разделах будут рассмотрены различные типы конфликтов, возникающие при выполнении команд в конвейере, и способы их разрешения.

Рис. 5.3. Представление о работе конвейера

Номер команды |

|

|

Номер |

|

||||

|

|

такта |

|

|

||||

|

|

|

|

|

||||

|

1 |

2 |

|

|

3 |

4 5 6 7 8 9 |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

MEM WB |

Команда i |

|

IF |

|

ID |

|

|

EX |

|

|

|

|

|

|

|

|

|

|

EX MEM WB

Команда i+1 |

IF ID |

ID EX MEM WB

Команда i+2 |

IF |

IF ID EX MEM WB

Команда i+3

Команда i+4

IF ID EX MEM WB

IF ID EX MEM WB

Рис. 5.4. Диаграмма работы простейшего конвейера

Рис. 5.5. Эффект конвейеризации при выполнении 3-х команд - четырехкратное ускорение

При реализации конвейерной обработки возникают ситуации, которые препятствуют выполнению очередной команды из потока команд в предназначенном для нее такте. Такие ситуации называются конфликтами. Конфликты снижают реальную производительность конвейера, которая могла бы быть достигнута в идеальном случае. Существуют три класса конфликтов:

4.Структурные конфликты, которые возникают из-за конфликтов по ресурсам, когда аппаратные средства не могут поддерживать все возможные комбинации команд в режиме одновременного выполнения с совмещением.

5.Конфликты по данным, возникающие в случае, когда выполнение одной команды зависит от результата выполнения предыдущей команды.

6.Конфликты по управлению, которые возникают при конвейеризации команд переходов и других команд, которые изменяют значение счетчика команд.

Конфликты в конвейере приводят к необходимости приостановки выполнения команд (pipeline stall). Обычно в простейших конвейерах, если приостанавливается какая-либо команда, то все следующие за ней команды также приостанавливаются. Команды, предшествующие приостановленной, могут продолжать выполняться, но во время приостановки не выбирается ни одна новая команда.

15. Классификация конфликтов по данным

Конфликт возникает везде, где имеет место зависимость между командами, и они расположены по отношению друг к другу достаточно близко так, что совмещение операций, происходящее при конвейеризации, может привести к изменению порядка обращения к операндам. В нашем примере был проиллюстрирован конфликт, происходящий с регистровыми операндами, но для пары команд возможно появление зависимостей при записи или чтении одной и той же ячейки памяти. Однако, если все обращения к памяти выполняются в строгом порядке, то появление такого типа конфликтов предотвращается.

Известны три возможных конфликта по данным в зависимости от порядка операций чтения и записи. Рассмотрим две команды i и j, при этом i предшествует j. Возможны следующие конфликты:

RAW (чтение после записи) - j пытается прочитать операнд-источник данных прежде, чем i туда запишет. Таким образом, j может некорректно получить старое значение. Это наиболее общий тип конфликтов, способ их преодоления с помощью механизма "обходов" рассмотрен ранее.

WAR (запись после чтения) - j пытается записать результат в приемник прежде, чем он считывается оттуда командой i, так что i может некорректно получить новое значение. Этот тип конфликтов как правило не возникает в системах с централизованным управлением потоком команд, обеспечивающих выполнение команд в порядке их поступления, так как последующая запись всегда выполняется позже, чем предшествующее считывание. Особенно часто конфликты такого рода могут возникать в системах, допускающих выполнение команд не в порядке их расположения в программном коде.

WAW (запись после записи) - j пытается записать операнд прежде, чем будет записан результат команды i, т.е. записи заканчиваются в неверном порядке, оставляя в приемнике значение, записанное командой i, а не j. Этот тип конфликтов присутствует только в конвейерах, которые выполняют запись со многих ступеней (или позволяют команде выполняться даже в случае, когда предыдущая приостановлена).

16. Организация регистров

Регистры процессора представляют память самого верхнего уровня. Их разделяют по функциям на программнодоступные( минимизирую число обращений к медленной оперативной памяти и обеспечивают хранение промежуточных результатов) и управления и состояния(используют для управления функционированием процессора(исп в программах ОС)).