- •Рецензент:

- •Т.Х.Иванов

- •Содержание

- •Предисловие

- •Лабораторная работа 1 Логические элементы

- •1. Теоретические основы лабораторной работы

- •1.1 Основы булевой алгебры

- •1.2 Назначение и технические характеристики универсального лабораторного стенда

- •2. Задание на лабораторную работу

- •3. Контрольные вопросы

- •Лабораторная работа 2 Проектирование комбинационных цифровых устройств в заданном базисе логических элементов

- •1. Теоретические основы лабораторной работы

- •1.1 Формы представления алгоритмов функционирования кцу

- •Алгоритм перехода от таблицы истинности логической функции к ее записи в виде сднф

- •1.3 Алгоритм перехода от таблицы истинности логической функции к ее записи в виде скнф

- •1.4 Минимизация логических функций

- •1.5 Алгоритм минимизации логических функций, заданных в сднф при помощи карт Карно

- •1.6 Минимизация частично определенных и инверсных логических функций

- •1.7 Преобразование минимальных форм логических функций к виду, реализуемому лэ заданного функционально полного набора

- •1.8 Минимальные формы в монофункциональных базисах

- •1.9 Проектирование схемы кцу в заданном базисе лэ

- •1.10 Проектирование многовыходных кцу

- •2. Задание на лабораторную работу

- •3. Содержание отчета

- •4. Контрольные вопросы

- •Лабораторная работа 3 Проектирование и исследование дешифраторов

- •1. Теоретические основы лабораторной работы

- •1.1 Линейные дешифраторы

- •1.2 Пирамидальные дешифраторы

- •1.3 Особенности проектирования неполных дешифраторов

- •1.4. Применение дешифратора в качестве универсального логического элемента

- •2. Задание на лабораторную работу

- •3. Содержание отчета по лабораторной работе

- •4. Контрольные вопросы

- •Лабораторная работа 4 Двоичные сумматоры

- •1. Теоретические основы лабораторной работы

- •1.1 Правила выполнения арифметических операций

- •1.2 Двоичные сумматоры

- •1.3 Двоичные вычитатели

- •1 .4 Двоичные сумматоры - вычитатели

- •2. Задание на лабораторную работу

- •3. Содержание отчета

- •4. Контрольные вопросы

- •Лабораторная работа 5 Цифровые компараторы

- •1. Теоретические основы лабораторной работы

- •2. Задание на лабораторную работу

- •3. Контрольные вопросы

- •Лабораторная работа 6 Устройства контроля работоспособности цу

- •1. Теоретические основы лабораторной работы

- •1.1 Контроль по модулю 2 (контроль по четности/нечетности)

- •1.2 Контроль дублированием и троированием

- •2. Задание на лабораторную работу

- •3. Контрольные вопросы

- •Лабораторная работа 7 Мультиплексоры и демультиплексоры

- •1. Теоретические основы лабораторной работы

- •1.1 Мультиплексоры

- •1.2. Демультиплексоры

- •1.3 Применение мультиплексоров и демультиплексоров

- •2. Задание на лабораторную работу

- •3. Контрольные вопросы

- •Лабораторная работа 8 Синтез и исследование триггеров

- •1. Теоретические основы лабораторной работы

- •1.1 Цифровые устройства последовательностного типа

- •1.2 Триггеры

- •1.3 Схемотехника триггеров

- •2. Задание на лабораторную работу

- •3. Содержание отчета

- •4. Контрольные вопросы

- •Лабораторная работа 9 Регистры

- •1. Теоретические основы лабораторной работы

- •1.1 Параллельный регистр

- •1.2 Последовательный регистр

- •2. Задание на лабораторную работу

- •4. Контрольные вопросы

- •Приложение

- •Лабораторная работа 10 Цифровые счетчики импульсов

- •1. Теоретические основы лабораторной работы

- •1.1 Суммирующие двоичные счетчики

- •1.2 Вычитающие двоичные счетчики

- •1.3. Реверсивные двоичные счетчики

- •1.4 Счетчики с произвольным значением модуля счета

- •2. Домашнее задание

- •3. Задание на лабораторную работу

- •4. Содержание отчета

- •5. Контрольные вопросы

- •Приложение

- •Принятые сокращения

- •Литература

- •Основы цифровой техники

Лабораторная работа 3 Проектирование и исследование дешифраторов

Цель работы:изучение принципов проектирования дешифраторов в заданном базисе логических элементов, а также исследование функционирования спроектированных дешифраторов и интегральных схем дешифраторов.

1. Теоретические основы лабораторной работы

Дешифратором (декодером)называется цифровое устройство комбинационного типа, осуществляющее преобразование n-разрядного двоичного кода в m-разрядный унитарный код.

У нитарный

код (код «1 из m»)может быть прямым

(одна «1» в некотором разрядеm-разрядного

двоичного кода иm-1 нулей)

или обратным (один «0» иm-1

единиц).

нитарный

код (код «1 из m»)может быть прямым

(одна «1» в некотором разрядеm-разрядного

двоичного кода иm-1 нулей)

или обратным (один «0» иm-1

единиц).

Примеры записи унитарного кода для m=8:

прямого – 0001 0000, 0100 0000, ...

обратного – 1101 1111, 0111 1111, ...

Схема дешифратора имеет nвходов, на которые поступают соответствующие разряды двоичного кодахn, xn-1, …, x2, x1иmвыходов, на которых формируются разряды унитарного кодауm-1, ...,у1,у0. При этом дешифратор реализуетmфункций вида:

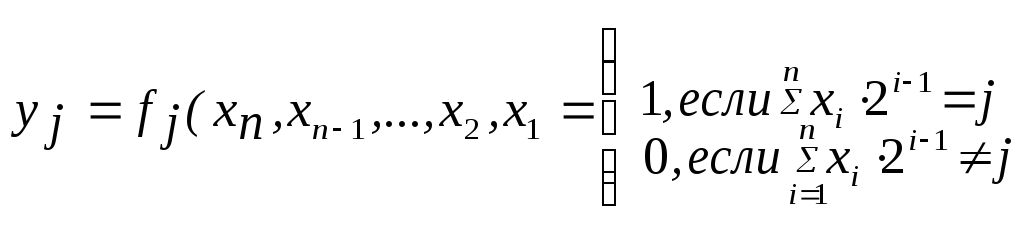

(1)

(1)

Функции (1) соответствуют преобразованию двоичного кода в прямой унитарный код и могут быть записаны в виде:

![]()

(2)![]() (2)

(2)

![]()

![]()

![]()

Такой системе уравнений соответствует таблица истинности (табл.1).

И

Таблица 1 xnxn-1 ...x3x2x1 y0y1y2ym-1

ym 0

0 ... 0 0 0 0

0 ... 0 0 1 0

0 ... 0 1 0 ……………………….

1

1 ... 1 1 0 1

1 ... 1 1 1 1

0 0 ... 0 0 0

1 0 ... 0 0 0

0 1 ... 0 0 ………………………

0

0 0 ... 1 0 0

0 0 ... 0 1

Дешифраторы входят в состав практически всех серий цифровых ИС и отличаются:

числом выходов (полные и неполные дешифраторы);

видом преобразования - в прямой (прямые выходы) или обратный (инверсные выходы) унитарный код;

наличием или отсутствием стробирующего (управляющего) входа. Сигнал на этом входе разрешает или запрещает выполнение микросхемой операции дешифрирования;

быстродействием, которое характеризуется средним временем задержки распространения сигнала от входа до выхода tзд.р.ср;

энергопотреблением; т.е. мощностью, потребляемой от источника питания.

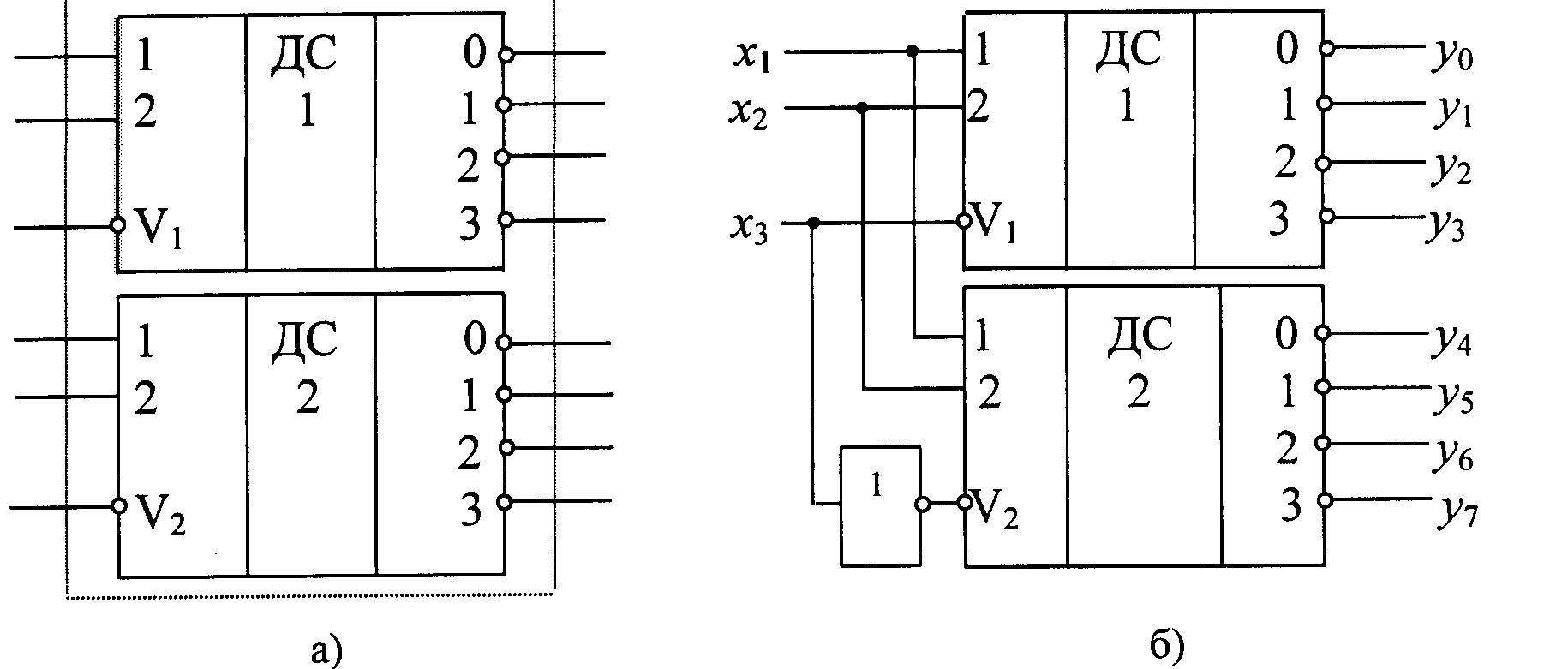

Например,

ИС сдвоенного дешифратора К 530 ИД-14

(рис.1, а) (в одном корпусе два автономных

дешифратора «2-4», выходы инверсные)

имеет по одному стробирующему входу

![]() и

и![]() в

каждом дешифраторе.

в

каждом дешифраторе.

При объединении (каскадировании) информационных и стробирующих входов, как это показано на рис.1, б, получают дешифратор 3-х разрядного двоичного кода. Входные сигналы дешифрируются первым дешифратором (при V1=0иV2=1,т.е. прих3=0, или вторым (приV1=1 иV2=0, т.е. прих3=1) дешифратором.

К 530 ИД 14

Рис.1. Дешифратор К 530 ИД 14 (а) и способ соединения двух дешифраторов для увеличения разрядности (наращивания числа входов-выходов) (б)