Лабораторная работа №7

Синтез и исследование RS-триггеров

Общие сведения

Триггер переходит из текущего состояния X на выходе к состоянию Q=0, при подаче на вход S нуля (единицы) и на вход R единицы (нуля), а при поступлении на вход S единицы (нуля) и на вход R нуля (единицы) триггер переходит к состоянию Q=l. При нулевых (единичных) значениях триггер должен сохранять старое значение. Четвертая входная комбинация считается не определенной, поскольку она приводит к одинаковому состоянию выходов триггера, тем самым нарушая условие взаимной инверсности последних.

В зависимости от того, сигналом какого уровня (0 или 1) осуществляется установка (сброс) выходного состояния триггера, различают RS-триггеры с прямыми и инверсными входами. В свою очередь то, какая комбинация (00 или 11) является неопределенной, зависит от того, на каких элементах (И-НЕ или ИЛИ-НЕ) построен триггер.

В таблице приведены состояния RS-триггера с инверсными входами для внутренней логики И-НЕ и логики ИЛИ-НЕ.

Таблица

Вход |

Выход |

||||

R |

S |

Логика И-НЕ |

Логика ИЛИ-НЕ |

||

Q |

|

Q |

|

||

0 |

0 |

Не определено |

Без изменения |

||

0 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

Без изменения |

Не определено |

||

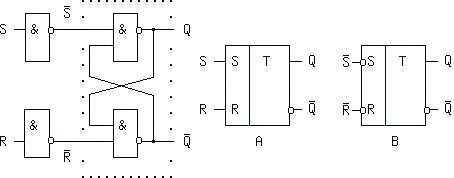

На рисунке 1 показаны внутренняя схема и условные графические обозначения (УГО) RS-триггера, построенного на логике И-НЕ. Условное обозначение В соответствует части рисунка, обведенной точками, т.е. RS-триггеру с инверсными входами, а обозначение А – всему рисунку, или RS-триггеру с прямыми входами.

Рис.1

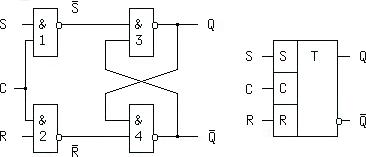

Если вместо входных инверторов 1 и 2 (см. рис.3.2) использовать элементы И-НЕ и их не задействованные входы соединить вместе, получится синхронный RS-триггер со статическим управлением (синхронизируемый уровнем). Схема и условное обозначение приведены на рисунке 2.

Рис.2

Нетрудно убедиться, что при С=0 независимо от значении S и R выходы сохраняют старые значения и триггер находится в режиме памяти. При С=1 он функционирует, как асинхронный RS-триггер. Триггеры со статическим управлением называют, также "прозрачными", т.к. при активном уровне синхросигнала С информация с входов беспрепятственно проходит на выходы.

Задание

Собрать схему, показанную на рисунке 1 и соответствующую прямой входной логике.

Изменяя состояния сигналов S и R на входах схемы проверить соответствие выходных сигналов схемы приведенной таблице истинности.

Видоизменить собранную схему в соответствии с рисунком 2 и проверить ее работу в качестве синхронного «прозрачного» RS-триггера.

Лабораторная работа №8

Исследование сдвиговых регистров

Общие сведения

Регистр – это линейка из нескольких триггеров, в которой в отличие от счетчиков-делителей нет внутренних запрещающих обратных связей. Регистры применяются для накопления и сдвига данных.

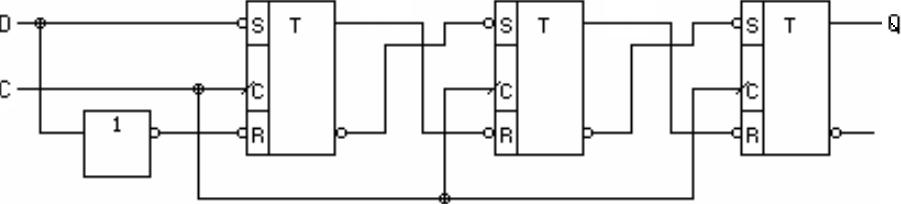

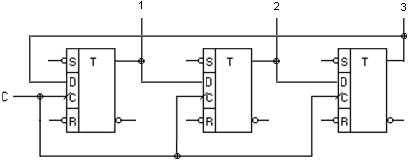

В простейшем

сдвиговом регистре триггеры соединены

последовательно. Например, при

использовании в качестве основы регистра

динамических RSC-триггеров

выходы q и

![]() предыдущего триггера передают бит

данных на входы R и S последующего. Все

тактовые входы С триггеров соединены

параллельно. При таком включении единица,

записанная в виде напряжений низкого

и высокого уровней по входам R и S первого

триггера, после подачи одного тактового

импульса перейдет во второй триггер,

затем во время следующего тактового

импульса она попадет в третий триггер

и так проследует далее, до конца регистра

(см. рисунок 1).

предыдущего триггера передают бит

данных на входы R и S последующего. Все

тактовые входы С триггеров соединены

параллельно. При таком включении единица,

записанная в виде напряжений низкого

и высокого уровней по входам R и S первого

триггера, после подачи одного тактового

импульса перейдет во второй триггер,

затем во время следующего тактового

импульса она попадет в третий триггер

и так проследует далее, до конца регистра

(см. рисунок 1).

Рис.1

Аналогично продвигается по регистру многоразрядное слово: оно поразрядно вводится на входы R и S первого триггера. Простейший регистр имеет один вход и один выход – последовательные. Вход управления также единственный – тактовый. Если ко входу каждого триггера добавить разрешающую логику, можно получить дополнительные, так называемые параллельные входы одновременной загрузки байта в регистр. Здесь, как правило, используются дополнительные защелки, где фиксируются данные, поступившие на входы после прихода тактового импульса. В такую схему добавляется вход разрешения записи.

Можно предусмотреть также логическую схему параллельного отображения на выходах состояния каждого триггера:

Рис.2

Тогда после заполнения регистра от последовательного или параллельных входов, по команде разрешения выхода накопленное цифровое слово можно отобразить поразрядно сразу на всех параллельных выходах.

В качестве основы регистра также можно использовать динамические D- и универсальные JK-триггеры.

Задание

Для исследования работы сдвигового регистра следует собрать схему на основе динамических D-триггеров, показанную на рисунке 3.

Рис.3

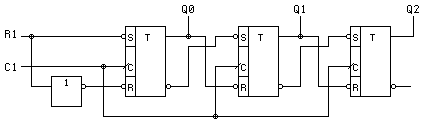

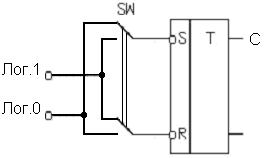

В качестве источника сигнала С следует использовать генератор одиночных импульсов, установленный на стенде, или организовать работу от переключателя «0–1». В последнем случае рекомендуется установить защиту от дребезга контактов переключателя (пример схемы показан на рисунке 4).

Рис.4

Подавая на входы S триггеров соответствующие сигналы, обеспечить установление на выходах 1–3 регистра логической комбинации 1 0 0.

Составить таблицу последовательных выходных состояний регистра, включенного по схеме рис.3, моделируя подачу импульса на вход С.