Лабораторная работа №5

Синтез и исследование сумматоров

Общие сведения

Сумматоры – устройства, осуществляющие основную арифметическую операцию – суммирование чисел в двоичном коде. Простейший случай – суммирование двух одноразрядных чисел: 0+0=0, 1+0=1, 0+1=1 и 1+1 =10. В последнем случае выходное число 10 (в десятичной записи это 2) оказалось двоичным двухразрядным. Появившаяся в старшем разряде суммы единица называется единицей переноса.

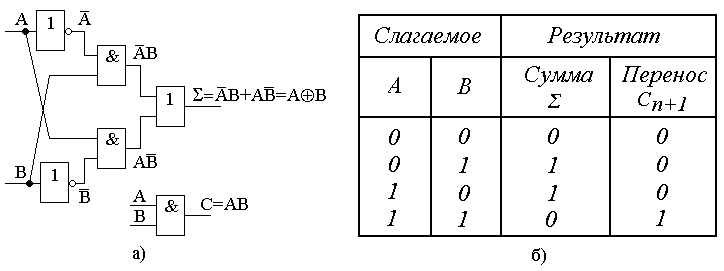

На первой лекции были перечислены состояния схемы «исключающее ИЛИ». Эти состояния соответствуют рассмотренному примеру (кроме случая 1l=0 – суммирование по модулю 2). К схеме «исключающее ИЛИ» несложно добавить выход переноса, т.е. генератор старшего разряда. Для этого оба суммируемых одноразрядных числа следует подать на схему И, выход которой даст необходимый старший разряд переноса 11=1. На рис.1,а показана реализация схемы суммирования двух одноразрядных чисел, состоящая из элементов исключающее или и и. Схема имеет два выходных провода: суммы и переноса. Такая схема называется полусумматором.

Рис.1

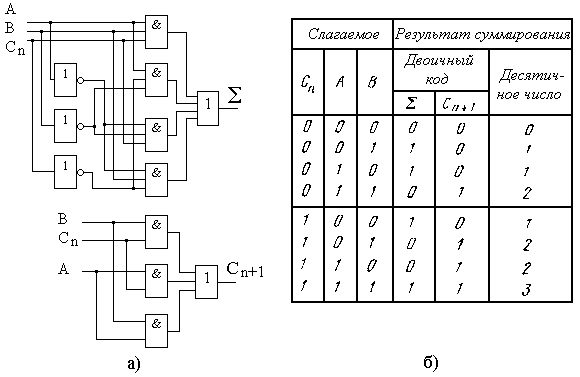

Полный сумматор должен иметь вход для приема сигнала переноса Cn (здесь n – число разрядов в суммируемых словах). Схема полного сумматора двух одноразрядных слов и таблица его состояний показаны на рис.2. В последнем столбце таблицы результаты суммирования даны в десятичной форме. В присутствии входной единицы переноса Cn сумма чисел А и В увеличивается на 1.

Рис.2

Задание

Собрать и исследовать при различных комбинациях входных сигналов схему полусумматора в соответствии с рис.1.

То же для полного сумматора в соответствии с рис.2.

Лабораторная работа №6

Синтез и исследование преобразователей кодов

Общие сведения

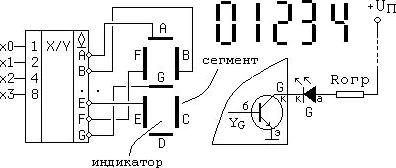

Преобразователи кодов (ПК) могут быть весовыми и невесовыми. Весовые ПК преобразуют информацию из одной системы счисления в другую. Основное назначение невесовых – преобразование информации для ее дальнейшего отображения. По ГОСТ'у преобразователь обозначается наклонной чертой, где в "числителе" стоит то, что, а в "знаменателе" – то, во что преобразуется (в нашем случае некоторый код X преобразуется в некоторый код Y). В качестве примера рассмотрим преобразователь двоично-десятичного кода в код для семисегментных светодиодных индикаторов. На рисунке также показан фрагмент подключения одного светодиода (сегмента) к выходу преобразователя с открытыми коллекторами & и приведены начертания первых пяти цифр.

Такой преобразователь должен иметь четыре входа, т.к. для кодирования десятичных цифр от 0 до 9 достаточно четырех двоичных разрядов, и семь выходов, по одному на каждый сегмент.

Сформулируем условия свечения/гашения светодиода:

1) Светодиод "горит", если напряжение на его аноде больше, чем на катоде (о конкретных значениях напряжения и тока пока речь не идет). Анод через резистор, ограничивающий, ток уже подключен к плюсу источника питания, поэтому на катоде должен быть потенциал, близкий к нулю. Для этого n-p-n транзистор, работающий в ключевом режиме, должен быть открыт. Тогда потенциал его коллектора близок к нулю. Транзистор открыт, если потенциал на его базе больше нуля, т.е. должно YG=l ( YG – логическая переменная, соответствующая сегменту G).

2) Светодиод погашен, если потенциалы его анода и катода равны. Это достигается, если ключевой транзистор закрыт и через него не протекает ток. Потенциал базы в этом случае должен быть равен нулю, т.е. YG=0.

Теперь в соответствии с полученными условиями заполним таблицу истинности преобразователя. Например в цифре 0 должны светиться все сегменты за исключением сегмента G. В цифре 1 светятся только два сегмента В и С и т.д. Весовые коэффициенты bi двоично-десятичных разрядов равны 2i (8,4,2 и 1). Справа дана таблица истинности. В таблице до конца заполнена только колонка для сегмента А. Нули в ней проставлены для тех цифр, в которых сегмент А не светится.

Десятичная цифра |

8 |

4 |

2 |

1 |

|

Сегменты |

х3 |

х2 |

x1 |

х0 |

YA |

YB YC YD YE YF YG |

|

0 |

0 |

0 |

0 |

0 |

1 |

1 1 1 1 1 0 |

1 |

0 |

0 |

0 |

1 |

0 |

1 1 0 0 0 0 |

2 |

0 |

0 |

1 |

0 |

1 |

… … … |

3 |

0 |

0 |

1 |

1 |

1 |

… … |

4 |

0 |

1 |

0 |

0 |

0 |

… |

5 |

0 |

1 |

0 |

1 |

1 |

|

6 |

0 |

1 |

1 |

0 |

1 |

|

7 |

0 |

1 |

1 |

1 |

1 |

|

8 |

1 |

0 |

0 |

0 |

1 |

|

9 |

1 |

0 |

0 |

1 |

1 |

|

![]() (сомножитель

(сомножитель

![]() во втором слагаемом отсутствует,

т.к. комбинация 1100 не соответствует

десятичной цифре и поэтому не

рассматривается). Тогда

искомое выражение будет иметь вид:

во втором слагаемом отсутствует,

т.к. комбинация 1100 не соответствует

десятичной цифре и поэтому не

рассматривается). Тогда

искомое выражение будет иметь вид:

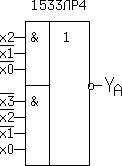

![]() .

Соответствующая ему реализация на

элементе И-ИЛИ-НЕ будет одной из самых

простых (см. рисунок). Аналогично могут

быть составлены и реализованы остальные

логические функции.

.

Соответствующая ему реализация на

элементе И-ИЛИ-НЕ будет одной из самых

простых (см. рисунок). Аналогично могут

быть составлены и реализованы остальные

логические функции.

Задание

1. Заполнить таблицу и составить остальные уравнения для сегментов B…G.

Примечание. При составлении уравнений рекомендуется учитывать, что входной код – двоично-десятичный, т.е. не все комбинации являются «разрешенными». Получаемые выражения следует упростить и по возможности привести к виду И-ИЛИ-НЕ.

2. Синтезировать схему преобразователя кода для отображения заданных преподавателем цифр.