- •Глава 5

- •5.1.2. Установочные микрооперации.

- •5.1.3. Запись информации от двух источников

- •5.1.4. Считывание информации

- •5.1.5. Логические микрооперации в регистрах

- •5.1.6. Микрооперации сдвига

- •5.1.7. Преобразование последовательного кода в параллельный и наоборот

- •5.1.8. Распределители тактов

- •5.1.9. Регистры в микросхемах серии кр1533

- •5.2.2. Двоичные суммирующие и вычитающие счетчики

- •5.2.3. Двоичные реверсивные счетчики

- •5.2.4. Двоично-десятичные счетчики

- •5.2.5. Счетчики с единичным кодированием

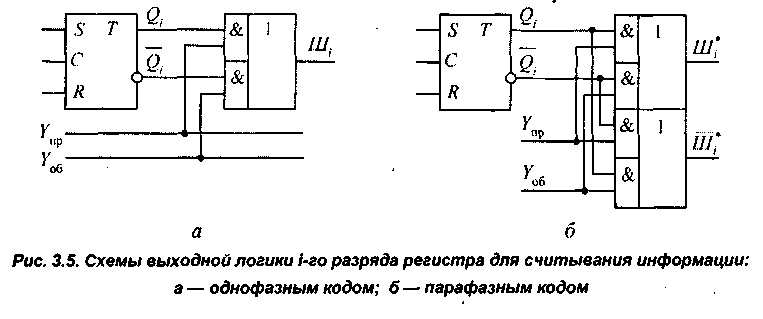

5.1.4. Считывание информации

Информация, хранимая в регистрах, может передаваться во внешние схемы однофазным или парафазным способом в прямом или обратном коде. Для реализации микроопераций считывания к выходам каждого триггера подключаются комбинационные схемы, образующие выходную логику регистра.

Схемы выходной логики строятся на основе следующих поразрядных логических уравнений:

• для считывания однофазным прямым или обратным кодом

Шi

=

Yпр

Qi

v

Yоб

(5.3)

(5.3)

• для считывания парафазным прямым или обратным кодом

Шi = YnpQi v Yпр ; Шi = Yo6 v Yo6Qi (5.4)

где Yпр и Yo6 — управляющие сигналы выдачи соответственно прямого или обратного кода;

Qi и Qi — прямое и инверсное значение, выхода r'-го разряда регистра;

Шi — разряд однофазной шины данных;

Шi и Шi — разряды парафазной шины данных.

Очевидно, что управляющие сигналы Yпр и Yоб не должны совпадать во времени.

Схемы выходной логики для i-го разряда на основе уравнений (5.3) и (5.4) показаны на рис. 5.5.

Рисунок 5.5-Схемы выходной логики i-разряда для считывания информации:

а) однофазным кодом; б) парофазным кодом

5.1.5. Логические микрооперации в регистрах

В регистрах могут выполняться следующие поразрядные (без переносов) логические микрооперации над словами А и В:

-логическое

сложение

и

умножение:

RG1:

= AvB;

RG1:

= А

В;

В;

-сложение

по

модулю

два

и

его

отрицание:

RG1:

= А В;

RG1:

=

В;

RG1:

=

;

;

-инверсия

слова:

RG1:

=

.

.

Логические микрооперации предполагают наличие первого слова А в регистре. С учетом этого логическое сложение слов А и В в регистре на RS- или JK-триггерах с однофазной записью выполняется вводом слов В без предварительного сброса.

Логическое

умножение

реализуется

подачей

инверсных

значений

разрядов

слова

B

на

входы

R

(или

K)

триггеров

регистра.

Действительно,

если

значение

Bi

= 0, тo

= 1 и

соответственно

триггеры

обнуляются,

что

и

требуется

для

поразрядного

логического

умножения.

= 1 и

соответственно

триггеры

обнуляются,

что

и

требуется

для

поразрядного

логического

умножения.

Микрооперации сложения по модулю два и его отрицания реализуются в регистрах на T-триггерах. Вначале записывается слово A, а затем без предварительного сброса по счетному входу вводится слово В.

После этого на прямых выходах триггеров фиксируется результат операции Q = А В, а на инверсных выходах - Q= .

Микрооперация инвертирования состоит в подаче импульса на все T-входы триггеров регистра, в которых хранится слово A. В итоге на прямых выходах триггеров устанавливается результат согласно соотношению Qi = Ai 1 = .

5.1.6. Микрооперации сдвига

Сдвиг — это одновременное пространственное перемещение двоичного слова в разрядной сетке с сохранением порядка следования нулей и единиц. Регистры, предназначенные для выполнения микроопераций сдвига, называются регистрами сдвига или сдвиговыми.

Микрооперации сдвига используют в процессе выполнения команд умножения, деления и нормализации. Кроме того, с помощью сдвига осуществляется преобразование параллельного кода в последовательный или наоборот (например, при обмене информацией с магнитными лентами и дисками).

Сдвиг слова может выполняться вправо (в сторону младших разрядов) или влево (в сторону старших разрядов).

Обозначим одноразрядные микрооперации сдвига вправо и влево символами R и L соответственно.

Различают правый и левый арифметический (Ra, La), логический (Rл, Lл) и циклический (Rц, Lц) сдвиги слова.

Пусть в регистре А записано слово Аn, Ап-1 ... А2 А1

где А1 — младший разряд; Аn — старший разряд.

Символически микрооперации сдвига записываются следующим образом:

• арифметические сдвиги (знаковый разряд не сдвигается):

RGA: = Ra(A) = An 0 An-1 ... A2; RGA : = La (A) = Аn Аn-2...А1 0 ;

• логические сдвиги (одновременно сдвигаются все разряды);

RGA: = Rл(A) = 0 Аn Аn-1 ...А2; RGA : = Lл(A) = Аn-1Аn-2 ...А1 0;

• циклические сдвиги (между старшим и младшим разрядами имеется кольцевая связь):

RGA := Rц (A) =A1 Аn Аn-1...А2; RGA : = Lц(A) = An-1 An-2 ...А1 An

Арифметические и циклические сдвиги преимущественно используют при выполнении команд в процессорах, а логические сдвиги обеспечивают преобразование последовательного кода в параллельный и наоборот в устройствах связи с магнитными лентами и дисками.

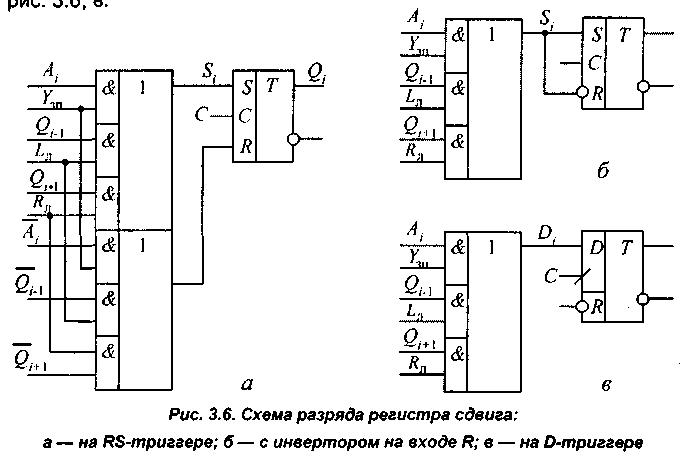

Сдвиговые регистры проектируют на двухступенчатых RS- (или JK-) или D-триггерах с динамическим управлением по фронту. Такие триггеры обеспечивают разделение во время процессов приема новой информации в каждом разряде и выдачи (сдвига)старой.

Примем, что в реверсивном регистре должны выполняться параллельная запись слова А по сигналу управления Yзп и сдвиги информации влево и вправо под воздействием управляющих сигналов Lл и Rл.

Схема одного разряда регистра сдвига на RS-триггерах показана на рис. 5.6, а.

Экономичная схема разряда регистра, в которой функция на R-входе триггера образуется инвертированием сигнала Si показана на рис. 3.6, б.

Однако в этом случае время записи данных увеличивается за счет задержки инвертора.

Схема разряда регистра сдвига на D-триггерах показана на рис. 5.6 в.

Рисунок 5.6-Схема разряда регистра сдвига:

а)-на RS-триггере; б)-с инвентором на входе R; в)-на D-триггере

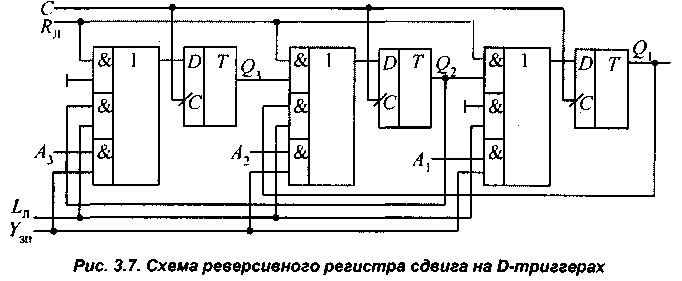

Пример построения реверсивного трехразрядного регистра сдвига на D-триггерах с динамическим управлением представлен на рис. 5.7.

Рисунок 5.7-Схема реверсивного регистра на D-триггерах

Реверсивный регистр сдвига работает следующим образом.

При значении сигнала Yзп = 1 в регистр записывается информация параллельным однофазным кодом.

При значении сигнала Rл = 1 хранимая информация одновременно сдвигается в сторону младших разрядов, при этом разряд Q3 обнуляется.

При значении сигнала Lл = 1 информация в регистре одновременно сдвигается в сторону старших разрядов, при этом разряд Q1 обнуляется.

Запись и сдвиг информации происходят по фронту синхроимпульса.