- •Вопрос 6. Обобщенная схема и принцип действия адресного зу. Обобщенная схема и принцип действия ассоциативного зу.

- •Вопрос 7. Организация запоминающих массивов адресных зу.

- •Структура зм (запоминающего массива) типа 2d.

- •Структура зм (запоминающего массива) типа 3d.

- •Структура зм (запоминающего массива) типа 3dm (модифицированная).

- •Вопрос 8. Расслоение памяти.

- •Вопрос 9. Статические зу с произвольной выборкой. Запоминающая ячейка статической памяти. Запоминающая ячейка с двухкоординатной выборкой. Запоминающая ячейка двухпортовой памяти.

- •Вопрос 10. Микросхема статической памяти. Диаграмма работы статической памяти.

- •Вопрос 11. Динамические зу с произвольной выборкой (dram).

- •Вопрос 12. Процесс считывания в динамических зу с произвольной выборкой. Принцип действия усилителя-регенератора.

- •Вопрос 13. Контроллер динамической памяти.

- •Вопрос 14. Микросхема динамической памяти.

- •Вопрос 15. Диаграмма работы dram, fpm dram и bedo dram памяти.

- •Вопрос 16. Диаграмма работы sdram и ddr sdram памяти.

- •Вопрос 18. Классификация пзу. Структура пзу.

- •Мпзу (mrom)

- •Ппзу (prom)

- •Рпзу-уф (eprom)

- •Опрпзу-уф (eprom-otp)

- •Рпзу-эс (eeprom), flash.

- •Fram (пзу на основе сегнетоэлектрической пленки)

- •8. Mram (Магниторезистивные пзу)

- •Вопрос 18. Характеристики, влияющие на эффективность кэш-памяти.

- •Вопрос 19. Кэш с произвольной загрузкой, прямым размещением, и наборно-ассоциативный кэш.

- •Вопрос 20. Алгоритмы замещения информации в кэш-памяти. Проблема согласования содержимого кэш-памяти и оперативной памяти.

- •Вопрос 21. Страничная организация виртуальной памяти. Сегментная организация виртуальной памяти. Сегментно-страничная организация виртуальной памяти.

- •Страничная организация.

- •Сегментно-страничная организация памяти.

Вопрос 15. Диаграмма работы dram, fpm dram и bedo dram памяти.

D RAM.

RAM.

tRCD – RAS to CAS Delay, время между сигналами RAS и CAS, оно определяет какой интервал времени нужно выдержать между выдачами адресов строк и столбцов.

tCAC – CAS Delay, определяет, через какое время после включения NOT(CAS ) будут считаны данные.

tRP – RAS Precharge, время предзаряда памяти.

FPM DRAM.

FPM DRAM – Fast Page Mode DRAM, память быстрого страничного режима. Основным отличием от памяти предыдущего поколения стала поддержка сокращенных адресов. Если очередная запрашиваемая ячейка находится в той же самой строке, что и предыдущая, ее адрес однозначно определяется одним лишь номером столбца и передача номера строки уже не требуется, поэтому t’ < tRCD+ tCAC (в диагрмме предполагается, что идет чтение одной и той же страницы).

BEDO DRAM.

У FPM низкое состояние CAS удерживается до окончания считывания данных, затем CAS дезактивируется, выдерживается небольшая пауза на перезарядку внутренних цепей, и только после этого на адресную шину подается номер колонки следующей ячейки. В новом типе памяти, получившем название EDO-DRAM (Extend Data Output), напротив, CAS дезактивируется в процессе чтения данных параллельно с перезарядкой внутренних цепей, благодаря чему номер следующего столбца может подаваться до завершения считывания линий данных.

Двукратное увеличение производительности было достигнуто лишь в BEDO-DRAM (Burst EDO). Добавив в микросхему генератор номера столбца, конструкторы ликвидировали задержку CAS Delay, сократив время цикла до 15 нс. После обращения к произвольной ячейке микросхема BEDO автоматически, без указаний со стороны контроллера, увеличивает номер столбца на единицу, не требуя его явной передачи. По причине ограниченной разрядности адресного счетчика (конструкторы отвели под него всего лишь

два бита) максимальная длина пакета не могла превышать четырех ячеек (2*2=4).

0

0

Здесь успеваем регенерировать

При передачи первой «четверти» пакета tCAC все же присутствует (генератор номера столбца нужно установаить в начальное положение), но потом оно равно нулю.

Вопрос 16. Диаграмма работы sdram и ddr sdram памяти.

SDRAM

Появление микропроцессоров с шинами на 100 MHz привело кvрадикальному пересмотру механизма управления памятью, и подтолкнуло конструкторов к созданию синхронной динамической памяти – SDRAM (Synchronous-DRAM). Как и следует из ее названия, микросхемы SDRAM памяти работают синхронно с контроллером, что гарантирует завершение цикла в строго заданный срок. Кроме того, номера строк и столбцов подаются одновременно, с таким расчетом, чтобы к приходу следующего тактового импульса сигналы уже успели стабилизироваться и были готовы к считыванию. Так же, в SDRAM реализован усовершенствованный пакетный режим обмена. Контроллер может запросить как одну, так и несколько последовательных ячеек памяти, а при желании - всю строку целиком. Это стало возможным благодаря использованию полноразрядного адресного счетчика уже не ограниченного, как в BEDO, двумя битами.

Количество банков памяти в SDRAM увеличено с одного до двух ( четырех). Это позволяет обращаться к ячейкам одного банка параллельно с перезарядкой внутренних цепей другого, что вдвое увеличивает предельно допустимую тактовую частоту. Помимо этого появилась возможность одновременного открытия двух (четырех) страниц памяти, причем открытие одной страницы (т.е. передача номера строки) может происходить во время считывания информации с другой, что позволяет обращаться по новому адресу столбца ячейки памяти на каждом тактовом цикле.

В отличие от FPM-DRAM\EDO-DRAM\BEDO, выполняющих перезарядку внутренних цепей при закрытии страницы (т.е. при дезактивации сигнала RAS), синхронная память проделывает эту операцию автоматически, позволяя держать страницы открытыми столь долго, сколько это угодно.

DQM подкл - т вых буф. к шине (аналог OE в SRAM)

Тайминг: 4-1-1-1

tCL – CAC latency (оно же tCAC )

Под таймингом памяти понимается набор: CAS-tRCD-tRP-tRAS:

CAS Latency (CAS) - задержка в тактах между подачей сигнала CAS и непосредственно выдачей данных из соответствующей ячейки. Одна из важнейших характеристик любого модуля памяти;

RAS to CAS Delay (tRCD) - количество тактов шины памяти, которые должны пройти после подачи сигнала RAS до того, как можно будет подать сигнал CAS;

Row Precharge (tRP) - время закрытия страницы памяти в пределах одного банка, тратящееся на его перезарядку;

Activate to Precharge (tRAS) - время активности строба. Минимальное количество циклов между командой активации (RAS) и командой подзарядки (Precharge), которой заканчивается работа с этой строкой, или закрытия одного и того же банка.

Таким образом, к достоинствам SDRAM относятся:

- Многобанковая огранизация.

- Командный режим работы.

- Команды пакетного чтения/записи.

- Использование чередования банков при последовательном увеличении адресов.

- Команды пакетного чтения/записи с авторегенерацией.

- Возможность осанова чтения/записи по режиму регенерации.

- Возможность останова чтения/записи по новому запросу чтения/записи.

- Управление маскированием шины данных по сигналу DQM.

- Минимальное время (1 CLK) между последовательными командами.

- Команда PrechargeAll (подзарядить все).

- CAS латентность 2 и 3 CLK.

- Длина пакета 1,2 и 4 слова.

- Команда саморегенерации.

- Режим энергосбережения.

P.S. Диаграмма кажется здоровой и тяжело запоминаемой. Но во всех предыдущих схемах не было сигналов C, CS, CKM, DQM, поэтому если их мысленно убрать или карандашом без них начертить, то все okay.

DDR SDRAM

Дальнее развитие синхронной памяти привело к появлению DDR SDRAM- Double Data Rate SDRAM (SDRAM c удвоенной скорости передачи данных). Удвоение скорости достигается за счет передачи данных и по фронту, и по спаду тактового импульса (в SDRAM передача данных осуществляется только по фронту). Благодаря этому эффективная частота

увеличивается в два раза - 100 MHz DDR-SDRAM по своей производительности эквивалента 200 MHz SDRAM.

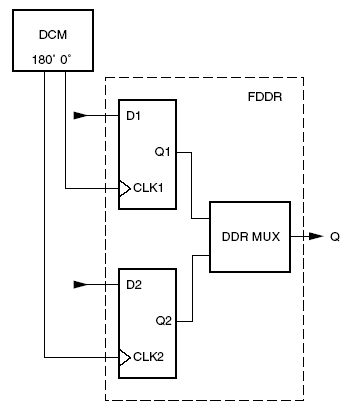

Схема слева реализует возможность передачи и по фронту и по спаду тактового импульса.

DCM – Digital Clock Manager, вырабатывает два противофазных сигнала.

Преимущества:

- Синхронизация.

- Конвейеризация.

-

Пакетный режим обмена.

- Чередование

банков при обращении по последовательным

адресам (это ускоряет скорость – см.

вопрос 8).

-

Удвоение скорости.

Синхронизация.

- Конвейеризация.

-

Пакетный режим обмена.

- Чередование

банков при обращении по последовательным

адресам (это ускоряет скорость – см.

вопрос 8).

-

Удвоение скорости.

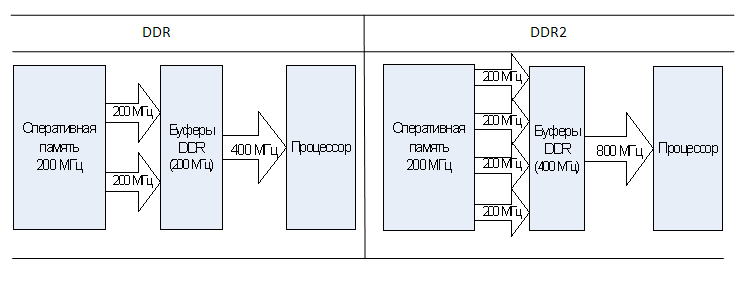

С равнение

DDR

SDRAM

и DDR2

SDRAM.

равнение

DDR

SDRAM

и DDR2

SDRAM.

Основное отличие в том, что шина DDR2 работаю на частоте в два раза больше, чем шины DDR.