- •Глава 5 коммуникационные микроконтроллеры и системы на их основе

- •5.1. Общие понятия

- •5.1.1. Семиуровневая модель управления в сетях

- •5.1.2. Функции, реализуемые коммуникационным контроллером

- •5.1.3. Семейство коммуникационных микроконтроллеров мрс860

- •5.2. Организация коммуникационных процессорных модулей в кмк

- •5.2.1. Структура коммуникационного процессорного модуля

- •5.2.2. Контроллеры коммуникационных каналов scc

- •5.2.3. Контроллеры управления smc

- •5.2.4. Контроллеры дополнительных коммуникационных каналов

- •5.3. Поддержка протоколов в коммуникационных

- •5.3.1. Доступ к линиям т1/серт. Поддержка basic isdn

- •5.3.2. Виртуальные каналы и поддержка primary isdn

- •5.3.3. Работа в асинхронных каналах связи

- •5.3.4. Доступ к сетям с пакетной передачей (с протоколами х.25)

- •Алгоритмы работы сети. Процесс установления соединения

- •Процесс разъединения

- •Процесс передачи сообщения

- •5.3.5. Доступ к сетям ethernet

- •5.3.6. Протоколы, поддерживаемые на уровне загружаемого микрокода

5.3.2. Виртуальные каналы и поддержка primary isdn

Общие сведения о контроллере QMC (QUICC Multichannel Controller). QMC-npo-токол обеспечивает поддержку до 64 логических каналов внутри одного SCC-канала, используя TDM-интерфейс временного мультиплексирования. QMC-протокол реализуется за счет оптимального использования аппаратуры и не является загружаемым микрокодом. Любой из TDM-каналов в последовательном интерфейсе определенных версий контроллеров может быть назначен для работы с QMC-протоколом. Стандартный МРС860 может работать с TDM-каналом, но поддерживает только один логический канал для каждого SCC-контроллера. QMC-протокол реализован в следующих версиях контроллеров: МРС860МН (расширение MPC860EN), MPC860DH (расширение MPC860DE).

Поддержка 64-канального QMC-канала возможна только в версиях контроллеров с частотой не меньше 50 МГц, так как в версиях контроллеров с меньшими системными частотами не обеспечить требуемой скорости обработки сетевых данных. Реализация 64-канального QMC-контроллера в 50 МГц версии МРС860МН производится с использованием двух SCC-каналов, каждый из которых работает с 32-канальным QMC-протоколом. Контроллер МРС860МН имеет достаточный объем внутренней двухпортовой памяти для реализации двух QMC-каналов без значительных ухудшений в показателях работы коммуникационного модуля .Каждый QMC-канал обеспечивает передачу данных со скоростью 64 Кбит/с, как и в обычном временном слоте линии Т1/Е1, что обеспечивает суммарную пропускную способность 64хг64 Кбит/с = 4 Мбит/с.

Версия PRI ISDN широко используется в мире как высокоскоростной и эффективный по стоимости интерфейс. В Северной Америке стандарт предусматривает реализацию физического соединения по линиям Т1 с использованием 24 каналов по 64 Кбит/с каждый. В Европе соединения реализуются по линиям Е1 (СЕРТ) с использованием 32 каналов по 64 Кбит/с каждый. Поток данных внутри каналов может быть разделен на подканалы. Для каждого канала назначен при обмене свой временной слот внутри кадра. Начало кадра отмечается стробирующим сигналом с частотой 8 КГц (125 мкс). Пропускная способность линии рассчитывается так: 8 КГц х длину кадра данных в битах. Например, для линии Е1 со скоростью передачи данных 2048 Кбит/с = 8 КГцх256 бит, для линии Т1 со скоростью передачи данных 1544 Кбит/с=8 КГцх193 бита. Общая длина кадра данных должна быть поделена между 24 каналами для линии Т1 и между 32 каналами для линии Е1. Для повышения надежности передачи информации и с целью подстройки синхронизации отдельные специальные временные каналы могут быть выделены для целей управления и контроля.

Для поддержки интерфейсов Е1/Т1 QMC-протокол может мультиплексировать до 64 различных групп каналов на одном TDM-интерфейсе. Так как Е1-интерфейс работает с 32 временными каналами (64 Кбит/с), а Т1 - с 24 каналами (64 Кбит/с), а ОМС-контроллер может поддерживать на каждом SCC-канале до 64 логических каналов, то в контроллерах возможно организовать обработку сразу двух отдельных Е1/Т1-линий, каждая на своем SCC-контроллере. Логический канал может быть независимо запрограммирован на работу или с HDLC-кадрами, или в режиме прозрачной (transparent) передачи. Это дает возможность разделять TDM-потоки между несколькими SCC-контроллерами. Благодаря RISC-контроллеру SCC-каналы работают в нормальном режиме, не замечая и не принимая участие в реализации некоторых функций QMC-протокола. SCC только выполняют последовательно-параллельное преобразование данных канала и реализуют алгоритмы работы выбранных протоколов, а СРМ-модуль, используя встроенный микрокод и дополнительную аппаратуру, позволяет передавать кадры всех протоколов по любому из 64 каналов. Любой SCC-канал может работать в ОМС-режиме независимо от режимов работы других SCC-контроллеров. Так как SCC1-контроллер имеет больший размер буферов FIFO по сравнению с другими SCC-каналами, то он и рекомендован для работы с QMC-протоколом. Один ТОМ может быть настроен для работы с несколькими SCC-каналами, которые работают с QMC-протоколом, при этом каждый SCC-контроллер работает со своим временным слотом. Если два TDM-канала подключены к одному SCC-контроллеру, то возникают ограничения, связанные с использованием одинаковых тактовых и стробирующих сигналов, и при программировании памяти маршрутизации следует контролировать коллизии, когда в один и тот же момент времени придется работать с несколькими каналами одновременно или при приеме, или при передаче данных. Особенности работы MC860MH/DH.

Поддерживается до 64 независимых логических каналов для каждого SCC-контроллера.

Каждый логический канал может работать с любым из 64 временных слотов TDM- канала. А так как каждый контроллер из семейств МРС860 имеет два полностью неза- висимых TDM-канала, то это делает их особо привлекательными при построении мо- стовых схем.

При объединении RX- и ТХ-частей памяти маршрутизации каждый логический канал может работать с любым из 128 временных слотов TDM-канала.

Возможна одновременная поддержка двух 32-канальных Е1-соединений при систем ной частоте в 50 МГц.

При работе с буферами памяти используется до 128 DMA-каналов.

Полностью независимое распределение временных каналов для приемника и пере датчика.

Поддерживается или HDLC или Transparent-протокол для каждого логического канала.

Прерывание может быть назначено после обработки буфера заданного размера или при переполнении буфера.

Каждый логический канал может работать в режиме внутренней петли.

Число обрабатываемых временных каналов зависит только от числа ячеек в памяти маршрутизации. Пользователь может сам программироватьв памяти маршрутизации, какие временные каналы и какого размера будут использоваться в TDM-кадре.

Начало кадра регистрируется при приходе стробирующего сигнала. Дополнительные внешние сигналы - стробы могут выставляться для работы с сетевыми устройствами, которые не поддерживают работу с TDM-каналами, например для обмена данными с контроллером МС68302.

Особенности последовательного интерфейса.

Поддерживает работу с 24-канальным T1/DS1 и 32-канальным Е1/СЕРТ РСМ- интерфейсами, basic ISDN и primary ISDN.

Поддерживается работа с 2048,1544, 1536 Кбит/с РСМ-интерфейсами.

Любой временной слот может быть разделен на логические каналы.

Полностью независимые приемная и передающая части.

•Несколько, не обязательно соседних, временных слотов могут быть объединены в логический канал.

•Поддерживает НО, Н11, Н12 ISDN-каналы.

При работе с TDM-каналами доступны следующие функции последовательного интерфейса: синхронизация кадров, тестовый режим локальной петли, тестовый режим автоматического эха. При работе в NMSI-режиме эти функции не доступны. При работе в NMSI-режиме синхронизация кадров достигается за счет использования импульсов внешних сигналов и

Режим локальной петли (при программировании ячейки памяти маршрутизации бит LOOP := 1) может быть включен для любого как временного, так и логического канала. Требуется только, чтобы частоты тактовых сигналов приемника и передатчика были равны и использовался общий импульс строба начала кадра. При этом данные, принятые из N логического канала, будут без промежуточной буферизации выдаваться в N логический канал на выходе передатчика.

Режим автоматического эха для QMC-протокола можно включить только для всего TDM-кадра. Режим автоматического эха для отдельного временного канала можно реализовать только программным путем.

QМС-маршрутизация. QMC-протокол обеспечивает реализацию обработки нескольких логических каналов на одном SCC-контроллере. Выбор и программирование работы SCC-контроллера с некоторым временным каналом TDM-кадра осуществляется обычным способом, как описано ранее. Индивидуальное разделение временного канала по логическим каналам производится внутри QMC-контроллера с помощью специальных внутренних таблиц маршрутизации.

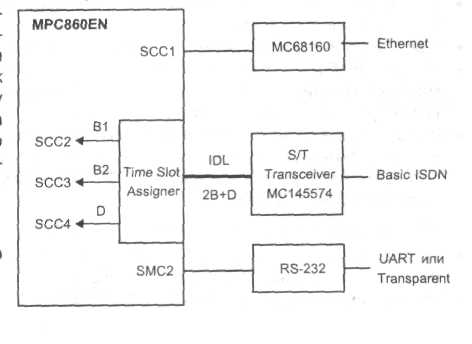

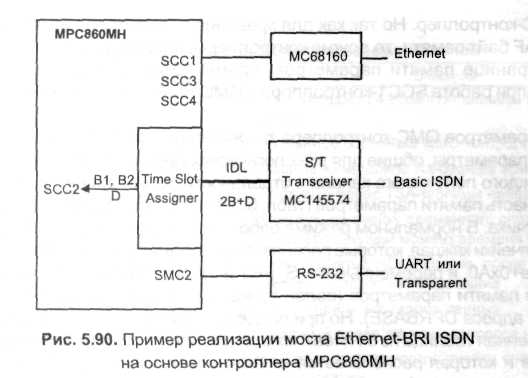

На рис. 5.89, 5.90 показаны схемы реализации Ethernet-BRI ISDN моста на базе MPC860EN (не поддерживает QMC-протокол) и на базе МРС860МН (поддерживает QMC-протокол). BRI ISDN-протокол требует обработки трех каналов (2B+D). В первом случае для обработки трех каналов пришлось задействовать три SCC-контроллера (SCC2, SCC3, SCC4), объединив их в мультиплексируемом режиме работы, а во втором - только один SCC2. Освободившиеся SCC-контроллеры можно использовать для реализации дополнительных линий связи или просто выключить, чтобы снизить потребление энергии и повысить производительность системы. Дополнительно контроллер SCC1 используется для подключения к сети Ethernet, a SMC-контроллер, работающий с протоколом UART, -для передачи данных на терминал компьютера контроля. Оба контроллера - и SCC1 и SMC2 настроены на NMSI-режим работы. Порт SPI используется для настройки режимов работы микросхемы ISDN-передатчика. Если во втором варианте схемы заменить контроллер на МРС860МН и S/T-передатчик МС145574 - на микросхему DS2180A, то получим схему моста Ethemet-PRI ISDN, обслуживающую 32-канальный ISDN (ЗОВ +1D) на одном 5СС2-контроллере.

Рис. 5.89. Пример реализации моста Ethernet-BRI ISDN на основе контроллера MPC860EN

Обратите внимание, что если один временной канал TDM-кадра занят QMC SCC-контроллером для работы с логическими каналами, то остальные временные каналы без ограничений могут быть использованы для нормальной работы другими SCC- и SMC-контроллерами.

При работе с QMC-протоколом могут регистрироваться следующие типы ошибок.

• Ошибка в битах данных обычно регистрируется контроллером, который работает с кон-

кретным протоколом в соответствии с правилами работы этого протокола. Обычно это может быть ошибка CRC контрольной суммы, ошибка длины кадра протокола, ошибка кадра, длина которого не кратна 8 битам. Эти типы ошибок регистрируются коммуникационными контроллерами и отмечаются в битах ошибок буферов дескрипторов приемника или передатчика.

Ошибка тактовых импульсов. При программировании памяти маршрутизации пользователь задает общую длину TDM-кадра в битах, таким образом, известно число такто- вых импульсов между двумя строб-импульсами. Внутренние схемы контроллера подсчитывают число тактов между стробами и регистрируют ошибку, если оно не со впадает с ожидаемым.

Ошибка импульсов синхронизации связана с моментом прихода внешнего строб-импульса. Если пользователь неправильно запрограммировал память маршрутизации, то момент окончания обработки TDM-кадра может не совпасть с реальным концом кадра, приходящим от внешнего источника и отмечаемым внешним сигналом.

Организация памяти QМС-протокола. SCC-контроллер, для которого выбран QMC-протокол, в целом функционирует аналогично SCC-контроллерам, которые работают с обычными коммуникационными протоколами. При обмене данными используется структура буферов данных и буферных дескрипторов, память параметров служит для реализации контрольных функций в соответствии с выбранным протоколом. Карта распределения внутренней двухпортовой памяти в контроллере МРС860МН та же, что и в базовой модификации контроллера.

Для каждого SCC-канала в памяти параметров выделена специальная область (страница), где хранятся общие и протокол-ориентированные параметры настройки выбранного SCC-контроллера. При работе с QMC-протоколом на этих страницах будут храниться параметры настройки и указатели для всех логических каналов, с которыми будет работать SCC-контроллер. Но так как для хранения параметров логических каналов необходимо OxAF байт памяти, то другие контроллеры, параметры которых располагались на той же странице памяти параметров, временно не будут доступны. Например, в МРС860МН при работе SCC1-контроллера с QMC-протоколом PC-контроллер не будет доступен.

Память параметров QMC-контроллера так же состоит из двух частей: в первой части описываются параметры, общие для всех логических каналов, во второй части - параметры работы каждого логического канала в отдельности (канал-ориентированная память).

Большую часть памяти параметров (табл. 5.59) занимают ISA-таблицы для приемника и для передатчика. В нормальном режиме работы используются две таблицы - TSATRx и TSATTx по 32 ячейки каждая, которые располагаются в памяти по адресам от SCC base+0x20 и до SCC base+0xA0, и переменные Rx_S_PRT и Tx_S_PTR указывают на расположение этих таблиц в памяти параметров (более точно, они задают смещение начала таблицы относительно адреса DPRBASE). Но при поддержке 64 логических каналов используется одна объединенная таблица из 64 ячеек, которая содержит общие параметры и приемника и передатчика и которая располагается в памяти по тем же адресам. В этом варианте приемник и передатчик работают с одинаковым закреплением между временными каналами и логическими каналами. Если же такой вариант распределения памяти не может быть применен, так как приемник и передатчик должны иметь разные параметры настроек, тогда для хранения общих Rx- и Тх-параметров может быть использована память параметров других SCC-каналов, и переменные Rx_S_PRT и Tx_S_PTR будут указывать на расположение частей этой таблицы в других областях памяти параметров.

Переменная Tx_S_PTR задает адрес начала таблицы TSATTx. В нормальном режиме работы с двумя TSA-таблицами значение TX_S_PTR = SCCbase+0хб0, но если используется объединенная таблица для приема и передачи, то значение TX_S_PTR = SCCbase+0x20. Эта таблица может быть размещена только внутри области общих параметров SCC.

Переменная Rx_S_PTR задает адрес начала таблицы TSATRx. В нормальном режиме работы значение RX_S_PTR=SCCbase+Ox20. Эта таблица может быть размещена только внутри области общих параметров SCC-канала.

Переменная MCBASE задает адрес начала таблицы буферных дескрипторов во внешней памяти, а переменные RBASE и TBASE из канал-ориентированной части памяти параметров определяют 16-битный сдвиг (offset) буфера дескриптора конкретного логического канала относительно адреса начала таблицы дескрипторов. Каждый логический канал имеет свои ячейки RBASE и TBASE в своей памяти параметров. Например, адрес дескриптора приема пятого логического канала будет равен MCBASE+RBASE_5.

Таблица буферов дескрипторов QMC-протокола располагается внутри 64-Кбайтной области внешней памяти. Размер таблицы определяется числом обрабатываемых логических каналов. Каждый SCC-контроллер имеет максимум 64 К/4 = 16384 буферов дескрипторов. Каждый дескриптор имеет стандартный 4-байтный формат, как и при работе с другими коммуникационными протоколами. Если при работе используются 32 логических канала, то каждый канал имеет по 16384/(32х2) = 256 буферов для приема и 256 буферов для передачи. Для каждого логического канала пользователь может программно задавать стартовый адрес таблицы дескрипторов и ее длину. Формат буферных дескрипторов аналогичен формату дескрипторов для других коммуникационных протоколов. Каждый буферный дескриптор имеет 32-битный адрес, который указывает расположение во внешней памяти буфера данных, связанного с этим дескриптором. Рекомендуется буферные дескрипторы других не QMC-протоколов располагать во внутренней памяти для уменьшения загрузки внешней шины.

П

Переменная MRBLR

задает размер буфера приемника в байтах.

После заполнения текущего

буфера до значения MRBLR

приемник переходит к заполнению

следующего буфера.

Для хранения каждого буфера в памяти

выделяется MRBLR+4

байт. При работе этот

параметр используется только в режиме

HDLC-протокола.

Если ОМС-контроллер работает

с 32-разрядными словами, то значение

MRBLR

должно быть кратным 4 байтам.

Переменная RxPTR

инициализируется значением SCCbase+Ox20,

т. е. стартовым адресом

таблицы TSARx.

Переменная TxPTR

инициализируется значением SCCbase+0хб0,

т.

е. стартовым адресом таблицы TSATx.

При работе RICS-контроллер

увеличивает значение

этих переменных после завершения

обработки текущего временного слота.

Переменная

GRFCNT

- вычитающий счетчик, который подсчитывает

число кадров данных,

которые необходимо принять до выработки

запроса на прерывание. При достижении

счетчиком значения «0» вырабатывается

RXF-запрос

на прерывание и в ячейку загружается

значение из переменной GRFTHR.

Запросы

на прерывание расположены в памяти в

виде очереди, которая обрабатывается

по кругу. Ячейки этой очереди содержат

информацию о запросе на прерывание.

Переменная RxPTR инициализируется значением SCCbase+0x20, т. е. стартовым адресом таблицы TSARx. Переменная TxPTR инициализируется значением SCCbase+0хб0, т. е. стартовым адресом таблицы TSATx. При работе RICS-контроллер увеличивает значение этих переменных после завершения обработки текущего временного слота.

Переменная GRFCNT - вычитающий счетчик, который подсчитывает число кадров данных, которые необходимо принять до выработки запроса на прерывание. При достижении счетчиком значения «0» вырабатывается RXF-запрос на прерывание и в ячейку загружается значение из переменной GRFTHR.

Запросы на прерывание расположены в памяти в виде очереди, которая обрабатывается по кругу. Ячейки этой очереди содержат информацию о запросе на прерывание,

который может быть выставлен QMC-контроллером к центральному процессору. Пере-менная INTBASE определяет стартовый адрес таблицы запросов в памяти, a nepeмeнная INTPTR-адрес следующей ячейки очереди, куда RISC-контроллер запишет информацию о прерывании при возникновении соответствующего события. Перед началом работы в ячейку загружают значение INTPTR := INTBASE.

Каждая TSA-таблица содержит 32 ячейки по 16 бит каждая (рис. 5.91) и определяет правила обработки каждого из 32 логических каналов при приеме (TSA Rx-таблица) и при передаче (TSA Тх-таблица). Ячейки таблицы определяют, из какого временного слота N-дет читать информация в текущий логический канал при приеме или в какой временной слот будет выдаваться информация от текущего логического канала при передаче.

Бит V (Valid) определяет, используется данный временной слот или нет. Если бит

V =0,то временной слот не используется, и его данные игнорируются при при- еме, а при передаче во временной слот будет выдаваться код логической «1». Если бит

= 1, то 8 бит данных из временного слота после удаления служебных битов (например, типа бит-стаффинг) записываются в текущий буфер при приеме и выдаются в этот вре- менной слот при передаче.

Бит W (Wrap) позволяет программисту ограничивать число используемых временные слотов в TDM-кадре данных. Если бит W = 1, то это последняя ячейка в таблице. Далее после получения нового импульса синхронизации (строба) RISC-контроллер перейдет к обработке ячейки временного слота «0».

Channel pointer - 6-битный указатель, определяющий логический канал, с которым будет связан данный временной слот. На самом деле реальный указатель имеет длину 12 бит и представляет собой адрес канал-ориентированной памяти параметров (адрес: RBASE илиТВАSЕ). Шесть старших значащих бит берутся из поля TSATRx channel pointed(или TSATTx channel pointer), а младшие 6 бит всегда обнуляются. Таким образом. 12-битный адрес указывает на 64-байтную область канал-ориентированной памяти параметров. Канал-ориентированная память всегда общая для приемника и передатчика, таким образом, для 32-канального интерфейса требуется 32x64 = 2 Кбайт памяти внутри двухпортовой RAM, а для 64-канального интерфейса - 64x64 = 4 Кбайт.

Обычно канал-ориентированная память каждого канала занимает 8 байт, и поэтому в большинстве случаев указатель channel pointer временного канала «0» содержит адрес начала двухпортовой памяти (DPBASE), начиная с которого располагаются параметры «0» логического канала. Указатель channel pointer временного канала «1» обычно содержит адрес DPBASE+4, начиная с которого располагаются параметры «1» логического канала. Если необходимо объединить несколько временных слотов для работы с одним логическим каналом, то в полях channel pointer ячеек TSA-таблицы, которое закреплены за выбранными временными слотами, указывается одно и то же значение адреса памяти параметров логического канала.

Биты MASK[0:7] определяют, какие из восьми битов данных временного слота будут использоваться при работе. Если бит маски равен 0, то соответствующий ему бит временного канала игнорируется при обработке. Во время передачи данных на месте замаскированного бита временного канала передается «1».

Работа нескольких SCC-контроллеров с одним TDM-каналом. Рассмотрим пример, когда один TDM-кадр обслуживается двумя SCC-контроллерами (допустим SCC: SCC3), которые оба настроены на работу с QMC-протоколом. Причем оба SCC-контроллера обслуживают одну и ту же последовательность логических каналов. Другими словами, обработка TDM-кадра разделена между двумя SCC-контроллерами с целью увеличить скорость и распараллелить обработку данных. Допустим, контроллер SCC2 обрабатывает нечетные временные слоты, а контроллер SCC3 - четные. При этом возникают проблемы программирования доступа нескольких SCC-каналов к общей ISA-памяти параметров одного TDM-кадра. Поэтому существует два варианта настройки режимов работы SCC-контроллеров с TSA-памятью.

При первом варианте (допустим, обрабатывается 32-канальный TDM-кадр) каждый SCC-канал настроен на работу с QMC-протоколом, каждый канал имеет ячейки указателей Rx_S_PTR_2 и Rx_S_PTR_3, но эти указатели адресуются только к одной TSA-таблице контроллера SCC2. Таким образом, TSA-таблица располагается в памяти параметров контроллера SCC2, а область памяти TSA-таблицы контроллера SCC3 не используется. Указатель Rx_S_PTR_2 первоначально содержит адрес SCC2_base+0x20. Шестнадцать логических каналов, которые обрабатываются SCC2, расположены в первых 16 ячейках таблицы. В ячейке канала 30 установлен бит W = 1, показывающий, что обработка логических каналов контроллером SCC2 закончена. Указатель Rx_S_PTR_3 первоначально содержит адрес SCC2_base+0x40. Шестнадцать логических каналов, которые обрабатываются SCC3, расположены в ячейках таблицы, начиная с 17-го по 32-й. В ячейке канала 31 установлен бит W = 1, показывающий, что обработка логических каналов контроллером SCC3 закончена. Каждая ячейка в таблице имеет указатель на область параметров обрабатываемого логического канала. Но здесь необходимо проверять, чтобы случайно контроллеры SCC2 и SCC3 не обрабатывали один и тот же логический канал. Таблица TSATTx тоже находится в области памяти параметров контроллера SCC2, TSA-таблица в области SCC3 не используется, и эта память может быть отведена для других целей.

При втором варианте (допустим, обрабатывается 64-канальный TDM-кадр) для хранения TSA-таблиц приемника и передатчика требуется 256 байт памяти (64ячейки х 2 байта х 2 таблицы), но в памяти параметров одного SCC-канала свободно только 128 байт. Поэтому можно применить следующий способ размещения. Таблица приемников контроллеров SCC2 и SCC3 располагается в области памяти параметров канала SCC2, а таблица передатчиков - в области памяти параметров канала SCC3. Разделение таблицы на две части между SCC-каналами будет такое же, как и в первом варианте. Такое распределение памяти контроллеров более эффективно.

На основе приведенных примеров можно запрограммировать режим работы, когда все временные слоты будут обрабатываться разными SCC-контроллерами и TSA-память будет распределена между страницами памяти параметров отдельных контроллеров, а это позволяет эффективно расходовать память и вычислительные мощности каждого SCC-канала. Но при этом пользователь должен быть уверен, что не возникнут коллизии, когда из-за ошибок при программировании несколько SCC-контроллеров будут обрабатывать один временной слот.

Канал-ориентированная память параметров. Канал-ориентированная память параметров (Channel-Specific parameter RAM) занимает нижнюю (младшую) часть двухпортовой памяти. Каждый логический канал может быть связан с временным каналом TDM-кадра с помощью указателей канала в ячейках TSA-памяти. Пользователь может сам определять количество необходимых логических каналов. Для каждого логического канала в памяти выделяется область размером 64 байта, формат которой зависит от коммуникационного протокола, по правилам которого передается информация по логическому каналу. Свободные области логических каналов могут быть отведены для хранения буферных дескрипторов других SCC-контроллеров. При работе с QMC-протоколом логические каналы могут работать или в режиме HDLC-протокола или в режиме transparent «прозрачной передачи».

Работа с HDLC-протоколом. Распределение памяти при работе с этим протоколом приведено в табл. 5.60.

Переменные TBASE и RBASE задают смещение стартового адреса таблицы буферных дескрипторов конкретного логического канала относительно базового адреса 64-Кбай-тной таблицы буферных дескрипторов всех логических каналов, который задан в ячейке MCBASE памяти общих параметров.

Переменные TBPTR и RBPTR задают смещение адреса текущего буферного дескриптора обрабатываемого логического канала относительно базового адреса 64-Кбайт-ной таблицы буферных дескрипторов всех логических каналов, который задан в ячейке MCBASE памяти общих параметров. Например, реальный адрес текущего буферного дескриптора передатчика вычисляется как MCBASE+TBPTR.

Каждый SCC-канал имеет переменную MFLR, определяющую максимальное число байт (максимум 64 Кбайт), которые могут передаваться в кадре. При приеме кадра, длина которого больше MFLR, кадр будет отброшен, установлен бит ошибки LG = 1 в слове состояния текущего буферного дескриптора, буфер будет закрыт и будет выставлен запрос на прерывание от событий RXF и RXB в регистре событий, если они не замаскированы.

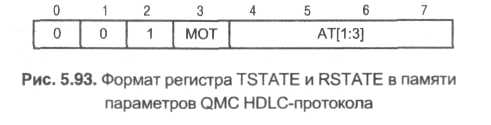

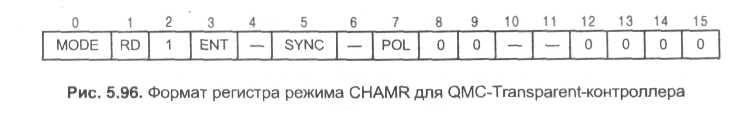

Бит MODE в регистре режима CHAMR (рис. 5.92) определяет протокол, с которым работает выбранный логический канал. Если MODE = 0, то канал работает с протоколом Transparent, если MODE=1 - с HDLC-протоколом.

Бит IDLM определяет режим передачи символов IDLE (если бит IDLM = 1) в промежутках между передачей кадров данных. Если IDLM = 0, то между кадрами данных IOLE-символы не передаются. В промежутке между кадрами передатчик передает NOF+1 символов флага, а затем передает следующий кадр данных. Если кадр еще не готов, то продолжается передача символов флага.

Бит ENT = 1 разрешает работу передатчика, и во временной канал будут передаваться данные согласно выбранному протоколу. Если бит ENT = 0, то передатчик выключен, и если канал подключен к временному слоту, то в этот временной канал будут передаваться «1». Следует отметить, что отсутствует бит разрешения работы приемника с QMC-протоколом, но для разрешения работы приемника необходимо инициализировать переменные ZDSTATE и RSTATE в памяти параметров.

Если бит POL = 0, то коммуникационный процессор не контролирует значение бита готовности R (Ready) в слове состояния дескриптора буфера при передаче. Если бит POL = 1, то при передаче контролируется значение бита готовности буфера.

При работе с HDLC-протоколом бит CRC определяет тип контрольной суммы. Если бит CRC = 0, то используется 16-битная CCITT-CRC контрольная сумма для данного канала. Если бит CRC = 1, то используется 32-битная CCITT-CRC контрольная сумма.

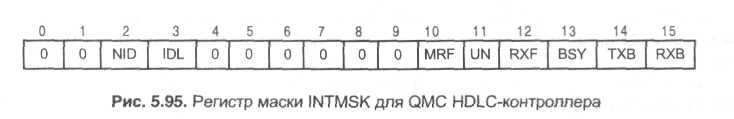

Все события, которые могут возникать при работе каналов, регистрируются в циклической очереди прерываний, в регистре событий (рис. 5.94). Для всех логических каналов существует один регистр маски. В регистре INTMSK (рис. 5.95) пользователь может при желании замаскировать прерывание от некоторых событий, если сбросит в «0» бит, соответствующий выбранному событию.

Работа с Transparent-протоколом. В табл. 5.61 приведено распределение канал-ориентированной памяти параметров при работе с протоколом Transparent.

Переменные TBASE и RBASE, TBPTR и RBPTR, ZISTATE и ZDSTATE, TSTATE и RSTATE имеют назначение, аналогичное одноименным переменным для QMC HDLC-протокола.

Бит MODE в регистре CHAMR (рис. 5.96) определяет протокол, с которым работает выбранный логический канал. Если MODE = 0, то канал работает с протоколом Transparent, если MODE = 1 - с HDLC-протоколом.

Бит RD определяет порядок передачи битов в байте. Если бит RD = 0, то в канал передается/принимается первым LSB-бит. Если бит RD = 1 , то первым передается или принимается MSB-бит.

Бит ENT = 1 разрешает работу передатчика, и во временной канал будут передаваться данные согласно выбранному протоколу. Если бит ЕМТ=0, то передатчик выключен, и если канал подключен к временному слоту, то в этот временной канал будут передаваться «1». Следует отметить, что отсутствует бит разрешения работы приемника с QMC-протоколом, но для разрешения работы приемника необходимо инициализировать переменные ZDSTATE и RSTATE в памяти параметров.

Если бит POL = 0, то коммуникационный процессор не контролирует значение бита готовности R (Ready) в слове состояния дескриптора буфера при передаче. Если бит POL = 1 , то при передаче контролируется значение бита готовности буфера.

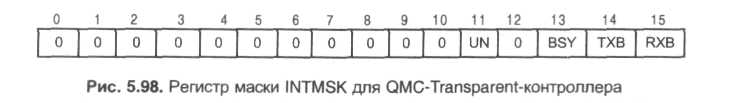

Все события, которые могут возникать при работе каналов, регистрируются в циклической очереди прерываний, в регистре событий (рис. 5.97). Для всех логических каналов существует один регистр маски. В регистре INTMSK (рис. 5.98) пользователь может при желании замаскировать прерывание от некоторых событий, если сбросит в «О» бит, соответствующий выбранному событию.

Рис. 5.96. Формат регистра режима CHAMR для QMC-Transparent-контроллера

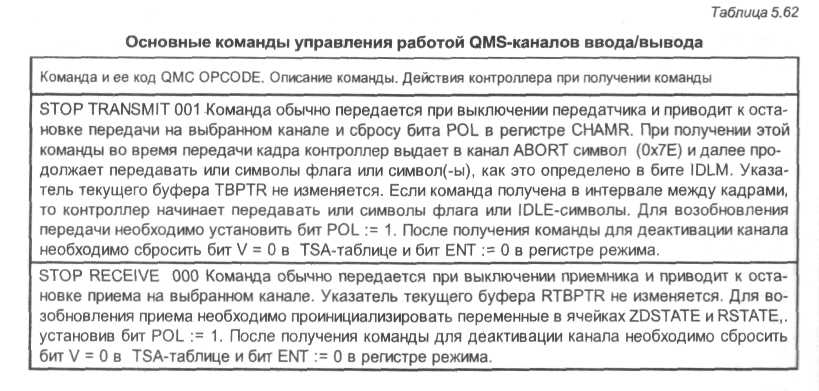

Основной набор команд представляет собой стандартные команды управления работой коммуникационного модуля (табл. 5.62). Обратите внимание, что отсутствуют команды запуска (start) приема и передачи, эти функции выполняются через регистр общих режимов GSMR.

Механизм обработки прерываний. При обработке прерываний используются регистр событий SCC-канала (рис. 5.100), который работает с QMC-протоколом, и циклическая таблица прерываний, к которой обращаются логические каналы при своей работе. Напоминаем, что сброс битов в регистре событий производится записью в соответствующий бит кода «1». При желании пользователь может замаскировать прерывание от отдельных событий, установив в «1» соответствующий бит в регистре маски SCCM.

Формат ячеек в таблице прерываний зависит от типа протокола, с которым работает канал, и был описан выше (см. рис. 5.94, 5.97). Переменная INTBASE указывает на расположение первой ячейки таблицы прерываний во внешней памяти контроллера. Переменная INTPTR указывает на текущую пустую ячейку в таблице, доступную для RISC-контроллера. Бит W = 1 (Wrap) в составе каждой ячейки отмечает последнюю ячейку таблицы прерываний. Таблица прерываний обрабатывается циклически - после обработки последней ячейки RISC-контроллер перейдет к обработке первой ячейки таблицы и произойдет переназначение указателя INTPTR := INTBASE.

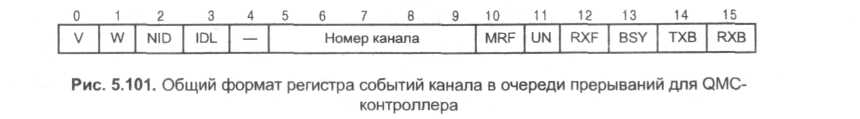

Когда один из QMC-каналов генерирует запрос на прерывание, то RISC-контроллер проверяет, маскировано это прерывание в регистре INTMSK или нет. Если прерывание не маскировано, то контроллер заполняет следующую свободную ячейку таблицы. Эта ячейка (рис. 5.101) содержит номер логического канала в поле «номер канала» и тип события, вызвавшего прерывание. Затем устанавливается бит V = 1 (Valid), который указывает, что данная ячейка используется и содержит флаги прерываний. Также увеличивается счетчик в ячейке INTPTR. После записи прерывания в таблицу QMC-контроллер устанавливает бит соответствующего прерывания в регистре событий SCCE SCC-контроллера. Если это прерывание RXF (прерывание, регистрирующееся после приема каждого кадра), то уменьшается счетчик GRFCNT, который контролирует, после приема скольких кадров будет выработано прерывание. Если этот счетчик не равен 0, то обработка прерывания прекращается. Если счетчик GRFCNT равен 0 или зарегистрировано другое прерывание, то в регистре событий используется дополнительный бит GINT, установка которого в «1» регистрирует, что в очереди на прерывание заполнена новая ячейка. После сброса бита GINT центральный процессор начинает обрабатывать очередь на прерывание. После чтения содержимого очередной ячейки таблицы процессор сбрасывает бит V := 0 и переходит к обработке следующей ячейки таблицы, и так продолжается, пока в таблице есть ячейки с установленным битом V = 1.

Если RISC-контроллер делает попытку записать данные о запросе на прерывание в ячейку, которая еще не обработана, т. е. у этой ячейки установлен бит V = 1, то регистрируется ошибка переполнения таблицы прерываний и в регистре событий устанавливается бит IQOV := 1. При возникновении этой ошибки данная ячейка таблицы немедленно программно сбрасывается и последнее прерывание теряется.

Бит NID (not idle) в ячейке таблицы устанавливается в «1», когда приемник получает данные, формат которых отличается от формата IDLE-символа. При работе с Transparent-протоколом N ID-прерывание не регистрируется.

Бит IDL используется при работе с HDLC-протоколом для регистрации приема IDLE-символа (0xFFFE). При работе с протоколом Transparent прерывание IDL не регистрируется.

Бит MRF устанавливается в «1» при работе с HDLC-протоколом, когда приемник принимает кадр, длина которого превышает максимальную длину, заданную в ячейке MFLR памяти параметров. При возникновении этой ошибки лишние байты кадра отбрасываются и не сохраняются в буфере памяти, в буферный дескриптор записывается длина полного кадра между двумя флагами и далее прием продолжается в обычном режиме. При работе с протоколом Transparent прерывание MRF не регистрируется.

При работе QMC-протокола регистрируются два типа глобальных ошибок, общих для всех каналов: ошибка незаполнения передатчика GUN (Global transmitting underrun), когда передача многобуферного кадра прекращается из-за неподготовленности очередных данных, и ошибка переполнения приемника GOV (Global receiver overrun), когда приемник не успевает принимать поступающие из сети данные. При возникновении ошибки GUN-контроллер передает во временной слот не менее 16 единиц, генерирует запрос на прерывание и устанавливает бит GUN в регистре событий SCCE SCC-канала, останавливает передачу данных во всех логических каналах и начинает передавать в канал или символы IDLE или символы FLAG в зависимости от типа используемого протокола. При возникновении ошибки GOV контроллер обновляет значение в ячейке RSTATE (бит 20 указывает, что прием остановлен), генерирует запрос на прерывание и устанавливает бит GOV в регистре событий SCCE SCC-канала, останавливает прием данных во все буферы всех каналов и ожидает, что центральный процессор сбросит в исходное состояние вначале ячейку ZDSTATE, а затем ячейку RSTATE.

Другой тип ошибок связан со скоростью передачи данных по SDMA-каналам внутри контроллера. Ошибка bus latency регистрируется, когда SDMA-контроллер не успевает освобождать FIFO приемника, и новые данные записываются в буфер поверх старых, что ведет к потере данных.

Такие же ошибки незаполнения (бит UN в ячейке таблицы прерываний) и переполнения могут быть зарегистрированы для каждого логического канала в отдельности с использованием ячейки таблицы прерываний. При возникновении ошибки незаполнения контроллер передает во временной слот не менее 16 единиц, генерирует запрос на прерывание и устанавливает бит UN в ячейке прерывания канала, останавливает передачу данных и начинает передавать в канал или символы IDLE или символы FLAG в зависимости от настройки регистра режима.

Бит RXF устанавливается в «1», если получен завершенный HDLC-кадр, он сохранен в памяти и обновлена информация в буферном дескрипторе. Далее декрементируется счетчик GRFCNT для генерации запроса на прерывание. Если во время приема кадра получена последовательность ABORT, состоящая минимум из семи единиц, буфер закрывается и устанавливаются биты RXB = RXF := 1 в регистре прерываний и бит АВ := 1 в слове состояния буферного дескриптора. При работе с протоколом Transparent прерывание RXF не регистрируется.

Если принят корректный кадр данных, но нет буферов для его сохранения, то регистрируется событие переполнения приемника, формируется условие занятости (busy condition) и устанавливается бит BSY := 1. После этого приемник выключается и прекращает прием данных.

Если текущий буфер данных успешно передан, то регистрируется событие и устанавливается бит ТХВ := 1. Но этот бит устанавливается, а прерывание генерируется только после того, как в FIFO-буфер передатчика будет записано заданное количество символов PAD или будет записан один закрывающий флаг, если в слове состояния дескриптора бит PAD = 0. Таким образом, время начала ТХВ-прерывания зависит от времени передачи закрывающего флага на линию TXD.

При получении по сети полного буфера данных устанавливается бит события RXB := 1.

Инициализация QMC-контроллера.

Проинициализировать регистр настройки последовательного интерфейса SIMODE. Установить нормальный режим работы (биты SDMx:=00), выключить механизм grant (бит GMx := 0) и сбросить бит STZx := 0. Остальные биты - SMCx, SMCxCS, RFSDx, DSCx, CRTx, CEx, FEx и TFSDx - устанавливаются в соответствии с системными установками для выбранного основного коммуникационного протокола. Обычно устанавливают CRTa = RFSDa = TFSDa := 1, включая общую синхронизацию для приемника и передат чика с задержкой в 1 бит при обработке кадра.

Проинициализировать регистр синхронизации последовательного интерфейса SICR. Сбросить бит GRx := 0, выключив механизм подтверждений (grant), и установить бит SCx := 1, подключив канал к SCCx мультиплексору TSA. Так как SCC-канал будет рабо тать в мультиплексируемом режиме, также требуется установить биты RxCSx и TxCSx, выбрав источник тактирования для приемника и передатчика канала.

Сконфигурировать выводы параллельного порта А для работы с сигналами интер фейсов TDMa или TDMb: LITXDx (передача данных), MRXDx (прием данных), LITCLKx тактовый сигнал передатчика), LIRCLKx (тактовый сигнал приемника). Например, про- инициализировать регистры порта A: PAPAR := 0xA5F0 и PADIR := Ox00F0.

Сконфигурировать выводы параллельного порта В для работы с выходным сигна лом тактового генератора LICLKOx интерфейсов TDMa или TDMb, а также с выходными зтробирующими сигналами L1ST1-L1ST4. Например, проинициализировать регистры порта В: PBPAR := 0xFС00 и PBDIR := 0х0С00.

Сконфигурировать выводы параллельного порта С для работы с сигналами интер фейсов TDMa или TDMb: LITSYNCx и URSYNCx (внешние стробы начала кадров при передаче и приеме), L1ST1-L1ST4 (выходные строб-сигналы для тактирования пери ферийных устройств). Например, проинициализировать регистры порта С: PCPAR := := 0x0F0F и PCDIR := 0x000F.

Записать исходные значения в ячейки памяти маршрутизации SI RAM, определив, какие временные слоты и какими SCC-каналами будут обрабатываться. Например, если каждый байтовый временной канал будет обрабатываться SCC1-контроллером, то ячей ки приемника программируются: SIRAM[0] := 0x0042... SIRAM[n-1]:- 0x0042, SIRAM[n] := := 0x0043 (в последней ячейке дополнительно устанавливается бит Last = 1), а ячейки передатчика: SIRAM[32] := 0x0042... SIRAM[32+n-1] := 0x0042, SIRAM[32+n] := 0x0043.

В регистре общих режимов памяти маршрутизации SIGMR установить бит Епх := 1, выбрав, какой канал - TDMa или TDMb - будет использоваться для обмена, а также установить биты RDM, выбрав режим работы памяти маршрутизации. Например, SIGMR := := ОхОЕ. Таким образом, выбран режим работы обоих - TDMa- и TDMb-каналов, каж дый работает с 32 (64)-ячейками для приема и передачи и без теневой памяти.

Если во время работы необходимо перенастраивать память маршрутизации, то требуется использовать теневую память. Настройка режимов работы основной и тене вой памяти производится в регистре команд Sl-интерфейса SICMR. Если SICMR = 0x00, то работает основная память, а если SICMR = 0xF0, то работает теневая память на обоих TDM-каналах.

Произвести настройку регистра общих режимов выбранных SCC-каналов GSMR_H. Выключить Transparent-режим обмена (биты TRX = ТТХ = TCRC = RSYN := 0), включить режим распознавания импульса сигналов со и cts (биты CDP = СТСР = CDS = CTSS := 1), выключить режим инвертирования данных (бит REVD := 0), при необходимости опреде лить полярность сигнала InfraRed (бит IRP) и включить схему распознавания паразитных перепадов на линиях тактового сигнала (бит GDE), установить нормальную длину буфе ра FIFO передатчика (бит TFL := 0), установить размер ячейки буфера FIFO приемника в 32 бита (бит RFW := 0), выключить взаимную синхронизацию приемника и передатчика (бит TXSY := 0), синхронизация будет производиться от внешнего сигнала (бит SYNL := 00), между кадрами данных в канал будут передаваться IDLE-символы (бит RTSM := 0). Обычно устанавливается GSMRH := 0x00000780.

10.Произвести настройку регистра общих режимов выбранных SCC-каналов GSMR_L. При необходимости установить способ кодирования сигнала для InfraRed протокола (бит SIR), сигналы будут анализироваться по обоим фронтам тактового сигнала (бит EDGE := 00), тактовый сигнал передатчика не инвертируется (бит TCI := 0), несущая частота всегда присутствует в канале (бит TSNC := 00), блок DPLL не инвертирует данные (биты RINV = = TINV := 0) и выполняет NRZ-кодирование (биты RENC = TENC := 000), внутреннее увеличение частоты тактового сигнала не производится (биты TDCR = RDCR := 000), пассивное состояние линии «1» (бит TEND := 0), преамбула не используется (биты TPL = = ТРР := 000), приемник и передатчик пока выключены (биты ENT = ENR := 0), выбран режим работы с QMC-протоколом (биты MODE := 1010), диагностический режим работы

устанавливается в соответствии с требованиями пользователя (бит DIAG). Обычно устанавливается GSMRJ- := 0х0000000А.

Для работы с QMC-протоколом проинициализировать основные общие парамет ры каналов: указатель на таблицу буферных дескрипторов MCBASE, указатель на табли цу прерываний INTBASE, при работе с HDLC-протоколом установить максимальный раз мер приемного буфера MRBLR (рекомендованное значение должно быть больше 30 байт и кратно 4 байтам), установить значение «прерывания после приема» GRFTHR кадров (обычно GRFTHR := 1), установить значение счетчика принятых кадров GRFCNT (обыч но GRFCNT := GRFTHR), для работы с 32-разрядной контрольной суммой записать зна чение константы C_MASK32 := 0xDEBB20E3, а при работе с 16-разрядной контрольной суммой - C_MASK16 := 0xF0B8.

Скопировать значение ячейки INTBASE в ячейку указателя на пустой элемент таб лицы прерываний INTPTR := INTBASE.

Проинициализировать TSA-таблицы TSATTx и TSATRx. Во всех рабочих ячейках установить бит V := 1, а также сбросить бит W := 0 во всех ячейках, кроме последней. Для работы со всеми восемью битами канала установить биты маски, равные OxFF. Устано вить требуемое значение указателя на таблицу канал-ориентированной памяти пара метров (channel pointer).

Проинициализировать значения указателей Tx_S_PTR и Rx_S_PTR, а также значе ния указателей на ячейку текущего временного слота TxPTR и RxPTR. Обычно в указатели Tx_S_PTR = TxPTR записывается стартовый адрес TSA-таблицы передатчика, а в указате ли Rx_S_PTR = RxPTR - стартовый адрес TSA-таблицы приемника. Если используется общая TSA-таблица, то во все ячейки указателей заносится значение MCBASE+0x20.

Установить значение переменной внутреннего состояния QMCSTATE := 0x8000.

Проинициализировать ячейки протокол-ориентированной памяти параметров каж дого логического канала для работы с выбранным коммуникационным протоколом (HDLC или Transparent). Для каждого используемого логического канала записать в их ячейки TBASE и RBASE стартовые адреса таблиц буферов дескрипторов каналов при передаче и приеме (напоминаем, что при работе стартовые адреса таблиц дескрипторов рассчи тываются как MCBASE+TBASE или MCBASE+RBASE). Проинициализировать значения указателей на таблицу дескрипторов RBPTR := RBASE и TBPTR := TBASE. Установить значение внутренних переменных состояния передатчика TSTATE := 0x30000000 для МРС860МН и приемника RSTATE := 0x31000000 для МРС860МН. Установить начальные значения в ячейки ZISTATE := 0x00000100, ZDSTATE := 0x80 для HDLC-протокола и ZDSTATE := 0x18000080 для Transparent-протокола. Разрешить прерывание от требуе мых событий, записав соответствующее значение в ячейку INTMSK, например, разре шить все прерывания INTMSK := 0хА. При работе с HDLC-протоколом установить макси мальный размер кадра данных MFLR, а для Transparent-протокола установить макси мальный размер приемного буфера TMRBLR (рекомендованное значение должно быть больше 30 байт и кратно 4 байтам). При работе с Transparent-протоколом также следует определить значение в регистре контроля синхронизации TRNSYNC.

Подготовить буферы и буферные дескрипторы приемника для каждого использу емого логического канала. Буферные дескрипторы должны располагаться в памяти по адресу RBASE. В их слове состояния рекомендуется установить бит готовности Е := 1, установить бит прерывания I := 1, а в последнем дескрипторе таблицы требуется устано вить бит W := 1.

Подготовить буферы и буферные дескрипторы передатчика для каждого исполь зуемого логического канала. Буферные дескрипторы должны располагаться в памяти по адресу TBASE. В их слове состояния рекомендуется установить бит готовности R := 1, установить бит прерывания I := 1, а в последнем дескрипторе таблицы требуется устано вить бит W := 1.

Проинициализировать таблицу прерываний. Если прерывания будут использо ваться, то для каждой ячейки таблицы рекомендуется сбросить биты V := W := 0, и только у последней ячейки таблицы бит W := 1.

Для каждого логического канала проинициализировать регистр режима CHAMR, выполнив настройку на работу или с HDLC-протоколом или с протоколом Transparent. Бит включения передатчика пока сброшен (ENT := 0), его необходимо установить только тогда, когда канал будет готов к передаче. Например, настроим канал для работы с HDLC- протоколом CHAMR := 0x9187.

Проинициализировать регистр событий SCCE для выбранного SCCx-канала. Сброс битов в регистре производится записью в соответствующие разряды кода «1» SCCE := OxF.

Проинициализировать регистр маски SCCM для выбранного SCCx-канала. Чтобы разрешить прерывание от всех событий, рекомендуется записать в регистр код 0xF. Для выбранного SCCx-канала в регистре контроллера прерывания CIMR в соответствующий бит требуется записать «1», чтобы разрешить регистрацию запросов на прерывание от этого канала.

В регистре режимов GSMRJ. SCCx-канала разрешить работу приемника и пере датчика, установив биты ENT := ENR := 1.

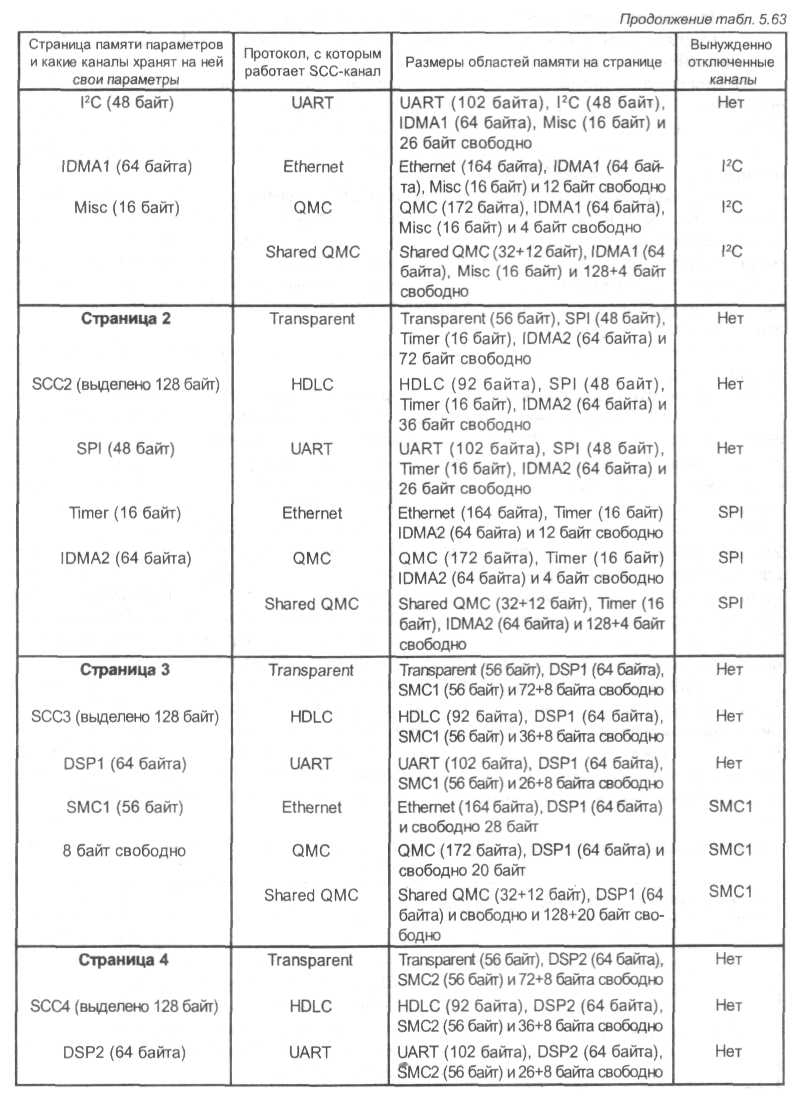

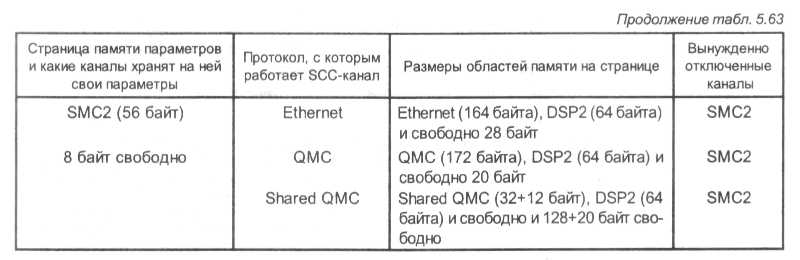

Особенности распределение памяти параметров для QMC-протокола. В контроллере МС860МН для поддержки 64-каналов требуется 4 Кбайт внутренней памяти (64 х 64 байта = 4096 байт). Если QMC-протокол использует для хранения буферных дескрипторов внешнюю память, то никаких конфликтов между одновременно работающими протоколами нет, и буферные дескрипторы других протоколов могут располагаться во внутренней памяти. Если используются все 64 канала, то для параметров других протоколов остальных каналов ввода/вывода в памяти параметров осталось только 4 страницы по 256 байт каждая. Первая страница содержит параметры канала SCC1, I2C, IDMA1 и параметр miscellaneous. Вторая - параметры канала SCC2, SPI, RISC-таймеров и SPI-ка-нала. Третья страница содержит параметры каналов SCC3, SMC1 и параметры DSP1-операций. Четвертая - параметры каналов SCC4, SMC2 и параметры О8Р2-операций. Из-за конфликта в распределении памяти невозможно одновременное использование некоторых коммуникационных протоколов, каналов или функций.

Если QMC-канал обрабатывается несколькими SCC-каналами (Shared QMC), то каждому SCC-контроллеру требуется 170 байт для хранения глобальных параметров и таблицы маршрутизации, а также для хранения TSA-таблиц приема и передачи (128 байт). Но SCC-каналы могут использовать общие TSA-таблицы, и тогда для одного SCC-кана-ла требуется 172 байта (44 байта для регистров и 128 байт для общей TSA-таблицы), а другим SCC-каналам потребуется только 44 байта для хранения регистров (табл. 5.63).

Применение контроллеров. В табл. 5.64 приведены наиболее распространенные варианты конфигурации контроллеров МРС860МН.

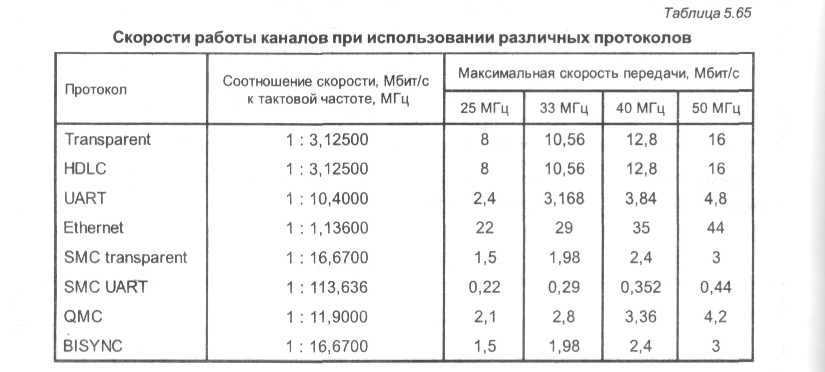

В табл. 5.65 приведены максимальные скорости передачи контроллеров при использовании различных коммуникационных протоколов в режиме полнодуплексной передачи.

По материалам вышеприведенных таблиц легко рассчитать коэффициент загрузки коммуникационного процессора или сколько процентов полосы пропускания контроллеpa будет занято коммуникационными протоколами. Коэффициент загрузки рассчитывается как сумма для всех каналов отношений скорости работы канала к максимальной скорости работы канала. Если коэффициент оказывается больше единицы, то такая конфигурация работы системы невозможна. Рассмотрим примеры.

Пример 1. Рассчитаем коэффициент загрузки для контроллера с частотой 25 МГц, в котором канал SCC1 работает в режиме полудуплекса с 10-Мбит/с Ethernet-протоколом, SCC2 работает с 2-Мбит/с HDLC-протоколом, SCC3 работает с 64-Кбит/с HDLC-протоколом, SCC4 работает с 9,6-Кбит/с UART-протоколом, SMC1 работает с 38-Кбит/с UART-протоколом. Коэффициент равен (10/22) + (2/8) + + (0,064/2,4) + (0,0096/2,4) + (0,038/0,22) = 0,96 < 1. Таким образом, коммуникационный процессор будет загружен на 96%.

Пример 2. Рассчитаем коэффициент загрузки для контроллера с частотой 25 МГц, в котором реализованы двадцать четыре 64-Кбит/с QMC-канала и два 128-Кбит/с HDLC-канала. Коэффициент равен (24x0,064/2,1) + (2x0,128/8) = 0,76 < 1. Таким образом, коммуникационный процессор будет загружен на 76%.

Пример 3. Рассчитаем коэффициент загрузки для контроллера с частотой 25 МГц, в котором реализованы тридцать два 64-Кбит/с QMC-канала и один 2-Мбит/с HDLC-канал. Коэффициент равен (32x0,064/2,1) + (2/8) = 1,22 > 1. Таким образом, коммуникационный процессор будет загружен на 122% и работать не будет.