- •Билет №1. Интерфейс связи клавиатуры с персональным компьютером. Временная диаграмма передачи данных от клавиатуры в системный блок пк.

- •Билет №2. Основные этапы выполнения программы прерывания int 9 (ввод данных из клавиатуры)

- •Билет № 3. Назначение контроллера клавиатуры пк. (Основные функции и основные узлы)

- •Билет №4; Билет №7 Назначение lpt-порта и его регистров

- •Билет №5. Физическая реализация интерфейса Centronics. Назначение линий интерфейса

- •Билет №6. Назначение и организация интерфейса rs 232-с. Суть асинхронного режима передачи по интерфейсу

- •Билет № 8. Назначение кэш-памяти винчестера (вместо этого «Контроллер hdd»)

- •Билет № 9. Назначение узла ramd ac видеоадаптера

- •Билет № 10. Архитектура шины usb

- •Билеты № 11, 25 Назначение сигналов внешнего интерфейса rs-232c

- •Билет № 12. Перечислите классификационные характеристики стандартных интерфейсов пк

- •Билет № 13.

- •Интерфейс isa-8

- •Билет № 14. Билет№ 21. Связь контроллера fdd с накопителем. Назначение сигналов интерфейса с накопителем Физическая реализация интерфейса накопителя fdd

- •Билет № 15. Организация видеопамяти видеоадаптера в текстовом и графическом режимах

- •Билет № 16. Назначение карты agp. Какие компоненты пк соединяет интерфейс agp?

- •Видеопамять

- •Билет № 17. Назовите назначение управляющих сигналов ras#, cas#, we#, поступающих в банки памяти пк

- •Билет № 18. Программа прерывания int 16h (поддержка клавиатуры). Операции программы

- •Билет № 19. Модули (биСы), выполняющие системные функции в пк. Назначение

- •Билет № 20. Последовательность пакетов при вводе-выводе по usb

- •А) вывод данных

- •Билет № 22. Контроллер fdd. Назначение. Регистры контроллера

- •Билет № 23. Временная диаграмма передачи данных по интерфейсу “Centronics”. Поясните по диаграмме процесс передачи данных

- •Билет №24 Драйвер (программа обслуживания) внешнего последовательного интерфейса rs 323-c. Операции и их назначение

Билет № 3. Назначение контроллера клавиатуры пк. (Основные функции и основные узлы)

С CPU ПК клавиатура взаимодействует через контроллер клавиатуры.

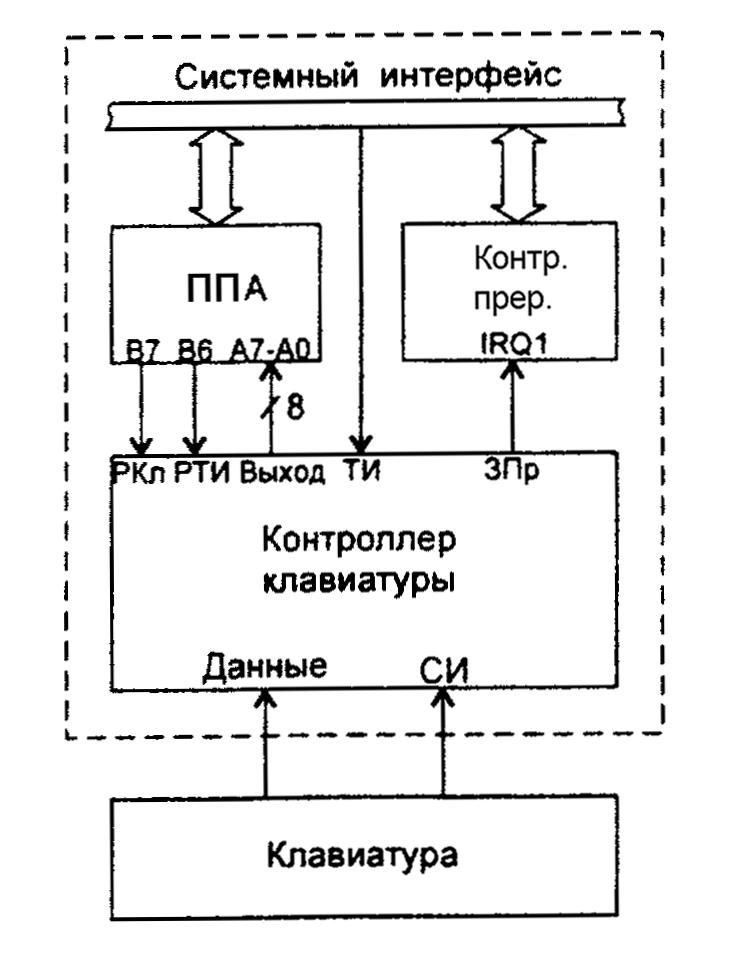

На рис. 3.3 приведена блок-схема подсоединения клавиатуры к системному интерфейсу. Контроллер клавиатуры предназначен для преобразования последовательно поступающего из клавиатуры значения скэн-кода в параллельный формат и формирования сигнала прерывания при наличии готовых для передачи в ЦПБ данных.

Данные в параллельном формате передаются программируемому параллельному интерфейсу 8255А в порт А, из которого поступают в CPU. Через биты В6 и В7 порта В этого интерфейса CPU передает в контроллер клавиатуры управляющие сигналы, которые предназначены для блокировки процессором связи с клавиатурой. Сигнал по В6 блокирует передачу синхронизирующих импульсов, а сигнал по В7 служит для блокировки передачи данных. Сигнал запроса прерывания с клавиатуры (ЗПр.) поступает в контроллер прерываний 8259А на вход IR1. Тактовые сигналы СLК от задающего генератора ПК поступают в контроллер клавиатуры для синхронизации работы CPU со входом от клавиатуры.

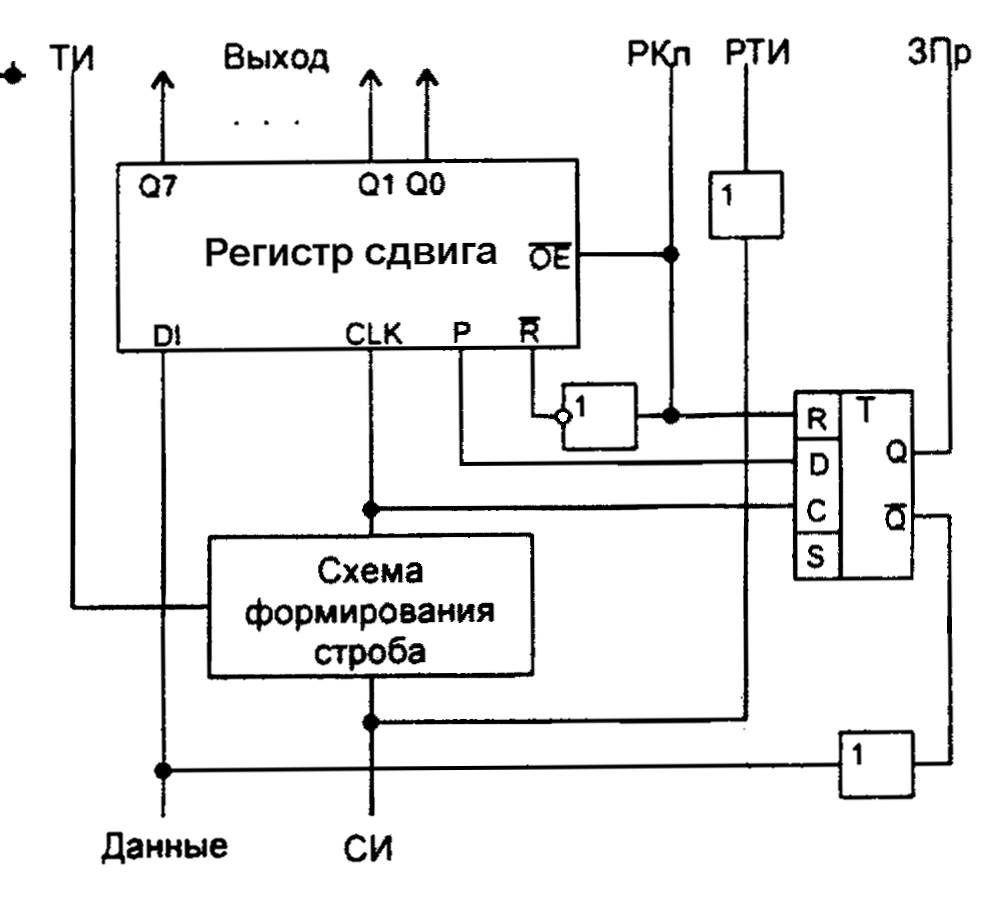

Блок-схема контроллера клавиатуры приведена на рис. 3.4. Основными элементами схемы контроллера клавиатуры являются: регистр сдвига, схема формирования строба и D-триггер. При передаче информации от клавиатуры в контроллер данные в последовательном коде поступают на вход DI регистра сдвига. Сдвиг в этом регистре происходит при подаче импульса из схемы формирования строба. Этот импульс формируется при наличии синхроимпульсов от клавиатуры и тактовых импульсов СLК.

При поступлении в контроллер клавиатуры очередного скэн-кода первый маркерный бит всегда равен "1". Его появление на выходе Р регистра сдвига свидетельствует об окончании преобразования этого скэн-кода, т.е. о наличии на выходе регистра данных для передачи в CPU. Этот сигнал подается на вход D-триггера, который изменяет свое состояние, формируя сигнал запроса на прерывание в БИС 8259А.

При необходимости CPU может заблокировать передачу данных с клавиатуры в контроллер путем подачи управляющих сигналов через биты В6 и В7 порта В БИС 8255А.

Рис. 3.3. Блок-схема соединения клавиатуры с системным интерфейсом

Рис. 3.4. Блок-схема контроллера клавиатуры

Билет №4; Билет №7 Назначение lpt-порта и его регистров

Блок-схема контроллера интерфейса приведена на рис. 2.9. Структура контроллера представляет собой типичную регистровую структуру. Центральный процессор ПК может адресоваться к трем регистрам контроллера:регистру данных; регистру управления; регистру состояния ПУ. Адреса этих регистров для ПК имеют стандартные значения: 378h, 379h и 37Ah - для LPT1; 278h, 279h и 27Ah - для LPT2; 3ВСh, 3ВDh и 3ВEh - для LPT3.

Centronics. Код, выводимый на интерфейс, фиксируется в регистре чтения данных, и его можно прочитать для контроля передаваемых данных. Первые адреса называются базовыми адресами портов. Область данных BIOS содержит базовые адреса для каждого контроллера. Базовый адрес для LPT1 находится в ячейке 0040:0008, для LPT2 – 0040:000А, для LPT3 – 0040:000С. При инициализации ПК базовому адресу присваивается значение 0, когда соответствующий порт не установлен.

Управление передачей информации по интерфейсу организуется в соответствии с временными диаграммами работы интерфейса Centronics, приведенными на рис. 2.8. Чере регистр данных CPU посылает код данных в параллельном формате в ПУ по линиям D0-D7 интерфейса.

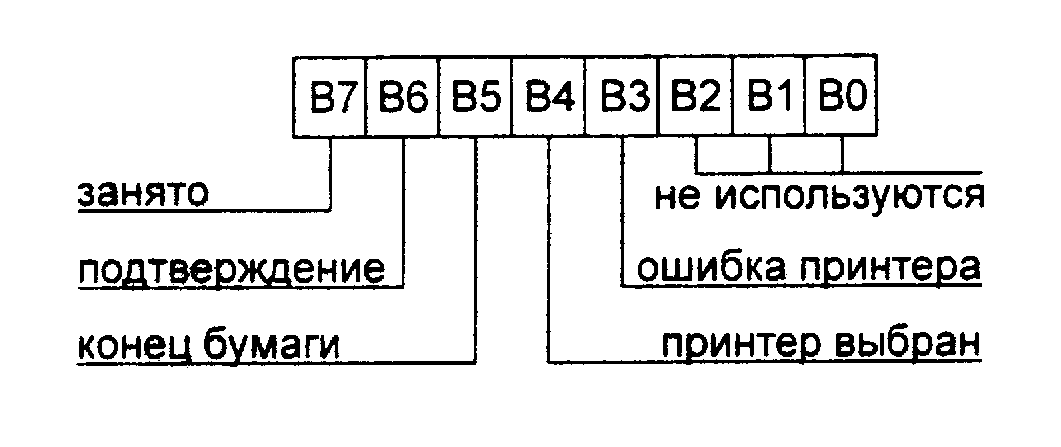

Регистр состояния ПУ содержит информацию о ПУ. Значения битов этого регистра приведены на рис. 2.10. CPU при передаче данных в ПУ опрашивает регистр состояния ПУ, чтобы определить момент, когда ПУ готово к приему, и можно посылать данные. Этот момент определяется соотношением сигналов BUSY (занято) и #ACK (подтверждение). Регистр состояния сообщает также, что произошла ошибка в работе ПУ или что ПУ не готово из-за отсутствия бумаги (при работе с принтером).

Через регистр управления в ПУ передаются сигналы инициализации ПУ (#INIT), управления выводом данных (#STROBE), т другие сигналы управления. Семантика битов этого регистра приведена на рис. 2.11. Установкой бита В4 в единичное состояние CPU переводит контроллер интерфейса в режим передачи данных по прерыванию. В этом режиме, когда ПУ готово к приему очередного кода данных, контроллер интерфейса посылает запрос на прерывание. Однако передача данных в ПУ в режиме прерывания практически не используется.

Рис. 2.9. Структура контроллера интерфейса Centronics

Формат регистра состояния LPT-порта

Бит В7 – инверсное отображение сигнала BUSY на линии интерфейса.

Бит В6 – отображение сигнала на линии #ACK.

Бит В5 – отображение сигнала на линии PE.

Бит В4 - отображение сигнала на линии SELECT.

Бит В3 - отображение сигнала на линии #ERROR.

Биты В2-В0 не используются.

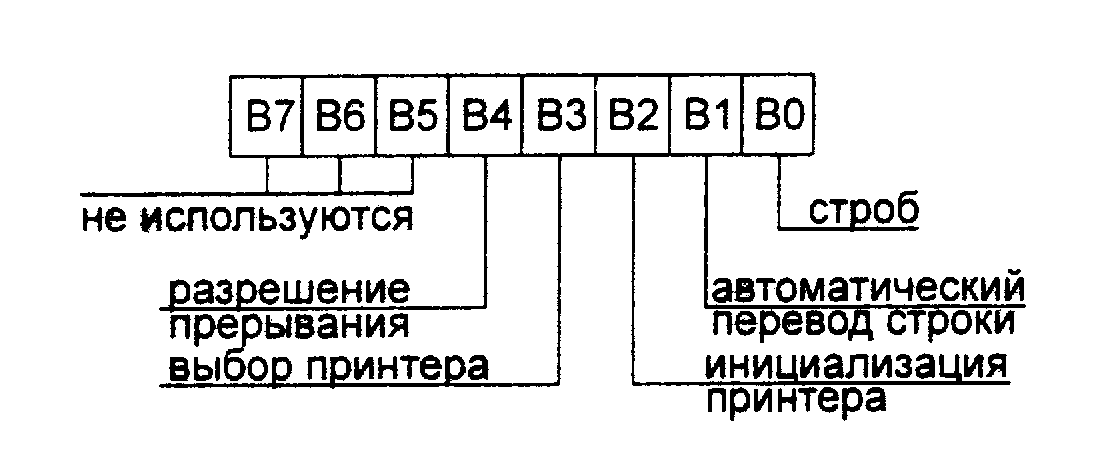

Назначение битов регистра управления LPT – порта:

биты В7-В5 не используются;

бит В4 – единичное значение разрешает прерывание по спаду сигнала на линии #ACK – сигнал запроса следующего байта;.

бит В3 – “1” формирует низкий активный уровень сигнала #SLCT IN;

бит В2 – “0” формирует низкий активный уровень сигнала #INIT;

бит В1 – “1” формирует низкий активный уровень сигнала #AUTO FD;

бит В0 – “1” формирует низкий активный уровень сигнала #STROBE;

Рис. 2.11. Формат регистра управления