- •Билет №1. Интерфейс связи клавиатуры с персональным компьютером. Временная диаграмма передачи данных от клавиатуры в системный блок пк.

- •Билет №2. Основные этапы выполнения программы прерывания int 9 (ввод данных из клавиатуры)

- •Билет № 3. Назначение контроллера клавиатуры пк. (Основные функции и основные узлы)

- •Билет №4; Билет №7 Назначение lpt-порта и его регистров

- •Билет №5. Физическая реализация интерфейса Centronics. Назначение линий интерфейса

- •Билет №6. Назначение и организация интерфейса rs 232-с. Суть асинхронного режима передачи по интерфейсу

- •Билет № 8. Назначение кэш-памяти винчестера (вместо этого «Контроллер hdd»)

- •Билет № 9. Назначение узла ramd ac видеоадаптера

- •Билет № 10. Архитектура шины usb

- •Билеты № 11, 25 Назначение сигналов внешнего интерфейса rs-232c

- •Билет № 12. Перечислите классификационные характеристики стандартных интерфейсов пк

- •Билет № 13.

- •Интерфейс isa-8

- •Билет № 14. Билет№ 21. Связь контроллера fdd с накопителем. Назначение сигналов интерфейса с накопителем Физическая реализация интерфейса накопителя fdd

- •Билет № 15. Организация видеопамяти видеоадаптера в текстовом и графическом режимах

- •Билет № 16. Назначение карты agp. Какие компоненты пк соединяет интерфейс agp?

- •Видеопамять

- •Билет № 17. Назовите назначение управляющих сигналов ras#, cas#, we#, поступающих в банки памяти пк

- •Билет № 18. Программа прерывания int 16h (поддержка клавиатуры). Операции программы

- •Билет № 19. Модули (биСы), выполняющие системные функции в пк. Назначение

- •Билет № 20. Последовательность пакетов при вводе-выводе по usb

- •А) вывод данных

- •Билет № 22. Контроллер fdd. Назначение. Регистры контроллера

- •Билет № 23. Временная диаграмма передачи данных по интерфейсу “Centronics”. Поясните по диаграмме процесс передачи данных

- •Билет №24 Драйвер (программа обслуживания) внешнего последовательного интерфейса rs 323-c. Операции и их назначение

Графический

сопроцессор

ЗГ

Контро-

ллер

ЭЛТВидеопамять

VS

GS

Графический контроллер

CLK

Интерфейс АGP

Рис.4.3. Блок-схема видеоадаптера AGP

CPU

North

bridge

Порт АGP

Память

Шина

АGP

Шина PCI

Рис.4.4. Технология AGP

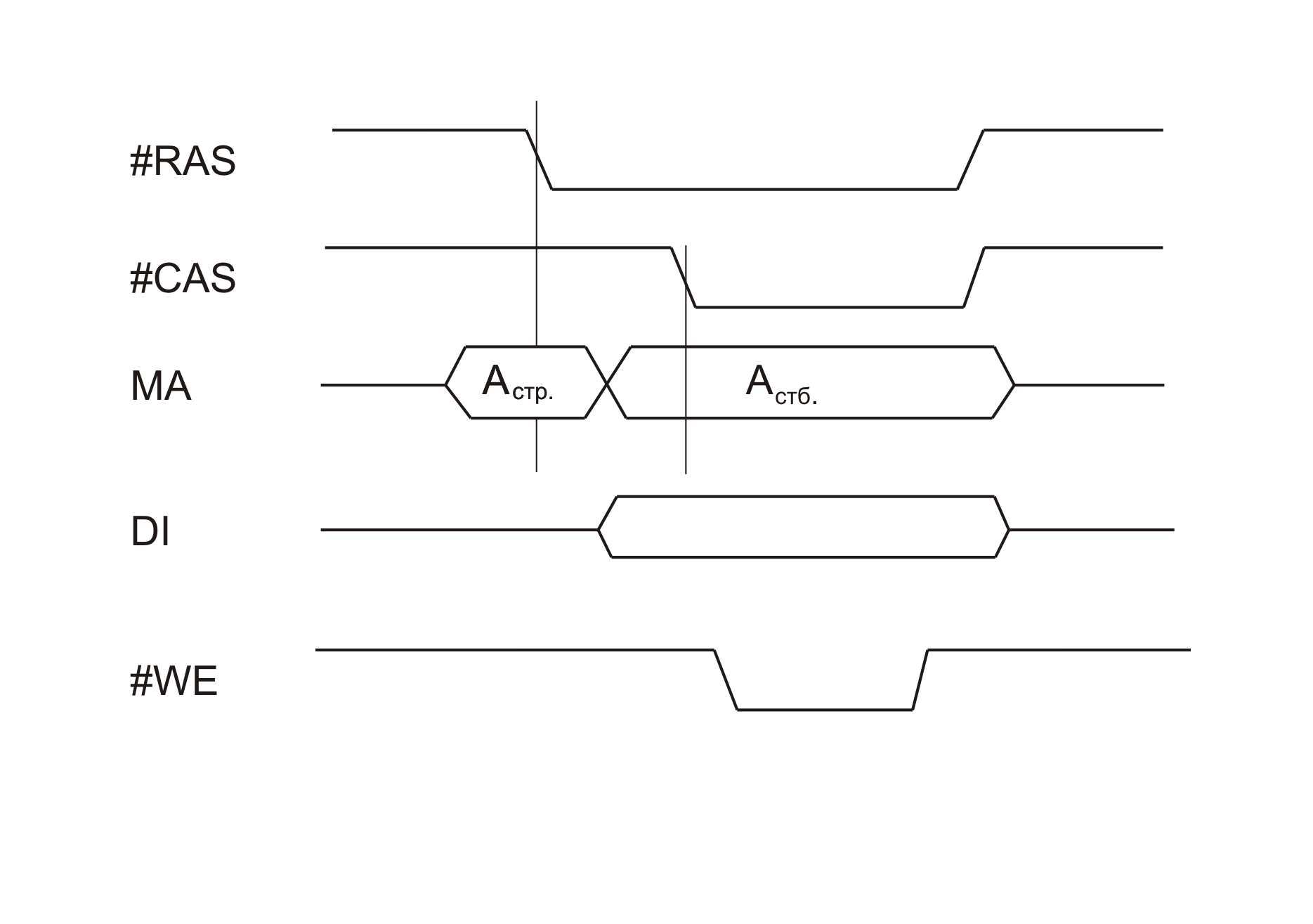

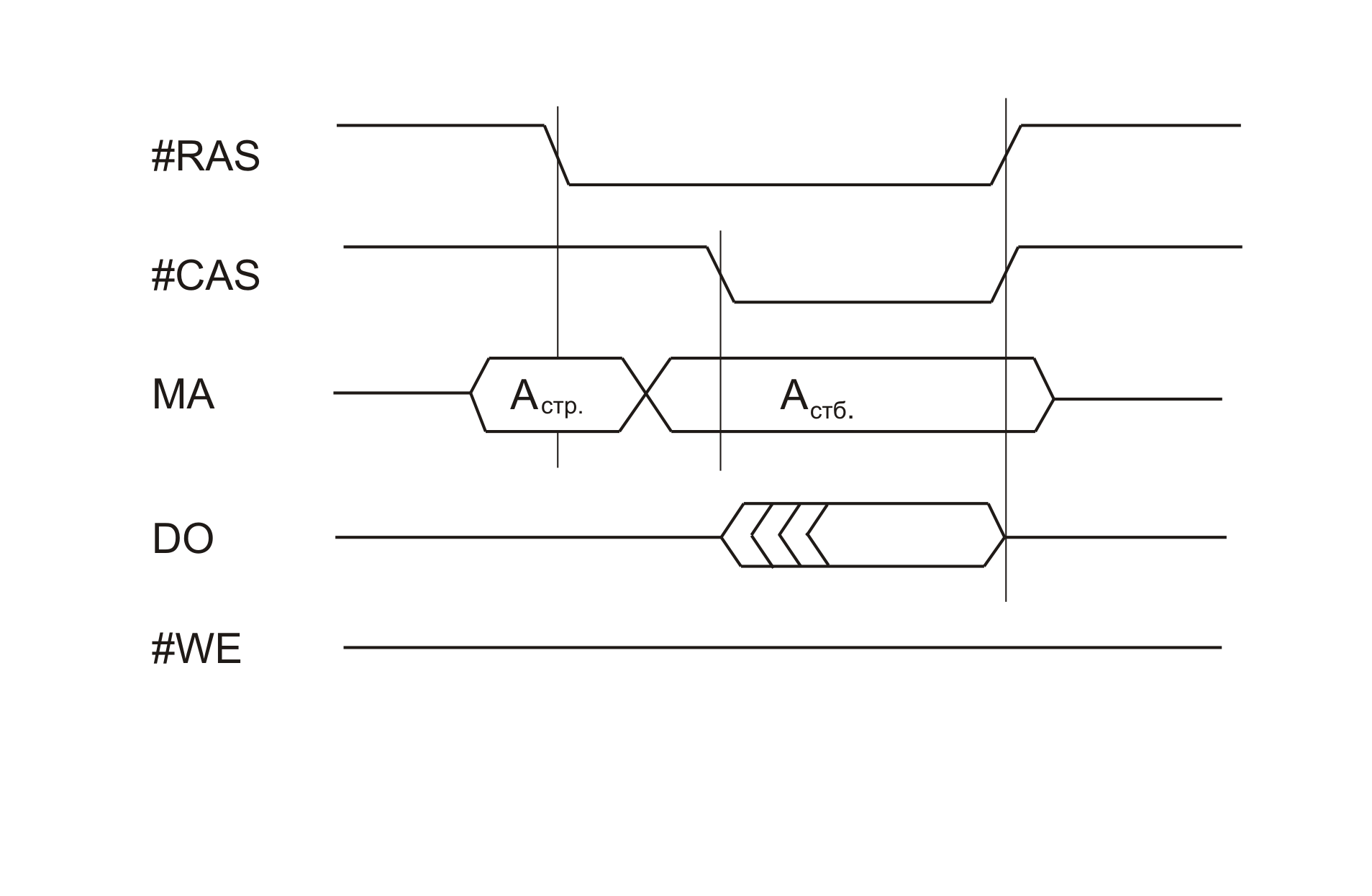

Билет № 17. Назовите назначение управляющих сигналов ras#, cas#, we#, поступающих в банки памяти пк

Обычно в микросхемах памяти типа DRAM хранится 1 бит информации. Матрица битов представляет собой решетку, состоящую из строк и столбцов, на пересечении которых находится элемент для хранения бита информации. Адреса строки и столбца передаются по мультиплексированной шине адреса МА и подаются на адресные входы микросхемы DRAM с разделением во времени. Сначала подается адрес строки (младшие разряды адреса), затем на те же входы микросхемы подается адрес столбца (старшие разряды адреса).

Если в одной микросхеме содержится одна матрица, то она хранит 1 бит информации. Поэтому, для хранения 1 байта данных устанавливается 8 таких микросхем. Для повышения скорости обмена данными между CPU и памятью были разработаны микросхемы типа DRAM, имеющие 4, 8, 16 одинаковых матриц ячеек памяти. Соответственно число входов для данных увеличилось до четырех, восьми, шестнадцати, а информация в таких микросхемах хранится уже не побитно, а побайтно. Назначение сигналов микросхем динамической памяти приведено в табл. 1.1.

Таблица 1.1. Сигналы микросхем динамической памяти

_Сигнал Назначение___ ___________________________________

# RAS Row Access Strobe – строб выборки адреса строки.

По спаду сигнала начинается любой цикл обращения;

низкий уровень сохраняется на все время цикла.

Адрес строки фиксируется по фронту сигнала # RAS.

#CAS Column Access Strobe - строб выборки адреса столбца.

По спаду сигнала начинается цикл записи или чтения.

Адрес столбца фиксируется по фронту сигнала #CAS.

МАi Multiplexed Address – мультиплексированные линии

адреса.

#WE Write Enable – разрешение записи. Данные записываются

в выбранную ячейку по спаду сигнала #WE при низком

уровне сигнала #CAS.

DI Data Input – входные данные (только для микросхем с

однобитной организацией.

DO Data Output – выходные данные (только для микросхем с

однобитной организацией. Выходные буферы микросхем

DRAM открыты только при сочетании низкого уровня

сигналов # RAS, #CAS и высокого уровня сигнала #WE.

DQx Data Bit – объединенные внутри микросхемы входные и

выходные сигналы данных (для микросхем с многобит-

ной организацией).

Выбранной микросхемой памяти является та, на которую во время действия сигнала низкого уровня # RAS приходит активный сигнал #CAS. Тип обращения определяется сигналом #WE. Временные диаграммы циклов записи и чтения приведены на рис. 1.2. Адреса строки и столбца стробируются по спаду импульсов #RAS и #CAS.

а)

б)

Рис. 1.2. Временные диаграммы: а)записи; б) чтения

динамической памяти