- •Тригери

- •1. Визначення та призначення тригерів

- •2. Класифікація тригерів

- •3. Таблиця переходів і логічні рівняння rs-тригерів

- •3.1. Асинхронний rs-тригер з прямими входами

- •3.2. Асинхронний rs-тригер з інверсними входами

- •3.3. Синхронний rs-тригер на елементах або-не

- •Синхронний rs-тригер на елементах і-не

- •4. Тригери типів jk, t та d

- •4.1. Таблиця переходів і логічне рівняння jk -тригера

- •4.2. Таблиця переходів і логічне рівняння т-тригера

- •4.3. Таблиця переходів і логічне рівняння d-тригера

4.2. Таблиця переходів і логічне рівняння т-тригера

Тригером типу Т називається запам’ятовуючий елемент з двома стійкими станами та одним інформаційним Т-входом. Стан Т-тригера змінюється на протилежний після кожного надходження лічильного сигналу на Т-вхід. Логіка функціонування асинхронного лічильного тригера подана таблицею переходів табл.2 і описується логічним рівнянням:

![]() . (9)

. (9)

Для побудови асинхронного Т-тригера на елементах І-НЕ рівняння (9) перетворимо до вигляду, зручному для реалізації у заданому елементному базисі:

![]() . (10)

. (10)

У

Таблиця

0

0

0

0

1

1

1

0

1

1

1

0

![]()

![]() .

Перемикання тригера визначається

сумісною дією лічильних сигналів ‘Т’

і зворотного зв’язку виходів

і

.

Схема Т-тригера та результати моделювання

наведено на рис. 10.

.

Перемикання тригера визначається

сумісною дією лічильних сигналів ‘Т’

і зворотного зв’язку виходів

і

.

Схема Т-тригера та результати моделювання

наведено на рис. 10.

Рис. 10

4.3. Таблиця переходів і логічне рівняння d-тригера

Тригером типу D називається синхронний запам’ятовуючий елемент з двома стійкими станами та одним інформаційним D-входом. Логіка функціонування D-тригера описується логічним рівнянням:

![]() . (11)

. (11)

Це рівняння показує, що після перемикання стан D-тригера повторює значення сигналу на D-вході в тактові моменти часу. Тому в літературі D-тригери часто називають тригерами затримки (від Delay – затримка).

Схему

D-тригера

можна побудувати на основі синхронного

RS-тригера,

якщо сигнал по входу S

одночасно

подавати через інвертор на вхід R.

Схеми

D-тригера

будують також на основі самостійного

логічного рівняння. Перетворимо рівняння

(6), замінивши сигнал S

на D

і сигнал R

на![]() :

:

![]() . (12)

. (12)

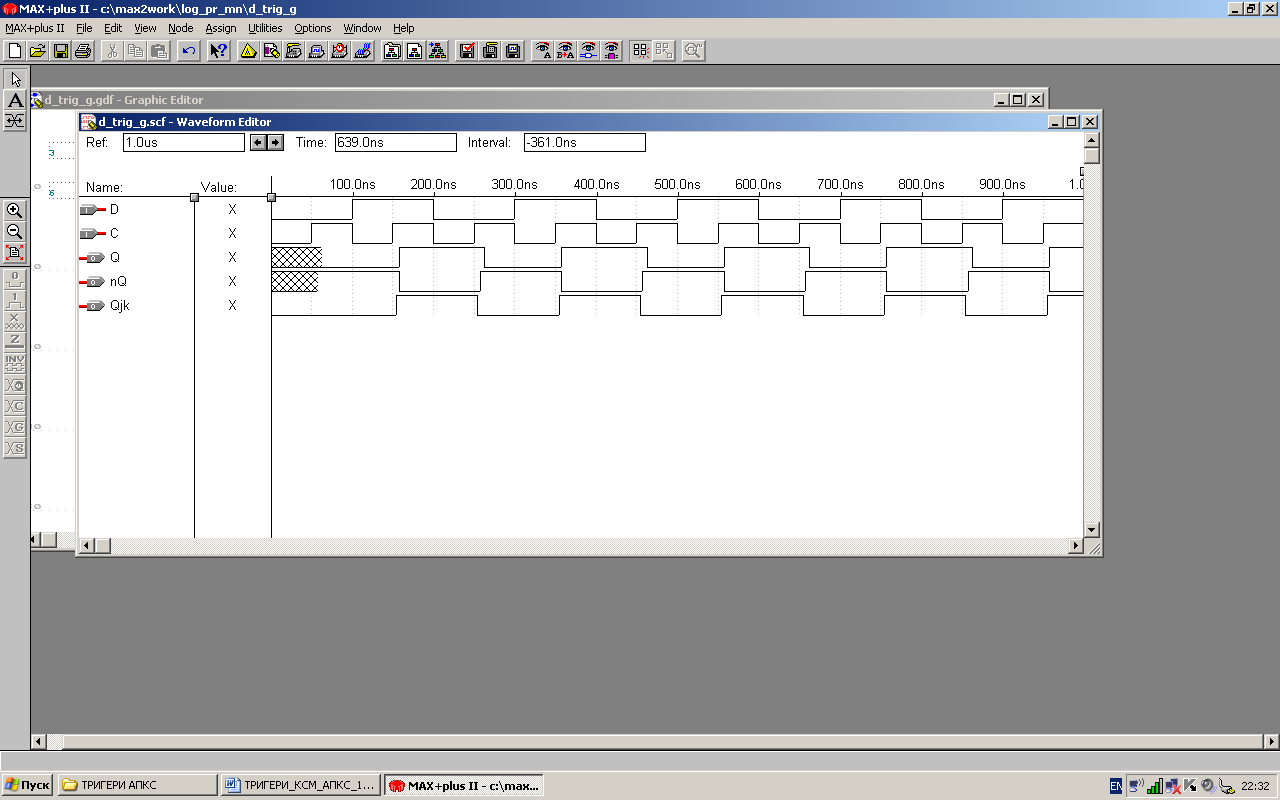

Відповідні схеми те результати моделювання їхньої роботи наведено на (рис. 11).

Рис. 11

На рис. 12 наведено проект, аналогічний до попереднього, з тією лише різницею, що замість синхронного RS-тригера взято JK-тригер.

Рис. 12

Для

затримки інформації в D-тригері

на довільне число тактів використовується

дозволяючий V-вхід

(рис. 13). Якщо

![]() ,

то DV-тригер

функціонує як звичайний тригер затримки;

якщо

,

то DV-тригер

функціонує як звичайний тригер затримки;

якщо

![]() ,

то робота схеми за входами блокується

і DV-тригер

зберігає попередню інформацію.

,

то робота схеми за входами блокується

і DV-тригер

зберігає попередню інформацію.

Рис. 13

На рис. 14 наведено реалізацію Т-тригера за допомогою D-тригера.

Рис. 14

На рис. 14 наведено тригер типу LATCH