- •Определение интерфейса эвм и систем. Классификация интерфейсов по функциональному назначению, по топологии связей, принципу обмена информацией, режиму обмена информацией.

- •2.1.2. Сигналы, линии, шины (подмагистрали) интерфейса pci

- •Правила арбитража в pci. Назначение и механизм исключающего доступа в pci. Назначение и временная диаграмма транзакции специального цикла.

- •Регистры конфигурационного пространства типа 0. Временная диаграмма транзакции конфигурационного чтения. Поля адреса конфигурационной транзакции типа 0 и типа 1.

- •Функциональные уровни устройств интерфейса pci-xp.

- •Пакет транзакционного уровня и заголовки tlp пакета интерфейса pci-xp.

- •Пакеты и заголовки пакетов уровня передачи данных интерфейса pci-xp.

- •Пакеты физического уровня (командные наборы) интерфейса pci-xp.

- •Надежная передача пакетов транзакционного уровня tlp интерфейса pci-xp. Структурная схема, поясняющая работу протокола ack/nak интерфейса pci-xp.

- •Задачи физического уровня интерфейса pci-xp.

- •Кодирование 8bit/10bit в интерфейсе pci-xp.

- •Соглашения по конструкции устройств pci-xp.

Регистры конфигурационного пространства типа 0. Временная диаграмма транзакции конфигурационного чтения. Поля адреса конфигурационной транзакции типа 0 и типа 1.

Интерфейс PCI обеспечивает полные программно-управляемые инициализацию и конфигурацию через отдельно адресуемое пространство конфигурации. Каждое PCI-устройство должно иметь до 256 байтов регистров конфигурации для этой цели.

У устройств одномагистральной PCI-системы (см. рис.2.1) пространство конфигурации типа 0,

содержащее до 64 32-разрядных регистров, доступных и по чтению, и по записи со стороны корневого

устройства. Они выполняют роль регистров-идентификаторов устройства, регистров команд и состояния,

шести базовых регистров адреса и др. (рис.2.16,а).

У мостов многомагистральной PCI-системы (см. рис.2.2) пространство конфигурации типа 1,

содержащее до 64 32-разрядных регистров, доступных и по чтению и по записи со стороны корневого

устройства. Они выполняют роль регистров-идентификаторов устройства, регистров команд и состояния,

двух базовых регистров адреса и др. (рис. 2.16,б).

В многомагистральных системах для поддержки иерархии PCI-магистралей используются два типа доступа конфигурации. Они имеют следующие два формата расшифровки полей адреса на линиях AD в течение фазы адреса транзакции конфигурации:

31 11 10 8 7 2 1 0

Адрес IDSEL |

Номер функции |

Номер регистра |

0 |

0 |

Type 0

31 24 23 16 15 11 10 8 7 2 1 0

Резерв |

Номер шины |

Номер устройства |

Номер функции |

Номер регистра |

0 |

1 |

Тип1

Тип 1 и тип 0 определяются значениями на линияхAD[1::0].

Тип 0 (когда AD [1::0] = 00) используется, чтобы выбрать устройство на PCI-магистрали, где транзакция выполняется.

Тип 1 (когда AD [1::0] = 01) используется, чтобы передатьзапрос конфигурации на другуюPCI-магистраль.

Поля адреса номер регистра и номер функции имеют одинаковое назначение для обоих типов, тогда как поля адреса номер устройства и номер шины используются только в типе 1.

Поле Резерв должно игнорироваться адресатами

Номер регистра - кодированное значение, используемое для адресации DWORD в пространстве

конфигурации адресата.

Номер функции - кодированное значение, используемое для выбора 1 из 8 возможных функций

устройства.

Номер устройства - кодированное значение, используемое для выбора 1 из 32 устройств на данной магистрали (шине). При выполнении транзакции типа 0 можно выбрать только 21 устройство с помощью линий AD [31...11].

Номер магистрали (шины) - кодированное значение, используемое для выбора 1 из 256 магистралей системы.

Если адресат находится на магистрали многомагистральной системы, подключенной «позади» моста, то исп. транзакция конфигурации типа 1. Она игнорируется всеми устр. на магистрали, за исключением мостов PCI-PCI, которые дешифрируют поле адреса номер магистрали (шины), с целью определить, находится ли адресат доступа конфигурации «позади» моста. Если поле адреса номер магистрали (шины) не соответствует номеру магистрали «позади» моста, то мост игнорирует такую транзакцию.

Мост обеспечивает обработку транзакции, если адресат на магистрали находится «позади» моста. Если поле адреса номер магистрали (шины) не равно номеру вторичной магистрали моста, то транзакция типа 1 передается без изменений. Если поле адреса номер магистрали (шины) равно номеру вторичной магистрали, мост преобразовывает транзакцию типа 1 в

транзакцию типа 0. Мост изменяет поле адреса AD [1::0] на 00 и передает поле адреса AD [10::02]

неизмененным, поле адреса номер устройства кодируется, чтобы выбрать 1 из 32 устройств на вторичной шине моста. Мост выставляет правильный сигнал IDSEL# и инициализирует транзакцию конфигурации типа 0.

Рис 2.11.17. Транзакция конфигурационного чтения

Мост PCI-PCI; назначение и функции. Механизмы выполнения функции маршрутизации в мостах PCI-PCI. Отложенные транзакции в мостах PCI-PCI.

представляет собой двухпортовое устройство, содержащее буферную память, совокупность регистров конфигурации, два контроллера интерфейса PCI, устройство управления. Один контроллер PCI обслуживает первичную магистраль, другой - вторичную магистраль.

Контроллер первичной магистрали (шины) со стороны первичной магистрали работает как устройство-цель, со стороны вторичной магистрали - как устройство-инициатор. Контроллер вторичной магистрали (шины) со стороны первичной магистрали работает как устройство-инициатор, со стороны вторичной магистрали - как устройство- цель.

Применение мостов PCI-PCI в многомагистральных PCI-системах, предоставляет возможности:

увеличение числа подключенных устр., что способствует преодолению ограничения

электрических спецификаций одномагистральной PCI-системы;

разделение устройств PCI на группы с различными характеристиками разрядности (32/64 бит),

тактовой частоты (33/66/100/133 МГц), протокола (PCI, PCI-X Mode 1, PCI-X Mode 2, PCI-X Express). организация сегментов с «горячим» подключением/отключением устройств;

организация одновременного выполнения транзакций от инициаторов, расположенных на разных

магистралях.

Допускается только древовидная конфигурация, т.е. две шины соединяются друг с другом лишь одним мостом и в системе нет «петель», образуемых мостами.

Мост должен выполнять ряд обязательных функций:

1) обслуживать в качестве устройства-инициатора вторичную магистраль, а именно:

выполнять арбитраж - принимать сигналы запроса REQx# от устройств-инициаторов вторичной

магистрали и предоставлять им право на управление шиной сигналами GNTx#;

парковать шину - подавать сигнал GNTx# какому-то устройству, когда управление шиной не

требуется ни одному из устройств;

генерировать конфигурационные циклы типа 0 с формированием индивидуальных сигналов IDSEL# к адресуемому устройству PCI;

«подтягивать» управляющие сигналы к высокому уровню;

определять возможности подключенных устройств и выбирать удовлетворяющий их режим работы шины (частота, разрядность, протокол);

формировать аппаратурный сброс (RST#) по сбросу от первичного интерфейса и по команде, сообщая о выбранном режиме сигнализацией;

2) поддерживать карты ресурсов, находящихся по разные стороны моста;

3) отвечать в качестве целевого устройства на транзакции, иници-

ированные мастером на одном интерфейсе и адресованные к ресурсу, находящемуся на стороне другого интерфейса; транслировать эти транз-

акции на другой интерфейс, выступая в роли ведущего устройства (мастера), и передавать их результаты истинному инициатору.

Маршрутизирующие функции моста. Основная задача маршрутизации - определение, где по отношению к мосту находится ресурс, адресованный каждой транзакцией, - является первоочередной задачей при обработке каждой транзакции, «увиденной» мостом на любом из своих интерфейсов. Эта задача решается двояко, поскольку в фазе адреса может передаваться как иерархический адрес PCI (шина – устройство - функция), так и «плоский» адрес памяти или порта ввода/вывода.

Маршрутизация по иерархическому адресу. Через номер шины и номер устр. адресуются

транзакции конфигурационной записи и чтения. Для этих транзакций маршрутизация основана на системе нумерации шин. Номера присваиваются магистралям (шинам) PCI при конфигурировании системы строго последовательно. Номера мостов соотв-т номерам их вторичных шин. Так, главный мост имеет номер 0.

Номера подчиненных шин моста начинаются с номера, следующего за номером его вторичной шины. Таким образом, для каждого моста необходимые ему знания топологии магистралей системы описывает список номеров магистралей - три числовых параметра в его конфигурационном пространстве:

номер первичной магистрали (Primary Bus Number);

номер вторичной магистрали (Secondary Bus Number); это и номер моста;

максимальный номер подчиненной магистрали (Subordinate Bus Number).

Все магистрали с номерами в диапазоне от номера вторичной магистрали до макс. номера

подчиненной магистрали включительно находятся со стороны вторич. магистрали, все остальные – со стороны первичной магистрали.

Знание номеров магистралей позволяет мостам распространять обращения к конфигурационным

регистрам устройств PCI в сторону от хоста к подчиненной магистрали. Ответы на расщепленные

транзакции (Split Complete) мост транслирует с одной магистрали на другую, если они адресованы к

противоположной магистрали.

Конфигурационные транзакции типа 0 мостами не транслируются. Конфигурационные транзакции

типа 1, обнаруженные на первичной магистрали, мост обрабатывает следующим образом:

преобразует их в конфигурац. транзакции типа 0, если номер магистрали (на линиях

AD [23:16]) соответствует номеру вторичной магистрали. При преобразовании в цикл типа 0 номер

устройства с первичной магистрали, полученный в фазе адреса, декодируется в позиционный код на вторичной магистрали, номер функции и номер регистра передаются без изменений, биты AD [1:0] на вторичной шине обнуляются;

пропускает их с первичной магистрали на вторичную без изменений, если номер шины

соответствует диапазону номеров подчиненных шин;

игнорирует их, если номер шины лежит вне диапазона номеров шин со стороны вторичного

интерфейса.

Маршрутизация по «плоскому» адресу. Для маршрутизации транзакций обращения к памяти и портам ввода/вывода мосту нужны карты адресов, на которых отмечены области, принадлежащие устройствам вторичной и подчиненных магистралей. В системе с «плоской»

адресацией этого достаточно. Для отмеченных областей мост должен отвечать в качестве целевого устройства на транзакции, «увиденные» им на первичной магистрали, и инициировать их в роли устройства- инициатора на вторичной магистрали; остальные транзакции на первичной магистрали он игнорирует. Мост должен вести себя «зеркально», т.е. отвечать в качестве целевого устройства на транзакции, «увиденные» им

на вторичной магистрали, и инициировать их как устройство-инициатор на первичной магистрали;

остальные транзакции на вторичной магистрали он игнорирует.

Каждый мост PCI-PCI имеет по одной карте адресов на каждый из трех типов ресурсов:

устройств ввода/вывода;

«настоящей» памяти;

памяти, на которую отображены регистры ввода/вывода.

В карте адресов указывается базовый адрес и размер области адресного пространства. Ресурсы одного типа для всех устройств, находящихся за мостом (на вторичной и всех подчиненных шинах), должны быть собраны в одну компактную область адресного пространства.

Отложенные транзакции выполняются мостом PCI для всех транзакций обращения к устр. ввода/вывода и транзакций конфигурации, а также для всех разновидностей транзакций чтения из памяти.

Отложенные транзакции выполняются в три фазы:

запрос транзакции устр-инициатором к мосту (обмена данными с целевым устройством еще нет);

завершение транзакции мостом с адресованным целевым устройством;

завершение транзакции устройством-инициатором с мостом.

Для того чтобы отложить транзакцию, мост должен поставить в очередь отложенный запрос (delayed request) и сигналом STOP# ввести условие Retry. На этом первая фаза отложенной транзакции завершается.

В запросе содержатся временно запоминаемые значения адреса, команды, разрешенных байтов, линий четности; для отложенных транзакций записи необходимо буферизировать (запомнить) еще и данные. Этой информации мосту достаточно, чтобы инициировать транзакцию на противоположной магистрали, - вторая фаза отложенной транзакции. Ее результатом будет преобразование в очереди отложенного запроса в отложенное завершение (delayed completion) - запрос вместе с ответом в виде состояния и запрошенных данных чтения. Устройство-инициатор транзакции, получив условие Retry, должно через некоторое время повторить транзакцию-запрос, причем в точности совпадающий с исходной транзакцией-запросом, иначе он

мостом будет воспринят как новый. Если к этому моменту мост успел выполнить отложенное завершение, то этот повторный запрос будет завершен нормальным образом, и мост удалит отложенное завершение из своей очереди. Если отложенное завершение еще не выполнено, то мост снова завершит транзакцию процедурой Retry, и устр-инициатор должно будет повторять свой запрос до тех пор, пока мост не обеспечит нормального завершения. Это третья, заключительная, фаза отложенной транзакции.

Устр-инициатор, дешифрировав условие Retry, обязано в точности повторить тот же запрос

транзакции, иначе мост будет накапливать невостребованные ответы. Конечно, и мост должен отслеживать невостребованные транзакции и через некоторое время (210 или 215 тактов шины) удалять их из своей очереди, чтобы не переполнить ее из-за «забывчивости» устройства-инициатора.

Откладывание транзакций мостом заметно увеличивает время исполнения каждой из них (с точки

зрения устройства-инициатора), однако оно позволяет обслуживать множество транзакций, находящихся в очередях мостов. В результате достигается увеличение суммарного объема произведенных транзакций на всех магистралях PCI за единицу времени, т.е. повышается производительность системы в целом.

Мост как держатель очереди транзакций в принципе может одновременно выполнять две транзакции, каждую на своей магистрали. Если бы транзакции не откладывались, а выполнялись непосредственно, то инициатору пришлось бы удерживать свою магистраль до тех пор, пока не освободится магистраль назначения (и все промежуточные магистрали, если

транзакция проходит через несколько мостов). В результате число бесполезных тактов ожидания на всех магистралях было бы недопустимо велико.

Транслируя транзакции чтения из памяти (как отложенные запросы), мост в некоторых случаях может использовать предвыборку (prefetch) - чтение про запас с целью ускорения работы с памятью. Выполняя предвыборку, мост рискует считать из источника данных больше, чем устройство-инициатор заберет от него в данной транзакции. В фазе завершения транзакции устройством-инициатором лишние данные в буфере

моста проще всего аннулировать, поскольку до возможного последующего востребования их в реальном источнике они могут быть уже модифицированы. Более сложный мост может отслеживать и эти изменения, аннулируя лишь модифицированные данные.

Согласование магистральных линий связи интерфейса PCI. Конструктивные особенности плат расширения интерфейса PCI.

Интерфейс PCI имеет две особенности с точки зрения электрических характеристик

Первая особенность:

магистраль интерфейса PCI - это магистраль КМДП-типа, и это означает, что токи устойчивых состояний (после переходных процессов) очень малы. Фактически большая часть постоянных токов определяется величиной сопротивления нагрузочных резисторов. Вторая особенность: в линиях связи интерфейса PCI принципиально используются отражения при формировании сигнала. Передатчики, возбуждающие сигналы в линиях интерфейса, обеспечивают формирование лишь половины требуемого логического перепада, что

экономит потребляемую ими мощность. Падающая (прямая) волна амплитудой, равной половине

логического перепада, возникает и распространяется по линии, отражается от ее несогласованного конца и вызывает отраженную (обратную) волну, равную по амплитуде падающей волне и распространяющуюся обратно к точке возникновения падающей волны. Сложение этих волн обеспечивает удвоение уровня напряжения в точке возникновения сигнала, чем достигается необходимый уровень напряжения в линии.

Детали согласования, а вернее, рассогласования линий связи для снижения требований по току к

самому передатчику иллюстрируются рис.2.18. Рассматривается случай (рис.2.18,а), когда

приемопередатчик устройства, инициирующего возбуждение линии в данный момент времени (t = 0), расположен в середине линии связи и передает нарастающий

фронт сигнала приемопередатчикам, принимающим сигнал на концах рассогласованной линии (Rн = ∞).Заметим, что входное сопротивление приемников устройств в любой момент времени достаточно велико по сравнению с волновым сопротивлением линии Z0, а выходное сопротивление передатчиков зависит от

режима устройства. Выходное сопротивление передатчика устройства, «слушающего» линию связи (передатчик в выключенном состоянии), достаточно велико по сравнению с волновым сопротивлением линии Z0, и можно считать, что в этом состоянии Rвых = ∞. Выходное сопротивление передатчика

устройства, «говорящего» в линию связи (передатчик в активном состоянии), пренебрежимо мало по сравнению с волновым сопротивлением линии Z0, и можно считать, что в этом состоянии Rвых = 0. Отметим, что на выходе передатчика включается последовательно согласующий резистор с

сопротивлением Rс = Z0/2. Падающая волна, возникающая в точке B (рис.2.18,б), равная половине

логического перепада Uпад = Uл (0,5Z0/(0,5Z0 + 0,5Z0)) = Uл/2, распространяется по обоим участкам линии и, достигнув конечных точек, вызывает отраженные волны Uотр = KотрUпад = Uпад, где Kотр = (Rн – Z0)/(Rн + Z0) = 1, так как Rн >> Z0. Результирующее (суммарное) напряжение Uа и Uс в точках А и С в этот момент (t = 0,12 нс) становится равным Uл (рис.2.18,в). В момент t = 0,24 нс отраженные от концов линии B и С волны амплитудой напряжения Uл/2 возвращаются к середине линии связи (точка А). Каждая из этих волн в свою очередь порождает новую отраженную волну напряжения амплитудой Uотр = Kотр·Uотр = ((Rн.экв – Z0)/(Rн.экв + Z))ЧUл/2 = ((Z0/3 – Z0)/(Z0/3 + Z0))ЧUл/2 = –Uл/4,

где Rн.экв = (Z0·Z0/2)/(Z0 + Z0/2) = Z0/3 и проходит как падающая волна напряжения на противоположный участок линии связи того же знака амплитудой Uл/4, поскольку проходящая волна равна алгебраической сумме падающей и отраженной волн в точке В в момент t = 0,24 нс. Суммарное напряжение падающей и отраженной волн в момент времени t = 0,36 нс в точке А и точке С равно нулю. Отражения в линии заканчиваются, и можно считать, что напряжения на концах линии устанавливаются через время 0,24 нс и составляют величину Uл.

Основные электрические параметры по постоянному и переменному току приемопередатчиков

интерфейса PCI приведены в табл.2.2.

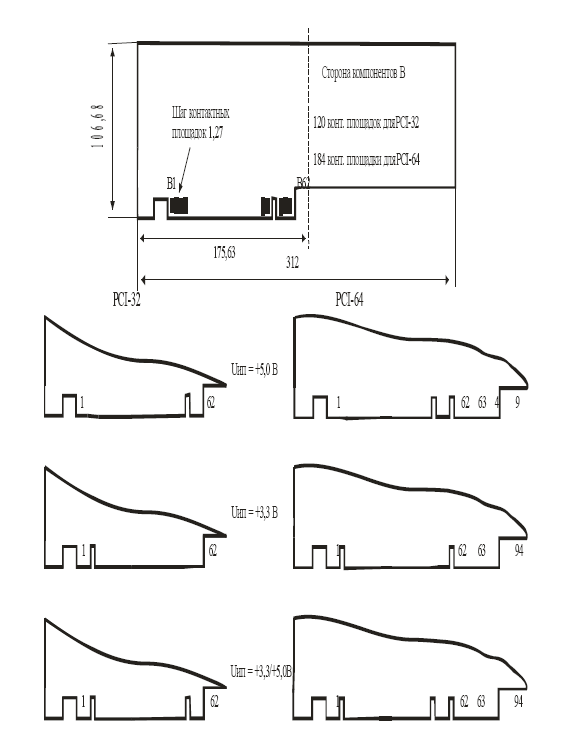

Конструктивные особенности плат расширения интерфейса PCI.

Плата расширения (дочерняя плата) PCI может иметь габариты не более 106,68175,63 мм для

случая 32-разрядной шины и не более 106,68312 мм для случая 64-разрядной шины (рис.2.19).

Если на плату смотреть со стороны В размещения компонентов, то в нижнем левом углу находится

двухрядный печатный разъем с шагом контактных площадок 1,27 мм. На стороне компонентов В

расположен ряд В контактных площадок, на противоположной стороне - ряд А контактных площадок.

Печатный разъем имеет ключи (вырезы на месте контактных площадок 12 и 13 или 50 и 51), которые обеспечивают установку дочерней платы PCI только в соответствующий соединитель (разъем) на материнской плате. Варианты разъемов PCI для плат с различным напряжением питания (5,0 В и/или 3,3 В) и различной разрядностью магистрали (32 и 64) показаны на рис.2.19,б.

Назначение контактных площадок печатных разъемов для трех типов плат (5-вольтовая; 3,3-вольтовая; универсальная) приводится в табл.2.2 и 2.3.

Системный интерфейс Compact PCI; назначение и основные технические характеристики.

Системный интерфейс Compact PCI предназначен для создания компьютерных систем реального

времени, использующихся в промышленной автоматизации, компьютерной телефонии,

телекоммуникационных системах, системах сбора и обработки данных, тренажерах и стендовом оборудовании,

системах специального (военного) применения и т.п.

Интерфейс Compact PCI используется в основном там, где требуются:

оптимальные возможности для работы современных микропроцессоров Pentium, PentiumMMX,

PentiumPRO, PentiumII, PowerPC, ALPHA, UltraSPARC и перспективных микропроцессоров;

модульность построения системы;

надежность;

устойчивость к воздействию жестких климатических, механических и радиационных факторов

(температуры, вибрации, пыли, электромагнитных помех и т.д.);

уменьшенные вес и габариты;

простота модернизации и удобство обслуживания;

малое время восстановления системы и улучшенные характеристики ремонтопригодности;

возможность замены модуля без выключения питания («горячей замены»).

Интерфейс Compact PCI был разработан в 1995 г. в рамках Ассоциации PICMG (PCI Industrial

Computer Manufacturer's Group). Сегодня в Ассоциацию PICMG входят более 300 фирм - производителей

компьютерного оборудования. Основная обязанность членов Ассоциации - разработка, развитие и

поддержка спецификаций систем промышленной автоматизации на базе интерфейса PCI. В настоящее время комитеты PICMG завершили работу над стандартом Compact PCI версии 2.1.

Основой электрических и логических параметров интерфейса Compact PCI служит спецификация

самого популярного стандарта «офисных» компьютеров - интерфейса PCI; механической основой -

европлаты формата 3U (100160 мм) и 6U (233160 мм). Интерфейс Compact PCI является 100%-ным

электрическим и логическим аналогом интерфейса PCI, и поэтому обеспечивается полное использование всего огромного парка недорогих PCI интегральных схем.

В отличие от обычных PCI-модулей (плат, ячеек) для настольных «офисных» компьютеров, в

Compact PCI-модулях (ячейках) в качестве соединителей (разъемов) используются высоконадежные 5-рядные 235-штырьковые соединители (раъемы) с шагом контактов 2 мм, соответствующие стандарту МЭК1076-4- 101. Из них 124 штырька используются для 32-разрядного Compact PCI, 55 штырьков - для

64-разрядного Compact PCI, остальные - для дальнейшего расширения и цепей «земли» и питания.

Compact PCI-модули устанавливаются в стандартные еврокрейты (блоки) стоечного, настенного или

настольного исполнения с установкой модулей с лицевой стороны еврокрейта. Каналы ввода/вывода информации могут подключаться к Compact PCI-модулю с помощью разъемов, устанавливаемых на его лицевой панели, или подсоединяться к его магистральному разъему, расположенному на тыльной стороне крейта.

Стандарт Compact PCI имеет перед стандартом PCI для настольных персональных компьютеров по

крайней мере три важнейших преимущества:

удвоенное количество подключаемых модулей к пассивной кросс-плате: 8 против 4;

значительно более приспособленную для промышленных

условий эксплуатации механическую конструкцию; в частности,

конструкция модулей обеспечивает проверенную годами

успешной эксплуатации схему крепления в четырех точках

Compact PCI-модуля и совершенную, столь необходимую для современной

КМОП-микроэлектроники, защиту от электростатических разрядов при установке модулей в еврокрейт

(блок);

используемые в Compact PCI-модулях промышленные разъемы штырькового типа значительно

более надежны, имеют лучшие характеристики по устойчивости к ударам, вибрации, пыли и по защите от влаги, чем печатные разъемы, применяемые для PCI-модулей обычных настольных персональных компьютеров. Сигнальные и питающие контакты Compact PCI-разъема конструктивно выполнены так, что возможна установка и замена модуля без выключения питания крейта (блока), что чрезвычайно важно в системах повышенной надежности.

Спецификации Compact PCI-модуля соответствуют новейшему стандарту IEEE 1101.11.

Интерфейс контрольно-измерительных систем PXI; основные технические характеристики.

Контрольно-измерительные системы, базирующиеся на интерфейсе PXI (PCI eXtention for

Instrumentation), обеспечивают более высокую производительность по сравнению с системами,

построенными на интерфейсах IEEE-488 и VXI, и при этом относительно дешевы.

Основные характеристики интерфейса PXI:

тактовая частота - 33/66 МГц;

32- и 64-разрядная передача данных;

скорость передачи данных - от 132 Мбайт/с (32 бита, 33 МГц) до 528 Мбайт/с (64 бита, 66 МГц);

расширение системы при помощи PCI-PCI-мостов;

поддержка режима Plug and Play.

Контрольно-измерительная PXI-система представляет собой шасси (крейт, блок) на базе

высокоскоростного интерфейса PXI, в которое могут быть установлены специфические для конкретной системы модули ввода/вывода.

Основой интерфейса PXI, по существу, является системный интерфейс Compact PCI и, соответственно, интерфейс PCI со всеми их достоинствами (см. разделы 2.1 и 2.2). Кроме того, интерфейс PXI имеет дополнительные магистрали тактирования и синхронизации, что обеспечивает высокий уровень интеграции

отдельных модулей, необходимый при создании точных измерительных и управляющих систем.

PXI-система состоит из шасси (chassis), содержащего объединительную или кросс-плату (backplane), в которое устанавливаются модуль системного контроллера (system controller module) и несколько периферийных модулей (peripheral modules). Слева от системного модуля может находиться несколько модулей расширения для контроллеров (controller expansion slots). Если используется контроллер

триггерной звезды (star trigger controller), этот модуль должен быть расположен за системным модулем. Если же контроллер триггерной звезды не используется, то в позицию этого модуля может быть установлен

любой периферийный модуль. Объединительная плата содержит соединители (разъемы) P1 и P2 (interface connectors) и обеспечивает связь между всеми компонентами системы. В системе с 33 МГц интерфейсом

Compact PCI может быть использовано до семи периферийных модулей, в системе с 66 МГц интерфейсом

Compact PCI - до четырех периферийных модулей. Системы с модулями расширения для контроллеров

могут быть построены с использованием нескольких магистралей со стандартными PCI-PCI-мостами. Кроме

того, PXI предоставляет возможность двустороннего взаимодействия с изделиями Compact PCI.

Основные технические характеристики интерфейса PCI-XP.

Контрольно-измерительные системы, базирующиеся на интерфейсе PXI (PCI eXtention for

Instrumentation), обеспечивают более высокую производительность по сравнению с системами,

построенными на интерфейсах IEEE-488 и VXI, и при этом относительно дешевы.

Основные характеристики интерфейса PXI:

тактовая частота - 33/66 МГц;

32- и 64-разрядная передача данных;

скорость передачи данных - от 132 Мбайт/с (32 бита, 33 МГц) до 528 Мбайт/с (64 бита, 66 МГц);

расширение системы при помощи PCI-PCI-мостов;

поддержка режима Plug and Play.

Контрольно-измерительная PXI-система представляет собой шасси (крейт, блок) на базе

высокоскоростного интерфейса PXI, в которое могут быть установлены специфические для конкретной системы модули ввода/вывода.

Основой интерфейса PXI, по существу, является системный интерфейс Compact PCI и, соответственно, интерфейс PCI со всеми их достоинствами (см. разделы 2.1 и 2.2). Кроме того, интерфейс PXI имеет дополнительные магистрали тактирования и синхронизации, что обеспечивает высокий уровень интеграции

отдельных модулей, необходимый при создании точных измерительных и управляющих систем.

PXI-система состоит из шасси (chassis), содержащего объединительную или кросс-плату (backplane), в которое устанавливаются модуль системного контроллера (system controller module) и несколько периферийных модулей (peripheral modules). Слева от системного модуля может находиться несколько модулей расширения для контроллеров (controller expansion slots). Если используется контроллер

триггерной звезды (star trigger controller), этот модуль должен быть расположен за системным модулем. Если же контроллер триггерной звезды не используется, то в позицию этого модуля может быть установлен

любой периферийный модуль. Объединительная плата содержит соединители (разъемы) P1 и P2 (interface connectors) и обеспечивает связь между всеми компонентами системы. В системе с 33 МГц интерфейсом

Compact PCI может быть использовано до семи периферийных модулей, в системе с 66 МГц интерфейсом

Compact PCI - до четырех периферийных модулей. Системы с модулями расширения для контроллеров

могут быть построены с использованием нескольких магистралей со стандартными PCI-PCI-мостами. Кроме

того, PXI предоставляет возможность двустороннего взаимодействия с изделиями Compact PCI.

Устройства PCI-XP системы. Понятие транзакции в PCI-XP; типы транзакций.

1. Функциональное назначение - системный интерфейс.

2. Объединяет следующие типы устройств (рис.2.29):

ядро, или корневой комплекс (Root Сomplex);

переключатели (Switch);

конечные точки (End Point), которые подразделяются на традиционные конечные точки (Legancy

End Point) и PCI-XP конечные точки (PCI-XP End Point);

мосты PCI-XP к PCI (PCI-XP Bridge to PCI) (на рис.2.29 не показаны).

Устройство, начинающее транзакцию, называется запросчиком. Устройство, завершающее транзакцию,

называется комплитором. Как запросчиком, так и комплитором при выполнении различных транзакций

может служить как корневой комплекс, так и любая конечная точка.

3. Топология связей - древовидная (см. рис.2.29).

4. Принцип обмена информацией - последовательная передача информации (бит за битом).

5. Скорость передачи информации в линии - 2,5 Гбит/с.

6. Битовая скорость передачи информации в канале равна:

0,5 Гбайт/с (2,5 Гбит/с 2 = 5 Гбит/с = 0,5 Гбайт/с) при использовании 2 витых пар на канал (1);

1 Гбайт/с (2,5 Гбит/с 4 = 10 Гбит/с = 1 Гбайт/с) при использовании 4 витых пар на канал (2);

2 Гбайт/с (2,5 Гбит/с 8 = 20 Гбит/с = 2 Гбайт/с) при использовании 8 витых пар на канал (4);

4 Гбайт/с (2,5 Гбит/с 16 = 40 Гбит/с = 4 Гбайт/с) при использовании 16 витых пар на канал (8);

6 Гбайт/с (2,5 Гбит/с 12 = 60 Гбит/с = 6 Гбайт/с) при использовании 24 витых пар на канал (12);

8 Гбайт/с (2,5 Гбит/с 32 = 80 Гбит/с = 8 Гбайт/с) при использовании 32 витых пар на канал (16);

16 Гбайт/с (2,5 Гбит/с 64 = 160 Гбит/с = 16 Гбайт/с) при использовании 64 витых пар на канал

(32).

7. В простейшем случае (1) в канале две дифференциальные линии, каждая из которых предназначена для передачи в симплексном режиме (передаваемые данные Tx и принимаемые данные Rx).

8. Обмен информацией - транзакционный. Возможны непочтовые транзакции (с уведомлением, с

возвратом данных) и почтовые транзакции (без уведомления, без возврата данных).

Типы транзакций:

запись/чтение памяти;

запись/чтение устройств ввода/вывода;

запись/чтение пространства конфигурации;

передача сообщений.

9. Поддерживает 32- и 64-разрядную адресацию. Разрядность передаваемых данных - одно двойное

слово 1DW(32) и два двойных слова 2DW(64).

10. Реализуются все транзакции обмена данными, свойственные PCI и PCI-X (cм. п. 8), и добавляется передача сообщений.

11. Обеспечивается совместимость программного обеспечения на уровне ядра PCI-XP с PCI и PCI-X.

12. Поддерживаются изохронные передачи информации (в масштабе реального времени).

13. Поддерживаются различные режимы качества обслуживания введением восьми классов трафика (8TC) и обеспечением восьми классов виртуальных каналов (8VC).

14. Защищенность адресных пространств обеспечивается отдельными адресными пространствами памяти, ввода/вывода и конфигурации.

15. Используется протокол прерывания, сигнализируемый сообщением (Message Signaled Interrupt), что уменьшает задержку на обработку прерываний и устраняет необходимость в специальных линиях для сигналов прерывания.

16. Функционально любое устройство PCI-XP описывается многоуровневой структурой

(транзакционный уровень TL, уровень передачи данных DLL, физический уровень PL).

17. Поддерживается технология Plug and Play.

18. Контроль потребляемой мощности с автоматическим переходом из режима высокого потребления в режим низкого потребления, и наоборот.

19. Кодирование информации на физическом уровне - 8b/10b.

20. Применение скремблирования для решения проблем электромагнитной совместимости.

21. Обеспечивается гальваническая развязка между отдельными устройствами.

22. Длина линий связи в пределах канала до 0,75 м.

23. Конструкция модуля PCI-XP совместима с конструкцией модуля PCI и PCI-X.32)Устройства PCI-XP системы.

32)

Объединяет следующие типы устройств (рис.2.29):

ядро, или корневой комплекс (Root Сomplex);

переключатели (Switch);

конечные точки (End Point), которые подразделяются на традиционные конечные точки (Legancy

End Point) и PCI-XP конечные точки (PCI-XP End Point);

мосты PCI-XP к PCI (PCI-XP Bridge to PCI) (на рис.2.29 не показаны).

Устройство, начинающее транзакцию, называется запросчиком. Устройство, завершающее транзакцию,

называется комплитором. Как запросчиком, так и комплитором при выполнении различных транзакций

может служить как корневой комплекс, так и любая конечная точка.

Понятие транзакции в PCI-XP; типы транзакций.

Транзакции интерфейса PCI-XP

Транзакция в интерфейсе PCI-XP определяется как последовательность нескольких (в частном случае одной) передач пакетов информации между запросчиком и комплитором. В качестве запросчика могут выступать и корневой комплекс, и конечная точка. В качестве комплитора могут выступать и корневой комплекс, и конечная точка, и переключатели, и мосты.

Последовательность пакетов состоит из пакета-запроса и в общем случае нескольких пакетов-

завершений. Пакет-запрос содержит командную маршрутную информацию и пересылаемые данные в случае транзакции записи. Пакет-завершение содержит маршрутную информацию, необходимую для маршрутизации пакета-завершения обратно к запросчику. Пакет-завершение проходит тот же путь и последовательность переключателей в обратном порядке, что и пакет-запрос. Кроме того, он содержит

пересылаемые данные в случае транзакции чтения. И пакет-запрос, и пакет-завершение содержат

одинаковый тег (метку), чтобы определить их принадлежность к одной транзакции.

Различают непочтовые и почтовые типы транзакции. В непочтовых транзакциях запросчик передает пакет-запрос комплитору. В ответ комплитор посылает пакет-завершение (в общем случае пакеты- завершения) запросчику, которые содержат уведомление о получении пакета-запроса. В дополнение пакет-завершение в транзакции чтения содержит запрашиваемые данные. В транзакции записи данные содержатся в пакете-запросе.

В почтовых транзакциях запросчик лишь передает пакет-запрос комплитору.

Все транзакции делятся на четыре категории. В табл.2.9 приведены категории и типы транзакций, а

также типы пакетов, их образующих.