- •Определение интерфейса эвм и систем. Классификация интерфейсов по функциональному назначению, по топологии связей, принципу обмена информацией, режиму обмена информацией.

- •2.1.2. Сигналы, линии, шины (подмагистрали) интерфейса pci

- •Правила арбитража в pci. Назначение и механизм исключающего доступа в pci. Назначение и временная диаграмма транзакции специального цикла.

- •Регистры конфигурационного пространства типа 0. Временная диаграмма транзакции конфигурационного чтения. Поля адреса конфигурационной транзакции типа 0 и типа 1.

- •Функциональные уровни устройств интерфейса pci-xp.

- •Пакет транзакционного уровня и заголовки tlp пакета интерфейса pci-xp.

- •Пакеты и заголовки пакетов уровня передачи данных интерфейса pci-xp.

- •Пакеты физического уровня (командные наборы) интерфейса pci-xp.

- •Надежная передача пакетов транзакционного уровня tlp интерфейса pci-xp. Структурная схема, поясняющая работу протокола ack/nak интерфейса pci-xp.

- •Задачи физического уровня интерфейса pci-xp.

- •Кодирование 8bit/10bit в интерфейсе pci-xp.

- •Соглашения по конструкции устройств pci-xp.

Правила арбитража в pci. Назначение и механизм исключающего доступа в pci. Назначение и временная диаграмма транзакции специального цикла.

1. В интерфейсе PCI используется централизованная система арбитража

2. Арбитраж «замаскирован», т.е. осуществляется во время выполнения предыдущей транзакции, что повышает производительность интерфейса PCI.

3. Арбитр должен обеспечивать некоторую процедуру арбитража, например чередование приоритетов.Спецификация PCI не устанавливает конкретный алгоритм арбитража, и алгоритм арбитража выбирается разработчиком системы.

4. Устройство-инициатор выставляет запрос центральному арбитру на захват интерфейса установкой радиального сигнала REQ#.

5. Когда арбитр решает, что может предоставить интерфейс в распоряжение запрашивающего

устройства-инициатора, он выставляет подтверждение устройству-инициатору на захват интерфейса установкой радиального сигнала GNT#.

6. Устройство-инициатор должно убедиться, что его сигнал GNT# установлен по нарастающему

фронту сигнала CLK.

7. Арбитр может сбросить сигнал GNT# для устройства-инициатора на любом такте сигнала CLK, при этом:

если сигнал GNT# сброшен, а сигнал FRAME# установлен, то транзакция должна закончиться сбоем

устройства-инициатора;

если сброшены сигналы GNT# и FRAME#, то транзакция

не должна начинаться.

8. Все устройства PCI должны определять окончание транзакции по ситуации, когда сигналы FRAME# и IRDY# сброшены.

9. Установленный сигнал GNT# дает доступ устройству-инициатору к магистрали на одну транзакцию.

Если устройство-инициатор нуждается еще в одном доступе на транзакцию, оно должно продолжать

выставлять сигнал REQ#. Если не установлены запросы от других устройств-инициаторов или если

захватившее магистраль устройство-инициатор имеет наивысший приоритет, центральный арбитр

продолжает предоставлять магистраль этому устройству-инициатору.

10. Устройство-инициатор может сбросить запрос на захват магистрали (сигнал REQ#) на любом такте

сигнала CLK, но в этом случае арбитр может мгновенно сбросить сигнал GNT#. Чтобы этого не

происходило, сброс сигнала REQ# должен совпадать по крайней мере с установкой сигнала FRAME#.

Назначение и механизм исключающего доступа в PCI.

В случае исключающего доступа доступ со стороны некоторого устройства-инициатора, захватившего магистраль, к некоторому устройству-цели может блокироваться другим устройством-инициатором.

Различают два механизма блокировки исключающего доступа:

блокировка устройства-цели;

блокировка PCI.

Устр.-цель, которое поддерживает исключающий доступ, должно функционировать в соответствии с правилами.

1. В устройстве-цели запоминается режим блокировки, если сигнал LOCK#сброшен в начале фазы адреса ( FRAME# установлен) и затем установлен в конце фазы адреса (LOCK# устанавливается в конце фазы адреса, т.е. через такт CLK после первогоустановления FRAME# в начале транзакции).

2. Если в конце фазы адреса устанавливается LOCK#, то сохранение режима блокировки устр-цели продолжается до того момента, пока сигналы LOCK# и FRAME# не будут сброшены одновременно.

3. Сохранение режима блокировки устр-цели может нарушиться ранее, но только в фазе адреса, если устройство-цель просигнализирует ситуацию перезапуска по инициативе устройства-цели(сбрас. TRDY# и уст. STOP#) или ситуацию сбоя устройства-цели.

4. Для всех других устр-инициаторов доступ к заблокированному устройству-цели не

обеспечивается, и заблокированное устройство-цель обрывает такие обращения процедурой сбоя

устройства-цели (уст.STOP# и сбрас. DEVSEL# ).

5. Устройство-цель должно гарантировать для устройства-инициатора, заблокировавшего его,

транзакцию с передачей как минимум 16 байт.

6. Устройство-цель должно проверять LOCK# в фазе адреса, даже если оно еще не

дешифрировало адрес и не ответило DEVSEL#.

7. Если заблокированное устр-цель при проверке LOCK# в фазе адреса обнаруживает, что доступ идет не от устройства-инициатора, заблокировавшего его, то сбрасывается DEVSEL# и устанавливается STOP#

Устройство-инициатор, которое поддерживает исключающий доступ, должно функционировать в соответствии со следующими правилами.

1.на линии LOCK# устанавливается в любой момент времени только одним устройством-инициатором и может быть сохранен ( LOCK# установлен) после окончания текущей транзакции до тех пор, пока это устройство-инициатор не прерветрежим исключающего доступа или арбитр не прервет принудительно режим исключающего доступа для этого устройства-инициатора.

2. Первой транзакцией при проведении блокировки для исключающего доступа должна быть

транзакция чтения из памяти.

3. LOCK# должен быть установлен в такте с CLK, следующем за тактом фазы, и долженподдерживаться установленным до окончания исключающего доступа.

4. LOCK# должен быть сброшен, когда доступ завершается сбоем устройства-инициатора илисбоем устройства-цели.

5. LOCK# должен быть сброшен как минимум на один такт IDLE между последовательными

операциями блокировки.

6. В режиме блокировки устройство-инициатор не имеет права обращаться по адресу, выходящему заадресные границы конкретного устройства-цели.

7. Перед тем как устройство-инициатор выставит свой LOCK#, оно проверяет, не идет ли

исключающий доступ, вызванный другим устройством-инициатором. Условие, когда исключающий доступне имеет места, следующее: FRAME# и LOCK# сброшены.

8. Если сигнал на линии LOCK# установлен некоторым устройством-инициатором, другое устройство-инициатор должно задержать установку своего REQ# к арбитру до тех пор, пока не освободится линия LOCK#.

9. Когда устройству-инициатору предоставляется доступ к магистрали и сигнал на линии LOCK# не

установлен, происходит захват управления линией LOCK#.

Общие правила исключающего и неисключающего доступов:

1. Неисключающий доступ к незаблокированным устройствам-целям разрешен в интерфейсе PCI , дажеесли сигнал LOCK# установлен.

2. Устройства-инициаторы имеют право бороться за захват управления сигналом LOCK#, когда

заканчивается текущий исключающий доступ.

3. Арбитр не должен реагировать на сброс сигнала LOCK# в течение одного такта сигнала CLK, когдаустановлен сигнал FRAME# и идет фаза адреса; иначе говоря, арбитр должен «закрывать глаза» на это кратковременное изменение сигнала LOCK#.

Рис.

2.1.13 Временные диаграммы исключающего

доступа в PCI

Рис.

2.1.13 Временные диаграммы исключающего

доступа в PCI

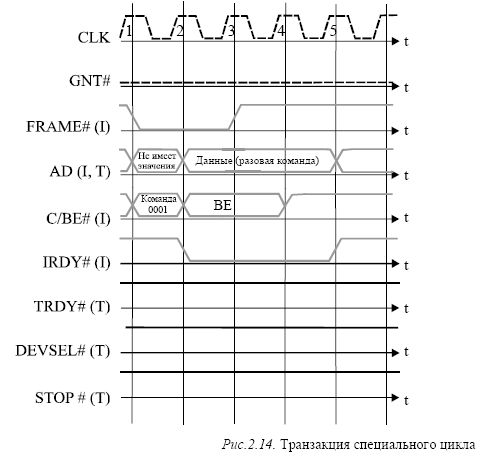

Транзакция специального цикла

Транзакция спец цикла предназначена для передачи некоторой команды устройству-цели.

Данную команду (на линиях C/BE# в фазе адреса код 0001)разработчики рассматривают как

реализацию механизма «логический проводник». Это команда широковещательной передачи: все

устройства-цели принимают и «заинтересованные» устройства-цели дешифрируют ее.

Правила выполнения транзакции специального цикла:

1. Фаза адреса не содержит достоверной информации на линиях AD [31….0], но сигналы на этих линиях должны, например, принимать значения логического «0», чтобы не нарушался контроль на четность.

2. В фазе данных на линиях AD выставляется код команды, который считывается всеми устройствами и затем дешифрируется в некоторую команду.

3. Устройства-цели в ответ на код команды специального цикла

не устанавливают сигнал DEVSEL#.

4. Завершается транзакция аварийно со стороны устройства-инициатора. Так как TRDY# и

DEVSEL# не установлены, то на пятом такте транзакции устройство-инициатор снимает IRDY#, и все устройства-цели «понимают», что выполняется транзакция специального цикла.

5. Устройство-инициатор может вставлять задержку сигналом IRDY#.