- •1. Состав и назначение семейств pic-контроллеров

- •6. Схема тактирования и цикл выполнения команды в мк pic16f84

- •7. Организация памяти программ и стека

- •8. Организация памяти данных

- •9. Регистры специального назначения pic16f84: регистр status

- •10. Регистры специального назначения pic16f84: регистр option

- •11. Регистры специального назначения pic16f84: регистр intcon

- •12. Регистры специального назначения pic16f84: счетчик команд pcl и pclath

- •13. Прямая и косвенная адресация в мк pic16f84

- •Порт ввода/вывода «а» мк pic16f84

- •Порт ввода/вывода «в» мк pic16f84

- •Модуль таймера tmr0 мк pic16f84

- •Память данных eeprom мк pic16f84

- •18 Организация прерываний в мк pic16f84

- •19 Работа с модулем ацп в мк pic16f676

- •20. Работа с модулем опорного напряжения в мк

- •21 Работа с модулем компаратора в мк

- •22 Форматы команд pic16f84a

- •23 Команды работы с байтами в мк pic16f84

- •24 Команды работы с битами в мк pic16f84

- •25 Команды управления в мк pic16f84

- •26 Команды работы с константами в мк pic16f84

- •27 Синтаксис ассемблера mpasm: метки, мнемоники, операнды, комментарии

- •Директивы языка mpasm

- •Языки программирования плк

- •Промышленные сети и интерфейсы: Can

Порт ввода/вывода «а» мк pic16f84

Порт ввода/вывода «в» мк pic16f84

PORT A <5> | TRIS A

PORT B <8> | TRIS B

RB7 RB0

7 0

1 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

TRIS B

0-вывод

1-ввод

В PIC16F84 имеет 2 порта:

-PORT A ( 5 bit)

-PORT B (8 bit)

Порт А представляет собой 5 битовый фиксатор соответствующий выводам МК RA0-RA4. Линия RA4 имеет вход триггера Шмита, а выход с открытым стоком. Все остальные линии порта имеют TTL входные уровни, и CMOS выходные буферы.

К каждой линии порта поставлен в соответствии бит направления передачи данных, хранящийся в управл. регистре TRIS A.

Если бит управл. регистром TRIS A имеет значение «1», то соответствующую линию порта настроена на ввод «0», переключает линию на вывод и одновременно выводит на нее содержимое регистра порта. Линии порта по умолчанию настроены на ввод. Вывод RA4 мультиплексирован с тактовым входом таймера.

PORT B это двунаправленный 8-ми битовый порт, соот. выводам RB7-RB0. Управляющий регистр для него TRIS B. Работает также как и TRIS A. У каждой ножки порта Б имеется небольшая активная нагрузка на линию питания, она автоматически отключается, если ножка запрограммирована на вывод. Подключение нагрузки осуществляется битом RB PU, регистра OPTION. При сбросе нагрузки отключаются.

4 линии порта Б, RB7-RB4 смогут вызвать прерывания (RB IF) при изменении значения сигнала на любой из них. Если эти линии настроены на ввод, то они опрашиваются и защелкиваются в цикле чтения Q1, новая величина входного сигнала, сравнивается со старой в каждом командном цикле. При несовпадении значения сигнала на ножке и фиксаторе генерируется запрос прерывания RB IF. Любая линия настроена на вывод в том сравнении не участвует.

Линия RB0 мультиплексирована с входом внеш. Прерывания INT.

На ножку, работающую в режиме вывода не должны нагружаться внешние источники токов, т.к. результирующие токи могут повредить кристалл.

Необходимо выдерживать определенную последовательность при обращении к портам ввода-вывода. Запись в порт вывода происходит в конце командного цикла. При чтении данные должны быть стабильны в начале командного цикла, т.е. надо быть стабильны в начале командного цикла, т.е надо быть внимательным в операциях чтения следующих сразу же а записью в тот же порт необходимо учитывать инерционность установление напряжения на выводах, поэтому может потребоваться программная задержка ( 1-2 ком. цикла), чтобы напряжение на ножке, котор. зависит от нагрузки, успело стабилизироваться до начала исполнения след. команды.

Модуль таймера tmr0 мк pic16f84

TMR0 - таймер/счетчик, имеет следующие особенности:

• 8-разрядный таймер/счетчик;

• возможность чтения и записи текущего значения счетчика;

• 8-разрядный программируемый предделитель;

• внутренний или внешний источник тактового сигнала;

• выбор активного фронта внешнего тактового сигнала

• прерывания при переполнении (переход от FFh к 00h).

Если предварительный делитель включен перед WDT, то коэффициент деления тактового сигнала

для TMR0 равен 1:1.

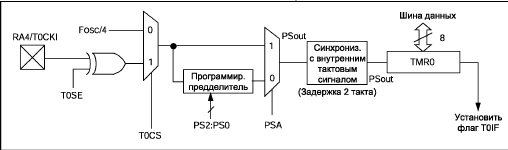

Блок схема модуля TMR0 показана на рисунке 11-1.

Управляющий регистр

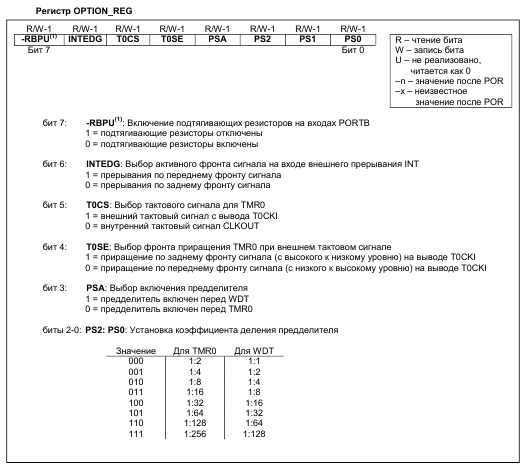

Регистр OPTION_REG доступен для чтения и записи, содержит биты управления:

• Предварительным делителем TMR0/WDT;

• Активным фронтом внешнего прерывания RB0/INT;

• Подтягивающими резисторами на входах PORTB.

Если предварительный делитель включен перед WDT, то коэффициент деления тактового сигнала

для TMR0 равен 1:1.

Работа таймера TMR0

Когда бит T0CS сброшен в ‘0’ (OPTION_REG<5>), TMR0 работает от внутреннего тактового сигнала. Приращение счетчика TMR0 происходит в каждом машинном цикле (если предделитель отключен). После записи в TMR0 приращение счетчика запрещено два следующих цикла (см. рисунки 11-2 и 11-3). Пользователь должен скорректировать эту задержку перед записью нового значения в TMR0.

Если бит T0CS установлен в ‘1’ (OPTION_REG<5>), TMR0 работает от внешнего источника тактового сигнала на входе T0CKI. Активный фронт внешнего тактового сигнала выбирается битом T0SE (OPTION_REG<4>) (T0SE=0 - активным является передний фронт сигнала Предделитель может быть включен перед WDT или TMR0, в зависимости от состояния бита PSA в регистре OPTION_REG<3>. Если бит PSA сброшен в ‘0’, то предделитель включен перед TMR0. Нельзя прочитать или записатьновое значение в предделитель. Когда предделитель включен перед TMR0, можно выбрать его коэффициент деления1:2, 1:4,…,1:256. Любая запись в регистр TMR0 вызовет запрещение приращения таймера TMR0 в течение двух следующих машинных циклов (2TCY). Т.е. после записи нового значения в TMR0 таймер не инкрементируется пока не определено, что 3-я команда не циклически повторяющаяся (см. рисунок 11-2). Если предделитель включен перед TMR0, то запись в регистр TMR0 вызовет немедленное изменение TMR0 и сброс предделителя. Приращение TMR0 и предделителя запрещено в течение 2-х машинных циклов (2TCY), после записи в TMR0.