Лабораторна робота №6 «дослідження дешифраторів та мультиплексорів »

Мета: вивчити принципи роботи дешифратора, шифратора, мультиплексора та перетворювача коду.

Дешифратор – логічна комбінаційна схема, яка має n інформаційних входів і 2n виходів. Кожній комбінації логічних сигналів на входах відповідає активний рівень на одному з виходів. Зазвичай n дорівнює 2, 3 або 4.

Таблиця

істинності для дешифратора з двома

входами (дешифратора 2

![]() 4)

буде мати наступний вигляд:

4)

буде мати наступний вигляд:

X1 |

X2 |

Y0 |

Y1 |

Y2 |

Y3 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

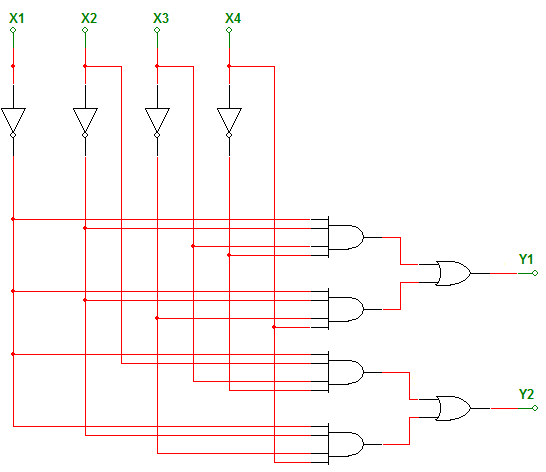

Синтез дешифратора можна виконати на

логічних елементах «І», «АБО» та «НІ»,

для чого слід записати ЗДНФ

для кожного з виходів:

![]() ,

,

![]() ,

,

![]() ,

,

![]() .

.

Рис. 1 Схема дешифратора на логічних елементах

Н

Рис. 2 Дешифратор в середовищі Multisim

Окрім інформаційних входів (А, В, С) дешифратори зазвичай мають додаткові входи управління (G). Сигнали на цих входах можуть дозволяти функціонування дешифратора або переводять його в пасивний стан, при якому, незалежно від сигналів на інформаційних входах, на всіх виходах встановиться рівень логічної одиниці.

Входи управління можуть бути прямими або інверсними. Для дешифраторів з прямим входом управління активним рівнем є рівень логічної одиниці, а дешифраторів з інверсним – рівень логічного нуля. На рис. 2 представлений дешифратор з одним інверсним входом управління.

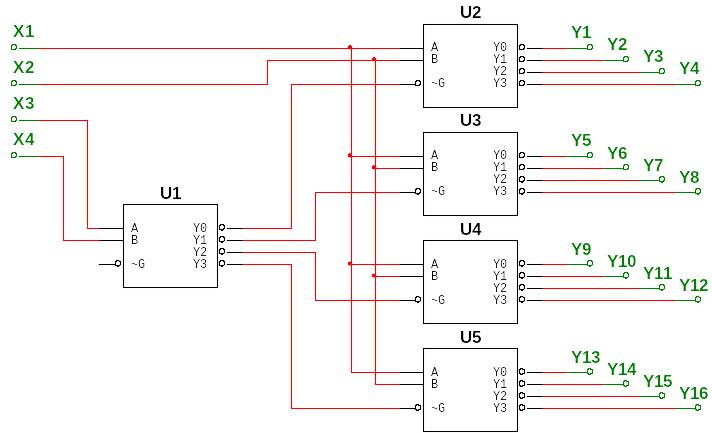

Для дешифраторів з декількома входами управління функцією дозволу, як правило, є логічний добуток всіх сигналів управління. Зазвичай входи управління використовують для збільшення розрядності (каскадування) дешифраторів або при паралельній роботі декількох схем на спільних вихідних лініях.

Для збільшення розрядності дешифратора старші розряди коду подаються на дешифратор першого каскаду, виходи якого підключені до входів дозволу роботи дешифраторів другого каскаду. На об'єднані входи дешифраторів другого каскаду подаються молодші розряди вхідного коду. Приклад побудови дешифратора 4–16 із п’яти мікросхем 2–4 показано на рис. 3.

Рис. 3 Збільшення розрядності (каскадування) дешифратора

Нехай на входах X3, X2, X1 та X0 присутнє число 10112, яке є представленням десяткового числа 1110. На входах X3 та X2, присутня комбінація 102, що відповідає числу 2 в десятковій системі. Таким чином саме на виході Y2 дешифратори U1 сформується активний сигнал, рівний нулю і лише дешифратору U4, який приймає його по входу G, дозволяється робота. На входах X1 та X0 присутнє число 112, що відповідає в числу 3 десятковому вигляді. Воно подається паралельно на всі чотири дешифратори, але лише на виході Y3 мікросхеми U4 з’являється активний сигнал. Якщо перелічити по порядку виходи всіх дешифраторів другого каскаду то вихід Y3 мікросхеми U4 буде виходом 11 для всієї схеми.

Аналогічно з дев'яти мікросхем 3–8 можна отримати дешифратор 6–64, а з сімнадцяти мікросхем 4–16 — дешифратор 8–256.

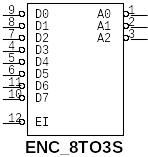

Шифратор виконує функцію, зворотну дешифратору, тобто перетворить непозиційний двійковий 2n розрядний код в n розрядний позиційний код. При подачі на один з входів одиничного сигналу на виході формується відповідний двійковий код. Принцип синтезу такий же як і для дешифратора. Нехай задана наступна таблиця істинності:

X1 |

X2 |

X3 |

X4 |

Y0 |

Y1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

ЗДНФ за поданою таблицею буде мати вигляд:

![]()

![]()

|

|

Рис. 4 Схема синтезованого шифратора та його модель у середовищі Multisim

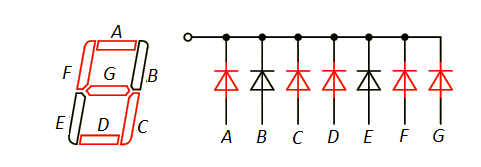

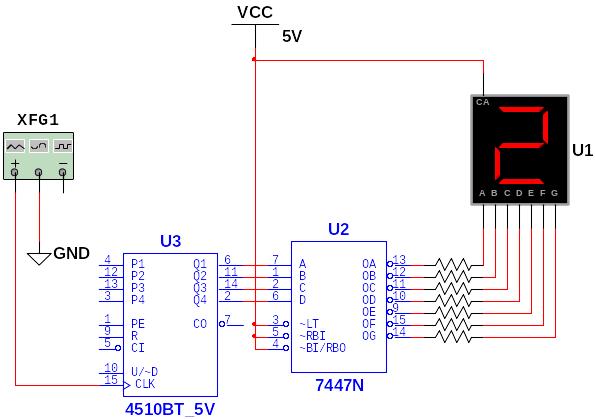

Найбільш часто перетворювачі коду використовуються при виведенні інформації на індикатори. Наприклад, для виведення десяткових цифр від 0 до 9 широко застосовується семисегментний індикатор. Перетворювач коду в такому випадку буде мати 4 входи та 7 виходів для підсвічення наборів сегментів індикатор, що відповідають кожній цифрі.

Рис. 5 Схема семисигментного індикатора

Таблиця істинності такого дешифратора буде мати наступний вигляд:

Цифра |

Двійковий код |

A |

B |

C |

D |

E |

F |

G |

|||

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

2 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

3 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

4 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

5 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

6 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

7 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

8 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

9 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

Виходячи з таблиці істинності можна сформувати ЗДНФ та синтезувати схему дешифратора.

Рис. 6 Дешифратор двійкового коду в код семисегментного індикатора (7447N) підключений до десяткового ліичильника (4510BT_5V)

М

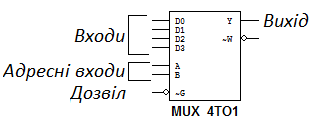

Рис. 7 Модель мультиплексора в середовищі

Multisim

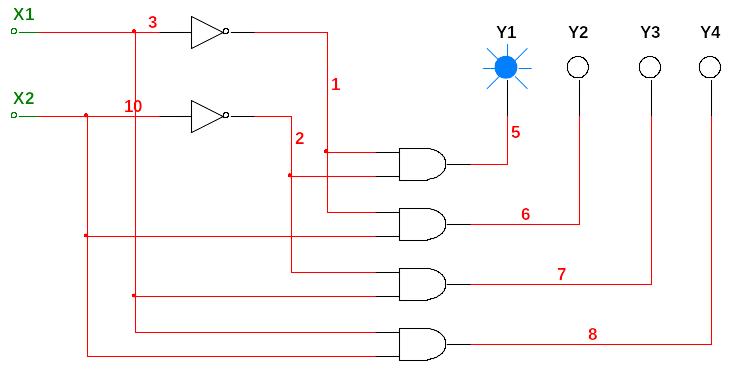

Керування роботою мультиплексора (вибір номеру каналу) здійснюється за допомогою вхідного коду, що подається на адресні входи. Наприклад, для 4-канального мультиплексора необхідний 2-розрядний код, управляючий код, а для 16-канального — 4-розрядний код. Розряди коду можуть позначаються як 1, 2, 4, 8 або А0, А1, А2, А3.

Деякі мікросхеми мультиплексорів мають вхід дозволу (заборони) «G», який при подачі на нього активного сигналу відключає виходи. На рис. 7 Зображено 4 канальний, однорозрядний мультиплексор із входом заборони.

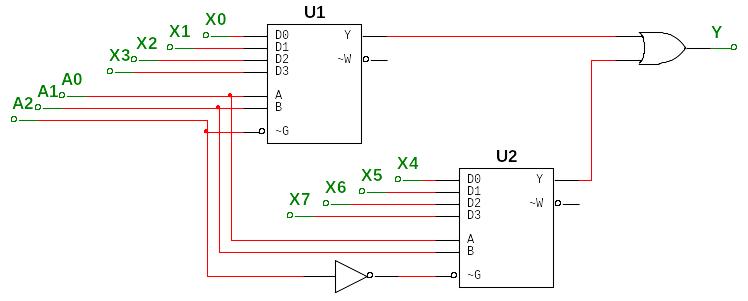

Мікросхеми мультиплексорів можна об'єднувати для збільшення кількості каналів. Наприклад, два 4-канальних мультиплексора легко об'єднуються в 8-канальний за допомогою інвертора на входах дозволу і елементу І-НІ для об’єднання вихідних сигналів мультплексорів в один (рис. 8). Старший розряд коду при цьому вибиратиме один з двох мультиплексорів. Так само з двох 16-канальних мультиплексорів можна зробити 32-канальний. Якщо потрібне більше число каналів, то необхідно замість інвертора включати дешифратор, на який подаються старші розряди коду. Вихідні сигнали дешифратора вибиратимуть один з мультиплексорів. На рис. 8 Зображено одно розрядний, восьми канальний мультиплексом побудований на основі двох чотириканальних. Принцип роботи схеми полягає в наступному: при появі на адресній лінії А2 активного сигналу він відключає мультиплексом першого каскаду U1 який відповідає за молодші канали. Далі сигнал лінії А2 поступає на інвертор та дозволяє роботу мультиплексору U2. Адресні лінії молодших розрядів подаються на обидва мультиплексори паралельно, так як працює лише один з них на виході з’являється сигнал з входу, що відповідає коду.

Рис. 8 Мультиплексор на побудований на основі схем з меншою кількістю входів

Мультиплексор можна використовувати як основу для синтезу комбінаційних схем із довільною таблицею істинності. В цьому випадку виходячи з таблиці істинності на вхідні канали мультиплексора подаються активні сигнали. При подачі різних комбінацій сигналів на адресні входи мультиплексора на його виході буде з’являтися або зникати активний сигнал перетворюючи його на комбінаційну схему.

Нехай дано наступну таблицю істинності:

X1 |

X2 |

X3 |

Y |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

Як видно, при комбінації вхідних сигналів, що відповідають 0, 2, 3, 5, 6, 7 вихідний сигнал повинен становити логічну 1. Схема, що реалізує представлену таблицю істинності наведено на рис. 9

Рис 9. Комбінаційна схема реалізована на мультиплексорі