- •Индивидуальное задание по теме: Организация памяти в защищённом режиме работы микропроцессора

- •Самостоятельная работа По теме: “Организация памяти в защищённом режиме работы микропроцессора.”

- •1Уровень

- •2 Уровень

- •Ответы Самостоятельная работа По теме: “Организация памяти в защищённом режиме работы микропроцессора.”

- •1Уровень

- •2 Уровень

Индивидуальное задание по теме: Организация памяти в защищённом режиме работы микропроцессора

Цель урока:

сформировать знания о работе процессора с памятью в защищённом режиме;

дать понятие о базовой терминологии защищённого режима;

сформировать понятие о виртуальном адресном пространстве, порядке определения его объёма;

дать понятие о порядке определения физического адреса ячейки памяти при включённой страничной адресации;

Основные понятия защищённого режима:

Селектор - это узел в составе устройства-исполнителя для распознавания адреса в циклах обмена по магистрали.

Дескриптор сегмента – это служебная структура в памяти, которая определяет сегмент. Длина дескриптора равна восьми байтам.

Дескрипторные таблицы — это служебные структуры данных, содержащие дескрипторы сегментов.

Cтраница— это блоки фиксированного размера, на которые делится как физическая, так и виртуальная память, причём выделение памяти и передача данных между диском и оперативной памятью осуществляется целыми страницами.

Виртуальный адрес – это адреса команд и переменных в готовой машинной программе, подготовленной к выполнению системой программирования.

Линейный адрес – это адрес образующийся сложением базового адреса сегмента с эффективным адресом.

Физический адрес — это адрес, по которому производится реальное обращение к памяти.

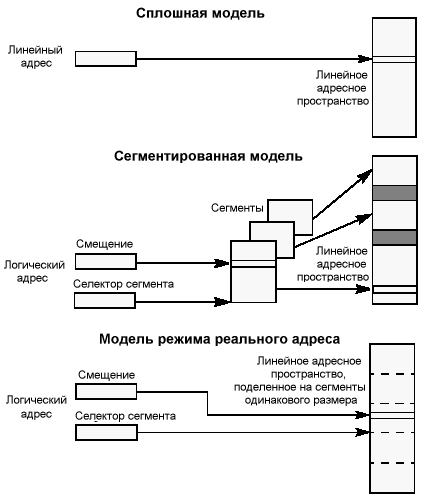

Сегментная организация памяти в реальном и виртуальном режиме:

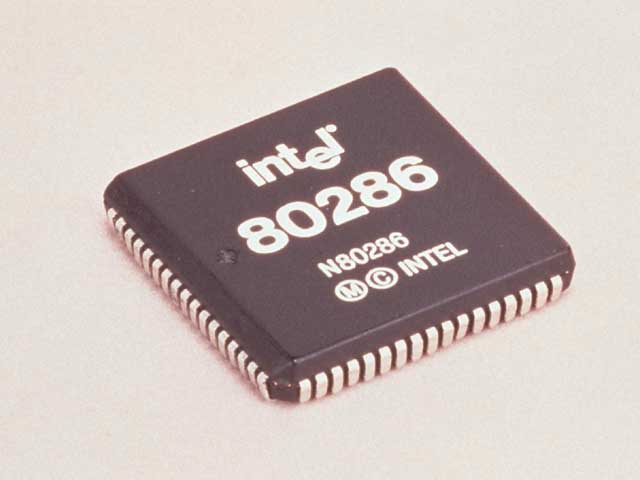

Реальный режим (или режим реальных адресов) — это название было дано прежнему способу адресации памяти после появления процессора 80286, поддерживающего защищённый режим. Но только с появлением процессора 80386 можно говорить о защищённом режиме в современном понимании, так как в процессоре 80286 нет страничной адресации памяти.

Описание

В

реальном режиме при вычислении линейного

а дреса,

по которому процессор собирается читать

содержимое памяти или писать в неё,

сегментная часть адреса умножается на

16 (или, что то же самое, сдвигается влево

на 4 бита) и суммируется со смещением

(если процессору передаётся не полный

адрес из двух 16-битных значений —

сегмента и смещения, — а только 16-битное

смещение, то сегмент берётся из одного

из сегментных регистров). Таким образом,

адреса 0400h:0001h и 0000h:4001h ссылаются на один

и тот же физический адрес, так как

400h×16+1 = 0×16+4001h.

дреса,

по которому процессор собирается читать

содержимое памяти или писать в неё,

сегментная часть адреса умножается на

16 (или, что то же самое, сдвигается влево

на 4 бита) и суммируется со смещением

(если процессору передаётся не полный

адрес из двух 16-битных значений —

сегмента и смещения, — а только 16-битное

смещение, то сегмент берётся из одного

из сегментных регистров). Таким образом,

адреса 0400h:0001h и 0000h:4001h ссылаются на один

и тот же физический адрес, так как

400h×16+1 = 0×16+4001h.

Такой способ вычисления физического адреса позволяет адресовать 1 Мб + 64 Кб − 16 байт памяти (диапазон адресов 0000h…10FFEFh). Однако в процессорах 8086/8088 всего 20 адресных линий, поэтому реально доступен только 1 мегабайт (диапазон адресов 0000h…FFFFFh), а при адресации выше (в диапазоне 100000h…10FFEFh) происходит «заворот» — старший единичный бит адреса игнорируется и доступ идёт к 64 килобайтам в начальных адресах (0000h…FFEFh).

В процессорах 80286/80288 адресная шина 24-битная (возможна адресация 224 = 16 Мб памяти), поэтому в них переполнения не происходит. Компьютеры IBM PC/AT построены на процессоре Intel 80286, но из соображений совместимости с IBM PC и IBM PC/XT, построенных на Intel 808x, в них был введён логический элемент (вентиль), отключающий 21-й адресный провод (A20) от схемы управления памятью. Этот логический элемент (Gate A20) управляется через контроллер клавиатуры (микросхема Intel 8042) и по умолчанию он включён.

Использование

В реальном режиме процессоры работали

только в DOS. Адресовать в реальном режиме

дополнительную память за пределами 1 М

б нельзя (хотя можно использовать

драйвера вроде HIMEM.SYS на машинах с

процессором 80286 и выше). Несмотря на то,

что фирма Intel не предусмотрела возврат

процессора из защищённого в реальный

режим, она обеспечила совместимость

16-битных программ, введя ещё один

специальный режим — режим виртуальных

адресов V86. При этом программы получают

возможность использовать прежний способ

вычисления линейного адреса, в то время

как процессор находится в защищённом

режиме. Режим V86 позволил организовать

работу DOS внутри многозадачных систем

вроде OS/2 и Microsoft Windows.

реальном режиме процессоры работали

только в DOS. Адресовать в реальном режиме

дополнительную память за пределами 1 М

б нельзя (хотя можно использовать

драйвера вроде HIMEM.SYS на машинах с

процессором 80286 и выше). Несмотря на то,

что фирма Intel не предусмотрела возврат

процессора из защищённого в реальный

режим, она обеспечила совместимость

16-битных программ, введя ещё один

специальный режим — режим виртуальных

адресов V86. При этом программы получают

возможность использовать прежний способ

вычисления линейного адреса, в то время

как процессор находится в защищённом

режиме. Режим V86 позволил организовать

работу DOS внутри многозадачных систем

вроде OS/2 и Microsoft Windows.

С труктура

адресного пространства IBM PC в реальном

режиме

труктура

адресного пространства IBM PC в реальном

режиме

Основная область памяти

В область, называемую основной областью памяти (англ. conventional memory), загружается таблица векторов прерываний, различные данные BIOS, а также могут загружаться 16-битные программы DOS. Основная область памяти занимает 640 Кбайт начиная с адреса 0000:0000.

Upper Memory Area

Upper Memory Area (UMA) занимает 384 Кбайт и используется для размещения информации об аппаратной части компьютера. Область условно делится на три области по 128 Кбайт. Первая область служит для видеопамяти. Через вторую область доступны BIOS адаптеров. Третья область используется системной BIOS, но, как правило, не полностью (обычно остаётся 64 Кбайт). Остальное адресное пространство из верхней области с помощью специальных драйверов (например, EMM386.EXE, EMS.EXE, LIMEMS.EXE и т. п.) и/или устройств расширения может использоваться для доступа к расширенной памяти через спецификацию расширенной памяти (англ. Expanded Memory Specification, EMS).

Дополнительная область памяти

Дополнительная память для 16-битных программ доступна через спецификацию дополнительной памяти (англ. eXtended Memory Specification, XMS). Дополнительная память начинается с адресов выше первого мегабайта и её объём зависит от общего объёма оперативной памяти, установленной на компьютере.

High Memory Area

High Memory Area (HMA) — это область дополнительной памяти сразу за первым мегабайтом размером 64 Кбайт минус 16 байт. Её появление обусловлено особенностью процессора 80286, в котором 24 линии адреса и при обращении по адресам выше FFFF:000F обращение идёт ко второму мегабайту памяти (вместо начала первого мегабайта, как в 8086/8088). Таким образом, программы реального режима получили доступ к HMA.

Режим виртуального 8086

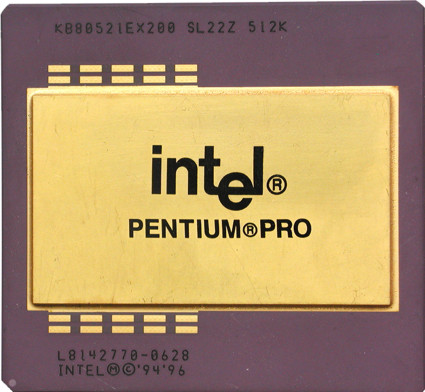

Процессор семейства х86

Режим

виртуального 8086 (V86, VM86, иногда просто

виртуальный режим) — режим адресации

процессоров семейства x86 совместимый

с прародителем семейства — процессором

Intel 8086. Является подрежимом защищенного.

Впервые появился в процессоре 80386 и

предназначался главным образом для

создания т. н. «виртуальных DOS-машин»,

виртуальных сред для исполнения

приложений господствовавшей в то время

в мире персональных ЭВМ операционной

системы MS-DOS. Является первой попыткой

корпорации Intel внедрить в свои процессоры

технологии аппаратной виртуализации.

Режим

виртуального 8086 (V86, VM86, иногда просто

виртуальный режим) — режим адресации

процессоров семейства x86 совместимый

с прародителем семейства — процессором

Intel 8086. Является подрежимом защищенного.

Впервые появился в процессоре 80386 и

предназначался главным образом для

создания т. н. «виртуальных DOS-машин»,

виртуальных сред для исполнения

приложений господствовавшей в то время

в мире персональных ЭВМ операционной

системы MS-DOS. Является первой попыткой

корпорации Intel внедрить в свои процессоры

технологии аппаратной виртуализации.

Особенности

Задача виртуального 8086 представляет собой обычную задачу защищенного режима со следующими особенностями:

Режим активируется установкой флажка EFLAGS.VM с помощью привилегированной инструкции (IRET, JMP <task>) (непривилегированная команда POPF, даже исполняясь на уровне привилегий 0, состояния этого флажка не изменяет).

Адрес, аналогично реальному режиму, является двухкомпонентным, состоящим из 16-битного номера 16-байтного параграфа, задающего базовый адрес сегмента и 16-битного смещения внутри сегмента;

Исходя из формата адреса, возможна адресация только нижнего мегабайта памяти (+65520 байт HMA); однако, благодаря страничному отображению, в эту область могут быть отображены произвольные страницы памяти, что позволяет организовать мультизадачность для задач DOS;

Задача исполняется с самыми низкими привилегиями в кольце 3.

Прерывания обрабатываются обычными обработчиками ОС защищенного режима. Таблица векторов прерываний по адресу 0 не используется (если не активно расширение VME). Модуль операционной системы, часто называемый V86-монитором, может эмулировать прерывание реального режима, программно обращаясь к этой таблице;

Меняется значение поля EFLAGS.IOPL. В режиме V86 оно используется для перехвата некоторых инструкций (CLI, STI, PUSHF, POPF, INT, IRET), а для перехвата ввода/вывода требуется использование битовой карты разрешения портов в сегменте состояния задачи;

Расширения

Начиная

с процессора Pentium в режим V86 были введены

опциональные функции: таблица

перенаправления прерываний и виртуализация

флажка прерываний. Теперь процессор,

без вмешательства ОС мог непосредственно

использовать таблицу векторов прерываний

по адресу 0, причем не для всех прерываний,

а только для тех, что разрешила операционная

система с помощью специальной битовой

карты (аналогичной карте ввода/вывода)

в сегменте состояния задачи. Виртуализация

флажка прерываний также уменьшает число

исключительных ситуаций, требующих

программной обработки операционной

системой, что, в свою очередь, сказывается

на общей производительности.

Начиная

с процессора Pentium в режим V86 были введены

опциональные функции: таблица

перенаправления прерываний и виртуализация

флажка прерываний. Теперь процессор,

без вмешательства ОС мог непосредственно

использовать таблицу векторов прерываний

по адресу 0, причем не для всех прерываний,

а только для тех, что разрешила операционная

система с помощью специальной битовой

карты (аналогичной карте ввода/вывода)

в сегменте состояния задачи. Виртуализация

флажка прерываний также уменьшает число

исключительных ситуаций, требующих

программной обработки операционной

системой, что, в свою очередь, сказывается

на общей производительности.

V86 и x86-64

Процессоры с архитектурой x86-64 поддерживают V86 только в наследственном, но не в длинном режиме. В длинном режиме флажок EFLAGS.VM попросту игнорируется. Поэтому, для поддержки виртуальных DOS-задачи требуется переключение в наследственный режим, сопряженное с двойным сбросом MMU. А поскольку роль DOS и её приложений в наши дни практически сошла на нет, операционные системы x86-64 не включают такого рода поддержку V86. Тем не менее, некоторые современные средства аппаратной виртуализации позволяют виртуализовать как реальный режим, так и V86, получая в результате двойную виртуализацию.

Поддержка операционными системами

M S-DOS — В DOS режим V86 использовался для эмуляции дополнительной памяти по стандарту LIM/EMS при помощи специального драйвера EMM386. Поскольку в этом режиме, в отличие от реального, возможна трансляция страниц, дополнительная память эмулировалась с помощью отображения расширенной в окно адресов UMB/EMS. Также драйвер позволял в адресах UMB размещать данные и резидентные программы.

OS/2 — В составе OS/2 имелась штатная виртуальная DOS-машина.

W indows

— В составе Windows начиная с версии 3.0

появился 386 расширенный режим, который

позволял позволял создавать V86-задачи

для программ DOS («DOS в окне»).

indows

— В составе Windows начиная с версии 3.0

появился 386 расширенный режим, который

позволял позволял создавать V86-задачи

для программ DOS («DOS в окне»).

Linux

— ОС Linux/x86 поддерживается системный

вызов vm86() которым активно пользуется

программа DOSEMU — свободная реализация

виртуальной DOS-машины (в последнее время

вытесненяемая эмулятором DOSBox, поскольку

эмуляция, несмотря на большие ресурсозатраты

более точно имитирует работу компьютера,

что было важно для программ того времени,

довольно часто обращающихся к аппаратным

средствам непосредственно).

Linux

— ОС Linux/x86 поддерживается системный

вызов vm86() которым активно пользуется

программа DOSEMU — свободная реализация

виртуальной DOS-машины (в последнее время

вытесненяемая эмулятором DOSBox, поскольку

эмуляция, несмотря на большие ресурсозатраты

более точно имитирует работу компьютера,

что было важно для программ того времени,

довольно часто обращающихся к аппаратным

средствам непосредственно).

FreeBSD

— В ОС FreeBSD/i386 имеется поддержка V86 и

встренная программа doscmd, обладающая

гораздо меньшими возможностями, чем

DOSEMU, поэтому практически не используемая.

FreeBSD

— В ОС FreeBSD/i386 имеется поддержка V86 и

встренная программа doscmd, обладающая

гораздо меньшими возможностями, чем

DOSEMU, поэтому практически не используемая.

Механизм определения линейного и физического адреса при использовании страничной адресации памяти:

Basic Input-Output System

Линейный адрес, который формируется п роцессором

из логического адреса, соответствует

адресу из линейного непрерывного

пространства памяти. В обычном режиме

в это пространство могут попадать

области памяти, в которые нежелательно

разрешать запись, — системные таблицы

и процедуры, ПЗУ BIOS и т.д. Чтобы этого

избежать, система может разрешать

программам создавать только небольшие

сегменты, но тогда теряется такая

привлекательная идея flat-памяти.

Сегментация — не единственный вариант

организации памяти, который поддерживают

процессоры Intel. Существует второй,

совершенно независимый механизм —

страничная адресация (pagination).

роцессором

из логического адреса, соответствует

адресу из линейного непрерывного

пространства памяти. В обычном режиме

в это пространство могут попадать

области памяти, в которые нежелательно

разрешать запись, — системные таблицы

и процедуры, ПЗУ BIOS и т.д. Чтобы этого

избежать, система может разрешать

программам создавать только небольшие

сегменты, но тогда теряется такая

привлекательная идея flat-памяти.

Сегментация — не единственный вариант

организации памяти, который поддерживают

процессоры Intel. Существует второй,

совершенно независимый механизм —

страничная адресация (pagination).

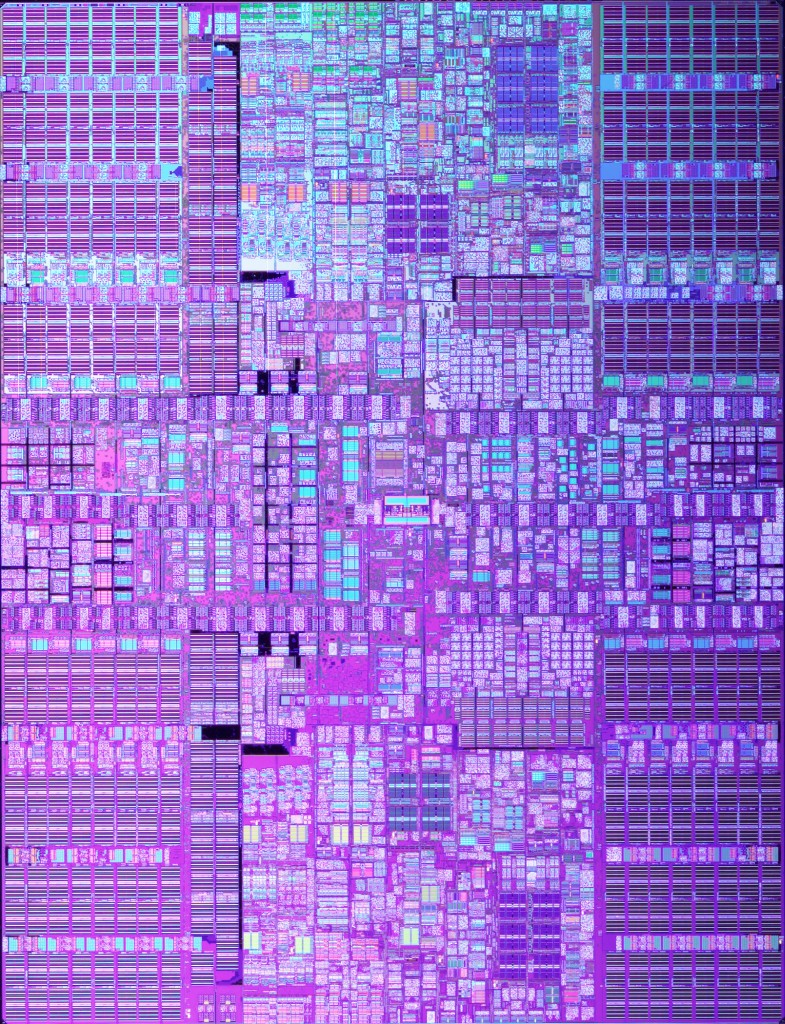

При страничной адресации непрерывное пространство линейных адресов памяти разбивается на страницы фиксированного размера (обычно 4 Кб (4096 или 1000h байт), но Pentium Pro может поддерживать и страницы по 4 Мб). При обращении к памяти процессор физически обращается не по линейному адресу, а по тому физическому адресу, с которого начинается данная страница. Описание каждой страницы из линейного адресного пространства, включающее в себя ее физический адрес и дополнительные атрибуты, хранится в одной из специальных системных таблиц, как и в случае сегментации, но в отличие от сегментации страничная адресация абсолютно невидима для программы.

Страничная адресация включается при установке бита PG регистра CR0, если бит РЕ установлен в 1 (попытка установить PG, оставаясь в реальном режиме, приводит к исключению #GP(0)). Кроме того, предварительно надо поместить в регистр CR3 физический адрес начала каталога страниц — главной из таблиц, описывающих страничную адресацию. Каталог страниц имеет размер 4096 байт (ровно одна страница) и содержит 1024 4-байтных указателя на таблицы страниц. Каждая таблица страниц тоже имеет размер 4096 байт и содержит указатели до 1024 4-килобайтных страниц. Если одна страница описывает 4 килобайта, то полностью заполненная таблица страниц описывает 4 мегабайта, а полный каталог полностью заполненных таблиц — 4 гигабайта, то есть все 32-битное линейное адресное пространство. Когда процессор выполняет обращение к линейному адресу, он сначала использует его биты 31 – 22 как номер таблицы страниц в каталоге, затем биты 21 – 12 как номер страницы в выбранной таблице, а затем биты 11 – 0 как смещение от физического адреса начала страницы в памяти. Так как этот процесс занимает достаточно много времени, в процессоре предусмотрен специальный кэш страниц — TLB (буфер с ассоциативной выборкой), так что, если к странице обращались не очень давно, процессор определит ее физический адрес сразу.

Элементы каталога страниц и таблиц страниц имеют общий формат:

биты 31 – 12: биты 31 – 12 физического адреса (таблицы страниц или самой страницы)

биты 11 – 9: доступны для использования операционной системой

бит 8: G — «глобальная страница» — страница не удаляется из буфера TLB при переключении задач или перезагрузке регистра CR3 (только на Pentium Pro, если установлен бит PGE регистра CR4)

бит 7: PS — размер страницы. 1 — для страницы размером 2 или 4 мегабайта, иначе — 0

бит 6: D — «грязная страница» — устанавливается в 1 при записи в страницу; всегда равен нулю для элементов каталога страниц

бит 5: А — бит доступа (устанавливается в 1 при любом обращении к таблице страниц или отдельной странице)

бит 4: PCD — бит запрещения кэширования

бит 3: PWT — бит разрешения сквозной записи

бит 2: U — страница/таблица доступна для программ с CPL = 3

бит 1: W — страница/таблица доступна для записи

бит 0: Р — страница/таблица присутствует. Если этот бит — 0, остальные биты элемента система может использовать по своему усмотрению, например, чтобы хранить информацию о том, где физически находится отсутствующая страница

Процессоры

Pentium Pro (и старше) могут поддерживать

расширения страничной адресации. Если

установлен бит РАЕ, физический адрес

оказывается не 32-битным (до 4 Гб), а

36-битным (до 64 Гб). Если установлен бит

PSE регистра CR4, включается поддержка

расширенных страниц размером 4 Мб для

РАЕ = 0 и 2 Мб для РАЕ = 1. Такие страницы

описываются не в таблицах страниц, а

прямо в основном каталоге. Intel рекомендует

помещать ядро операционной системы и

все, что ему необходимо для работы, на

одну 4-мегабайтную страницу, а для

приложений пользоваться 4-килобайтными

страницами. Расширенные страницы

кэшируются в отдельном TLB, так что, если

определена всего одна расширенная

страница, она будет оставаться в TLB все

время.

Процессоры

Pentium Pro (и старше) могут поддерживать

расширения страничной адресации. Если

установлен бит РАЕ, физический адрес

оказывается не 32-битным (до 4 Гб), а

36-битным (до 64 Гб). Если установлен бит

PSE регистра CR4, включается поддержка

расширенных страниц размером 4 Мб для

РАЕ = 0 и 2 Мб для РАЕ = 1. Такие страницы

описываются не в таблицах страниц, а

прямо в основном каталоге. Intel рекомендует

помещать ядро операционной системы и

все, что ему необходимо для работы, на

одну 4-мегабайтную страницу, а для

приложений пользоваться 4-килобайтными

страницами. Расширенные страницы

кэшируются в отдельном TLB, так что, если

определена всего одна расширенная

страница, она будет оставаться в TLB все

время.

Для расширенных страниц формат элемента каталога совпадает с форматом для обычной страницы (кроме того, что бит PS = 1), но в качестве адреса используются только биты 31 – 22 — они соответствуют битам 31 – 22 физического адреса начала страницы (остальные биты адреса — нули).

Для расширенного физического адреса (РАЕ = 1) изменяется формат регистра CR3, размеры всех элементов таблиц становятся равными 8 байтам (причем используются только биты 0 – 3 байта 4), так что их число сокращается до 512 элементов в таблице и вводится новая таблица — таблица указателей на каталоги страниц. Она состоит из четырех 8-байтных элементов, каждый из которых может указывать на отдельный каталог страниц. В этом случае биты 31 – 30 линейного адреса выбирают используемый каталог страниц, биты 29 – 21 — таблицу, биты 20 – 12 — страницу, а биты 11 – 0 — смещение от начала страницы в физическом пространстве (следовательно, если биты 29 – 21 выбрали расширенную страницу, биты 20 – 0 соответствуют смещению в ней).

Основная цель страничной адресации — организация виртуальной памяти в операционных системах. Система может использовать внешние устройства — обычно диск — для расширения виртуального размера памяти. При этом, если к какой-то странице долгое время нет обращений, система копирует ее на диск и помещает отсутствующей в таблице страниц. Затем, когда программа обращается по адресу в отсутствующей странице, вызывается исключение #РЕ Обработчик исключения читает адрес, вызвавший ошибку из CR2, определяет, какой странице он соответствует, загружает ее с диска, устанавливает бит присутствия, удаляет копию старой страницы из TLB командой INVLPG и возвращает управление (не забыв снять со стека код ошибки). Команда, вызывавшая исключение типа ошибки, выполняется повторно.

Кроме того, система может периодически сбрасывать бит доступа и, если он не установится за достаточно долгое время, копировать страницу на диск и объявлять ее отсутствующей. Если при этом бит D равен нулю, в страницу не выполнялось никаких записей (с того момента, как этот бит последний раз обнулили) и ее вообще можно не сохранять.

Второе

не менее важное применение страничной

адресации — безопасная реализация

flat-модели памяти. Операционная система

может разрешить программам обращаться

к любому линейному адресу, но отображение

линейного пространства на физическое

не будет взаимно однозначным. Скажем,

если система использует первые 4 Кб

памяти, физическим адресом нулевой

страницы будет не ноль, а 4096 и

пользовательская программа даже не

узнает, что обращается не к нулевому

адресу. В этом случае, правда, и сама

система не сможет обращаться к первой

физической странице без изменения

таблицы страниц, но эта проблема решается

при применении механизма многозадачности.

Второе

не менее важное применение страничной

адресации — безопасная реализация

flat-модели памяти. Операционная система

может разрешить программам обращаться

к любому линейному адресу, но отображение

линейного пространства на физическое

не будет взаимно однозначным. Скажем,

если система использует первые 4 Кб

памяти, физическим адресом нулевой

страницы будет не ноль, а 4096 и

пользовательская программа даже не

узнает, что обращается не к нулевому

адресу. В этом случае, правда, и сама

система не сможет обращаться к первой

физической странице без изменения

таблицы страниц, но эта проблема решается

при применении механизма многозадачности.

Особенности сегментной, страничной и сегментно-страничной организации памяти в защищённом режиме:

Основная трудность, с которой сталкивается программист, изучающий защищённый режим - это сложная схема преобразования адресов. Поэтому мы уделим много внимания тому, как в этом режиме происходит адресация памяти.

Преобразование адресов в защищённом режиме

В защищённом режиме, также как и в реальном, существуют понятия логического и физического адреса. Логический адрес в защищённом режиме (иногда используется термин "виртуальный адрес") состоит из двух 16-разрядных компонент - селектора и смещения. Селектор записывается в те же сегментные регистры, что и сегментный адрес в реальном режиме. Однако преобразование логического адреса в физический выполняется не простым сложением со сдвигом, а при помощи специальных таблиц преобразования адресов.

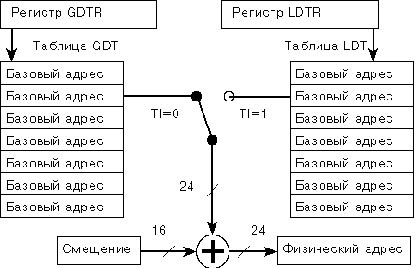

В первом приближении можно считать, что для процессора i80286 селектор является индексом в таблице, содержащей базовые 24-разрядные физические адреса сегментов. В процессе преобразования логического адреса в физический процессор прибавляет к базовому 24-разрядному адресу 16-разрядное смещение, т.е. вторую компоненту логического адреса.

На рисунке показана сильно упрощённая схема преобразования логического адреса в физический.

Такая схема формирования физического адреса позволяет непосредственно адресовать 16 мегабайт памяти с помощью 16-разрядных компонент логического адреса.

Заметьте, что селектор - это не сегментный адрес. Это индекс, с помощью которого процессор извлекает из специальной таблицы 24-разрядный базовый адрес сегмента. В реальном режиме мы имеем дело с сегментным адресом и смещением, а в защищённом - с селектором и смещением.

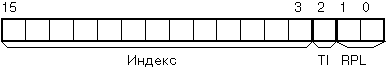

На самом деле не все 16 бит селектора используются для индексации по таблице базовых адресов. В качестве индекса выступают старшие 13 бит. Два младших бита (бит 0 и бит 1) используются системой защиты памяти, о чём мы подробно поговорим в следующем разделе. Бит 2 позволяет выбирать для преобразования адреса один из двух типов таблиц преобразования адресов.

Формат селектора адреса.

На этом рисунке два младших бита обозначены как RPL (Requested Privilege Level). Это поле является запрошенным программой уровнем привилегий и его мы будем обсуждать позже. Поле TI (Table Indicator) состоит из одного бита. Если этот бит равен нулю, для преобразования адреса используется так называемая глобальная таблица дескрипторов GDT (Global Descriptor Table), в противном случае - локальная таблица дескрипторов LDT (Local Descriptor Table).

Таблица дескрипторов - это просто таблица преобразования адресов, содержащая базовые 24-разрядные физические адреса сегментов и некоторую другую информацию. То есть каждый элемент таблицы дескрипторов (дескриптор) содержит 24-разрядный базовый адрес сегмента и другую информацию, описывающую сегмент.

Таблица GDT - единственная в системе. Обычно в ней находятся описания сегментов операционной системы. Таблиц LDT может быть много. Эти таблицы содержат описания сегментов программ, работающих под управлением операционной системы, т.е. отдельных задач. В каждый данный момент времени процессор может использовать только одну таблицу LDT.

Процессор имеет два регистра, предназначенных для адресации используемых в настоящий момент таблиц GDT и LDT. Регистр GTDR описывает расположение и размер таблицы GDT, а регистр LDTR содержит ссылку на использующуюся в настоящее время таблицу LDT.

На рисунке показана уточнённая схема преобразования адресов в защищённом режиме. Из рисунка видно, что регистры процессора GDTR и LDTR определяют расположение в памяти таблиц GDT и LDT соответственно. Таблицы GDT и LDT содержат дескрипторы, описывающие сегменты памяти. В этих дескрипторах, помимо другой информации (заштрихованная область) содержится 24-разрядный базовый адрес сегмента.

Старшие 13 битов селектора (индекс) выбирают элемент из таблицы GDT или LDT в зависимости от состояния бита TI селектора.

Извлечённый из таблицы дескрипторов базовый адрес сегмента складывается процессором для получения 24-разрядного физического адреса.

Уточнённая схема преобразования адресов.

Селектор 0000h адресует самый первый дескриптор в глобальной таблице дескрипторов GDT. Поле RPL для этого дескриптора равно 0, поле TI также равно 0. Селектор 0008h указывает на второй элемент таблицы GDT, а селектор 0014h указывает на третий дескриптор в локальной таблице дескрипторов LDT, т.к. поле TI в нём равно 1.

Детальное описание схемы преобразования адресов

Теперь перейдём к более строгому описанию схемы преобразования адресов в защищённом режиме.

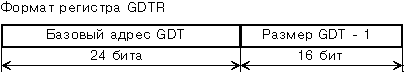

Регистр GDTR, указывающий расположение в физической памяти и размер глобальной таблицы дескрипторов GDT является ключевым в схеме адресации защищённого режима.

Формат регистра GDTR процессора i80286 приведён на рисунке.

Формат регистра GDTR процессора i80286.

Из рисунка видно, что регистр GDTR имеет длину 5 байт. Старшие 3 байта содержат 24-разрядный физический адрес таблицы GDT, младшие два байта - длину таблицы GDT, уменьшенную на 1.

Длина GDT, уменьшенная на единицу, называется пределом таблицы GDT (GDT limit). Она используется для проверки правильности задаваемых программой селекторов. Поле индекса селектора должно содержать ссылки только на существующие элементы таблицы GDT, в противном случае произойдет прерывание. Зная размер GDT, процессор блокирует использование селекторов со значениями поля индекса, выходящее за рамки разрешённых для таблицы GDT. Аналогичный механизм используется и для проверки селекторов, ссылающихся на LDT.

Перед переходом в защищённый режим программа должна создать в оперативной памяти таблицу GDT и загрузить регистр GDTR при помощи специальной команды LGDT (синтаксис транслятора Turbo Assembler, режим IDEAL):

lgdt [QWORD gdt_ptr]

Перед выдачей команды LGDT gdt_ptr необходимо подготовить область памяти с адресом gdt_ptr, записав в неё физический адрес таблицы GDT и её размер, уменьшенный на 1 (предел):

gdt_ptr dw GDT_LIMIT ; предел таблицы GDT

base_lo dw ? ; младшее слово базового адреса GDT

base_hi dw ? ; старшее слово базового адреса GDT

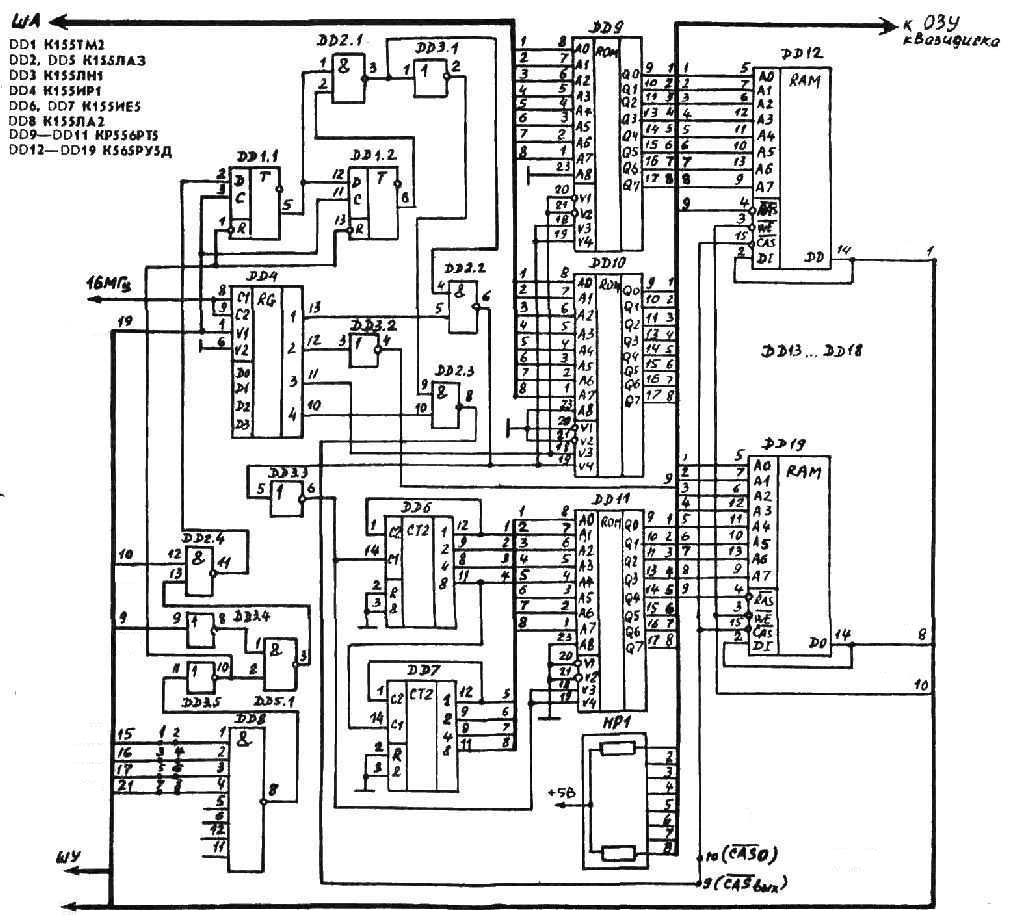

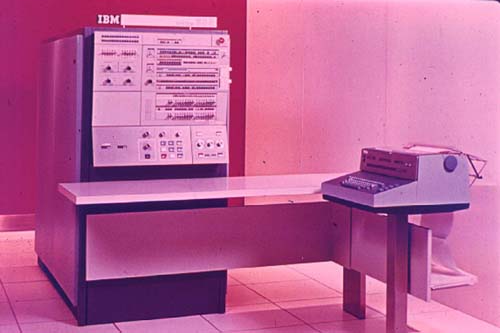

Структура микропроцессора i80286

Заметьте, что несмотря на то что размер регистра GDTR составляет 5 байт, в качестве операнда для команды LGDT используется адрес области памяти размером 6 байт. Здесь нет никакой ошибки, процессор i80286 использует только 5 байт из этой области, так как физический адрес содержит 24 разряда. Процессоры i80386 и i80486 в 32-разрядном режиме используют все 6 байтов, загружая в 6-байтный регистр GDTR 32-битовый физический адрес таблицы GDT и её 16-битовый предел.

Однако мы ещё не знаем точную структуру таблицы GDT. Сначала мы познакомим вас со структурой таблицы GDT (и соответственно, с идентичной ей структурой таблицы LDT), а затем на примере фрагмента программы покажем, как создать таблицу GDT и загрузить регистр GDTR.

Как мы уже говорили, таблицы GDT и LDT представляют собой массивы дескрипторов - описателей сегментов. Кроме дескрипторов, описывающих сегменты памяти, таблица GDT может содержать специальные типы дескрипторов - вентили вызова (call gate), задач (task gate) и ловушек (trap gate).

Вентили определяют точки входа в соответствующие процедуры. Например, вентиль вызова в описывает адрес подпрограммы, вызываемой, например, по команде CALL. При вызове подпрограммы через вентиль в качестве операнда для команды CALL используется селектор, адресующий соответствующий дескриптор в таблице GDT (или таблице LDT).

На рисунке приведён формат дескриптора сегмента для процессора i80286:

![]()

Дескриптор сегмента для процессора i80286.

Длина дескриптора составляет 8 байт. Он состоит из следующих полей:

поле базового адреса длиной 24 бита содержит физический адрес сегмента, описываемого данным дескриптором;

поле предела содержит размер сегмента в байтах, уменьшенный на единицу;

поле доступа описывает тип сегмента (сегмент кода, сегмент данных и др.);

зарезервированное поле длиной 16 бит для процессора i80286 должно содержать нули, это поле используется процессорами i80386 и i80486 (там, в частности, хранится старший байт 32-разрядного базового адреса сегмента).

В реальном режиме начало сегмента в памяти определяется сегментным адресом, длина сегмента составляет 64 килобайта. В защищённом режиме можно задавать сегменты меньшего размера (процессоры i80386 и i80486 допускают также существование сегментов с размером, значительно превышающим 64 килобайта). При этом процессор автоматически отслеживает попытки программы обратиться за пределы сегмента, заданные в дескрипторе. При обнаружении такой попытки выполнение программы прерывается.

Ограничение размера сегментов и контроль за попытками адресации памяти вне пределов сегментов сильно повышает надёжность системы. Программа не может разрушить чужие сегменты, в частности, сегменты операционной системы. Подробнее о защите мы расскажем в следующем разделе.

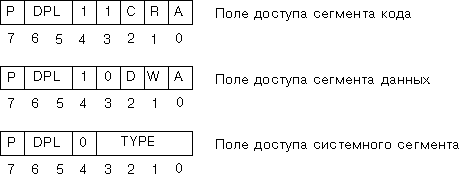

Поле доступа, занимающее в дескрипторе один байт (байт доступа) служит для классификации дескрипторов. На рисунке приведены форматы поля доступа для трёх типов дескрипторов - дескрипторов сегментов кода, сегментов данных и системных.

Форматы поля доступа дескриптора.

Поле доступа дескриптора сегментов кода содержит битовое поле R, называемое битом разрешения чтения сегмента. Если этот бит установлен в 1, программа может считывать содержимое сегмента кода. В противном случае процессор может только выполнять этот код.

Программа не может модифицировать сегмент кода. Это означает невозможность создания самомодифицирующихся программ для защищённого режима (распространённая, но порочная практика среди программистов, создающих программы для MS-DOS). Впрочем, есть обходной путь. Для сегмента кода можно создать ещё один, алиасный дескриптор, в котором этот сегмент отмечен как сегмент данных. Если для этого сегмента будет разрешена запись, ничто, кроме здравого смысла, не помешает вам модифицировать код программы во время её выполнения.

Бит C называется битом подчинения, он будет рассмотрен в следующем разделе.

Биты P и A предназначены для организации виртуальной памяти. Их назначение будет описано в разделе, посвящённом виртуальной памяти. Сейчас отметим, что бит P называется битом присутствия сегмента в памяти. Для тех сегментов, которые находятся в физической памяти (мы будем иметь дело в основном с такими сегментами) этот бит должен быть установлен в 1.

Любая попытка программы обратиться к сегменту памяти, в дескрипторе которого бит P установлен в 0, приведёт к прерыванию.

Бит A называется битом обращения к сегменту и для всех наших программ должен быть установлен в 0.

Поле доступа дескриптора сегмента данных имеет битовые поля W и D. Поле W называется битом разрешения записи в сегмент. Если этот бит установлен в 1, наряду с чтением возможна и запись в данный сегмент. В противном случае при попытке чтения выполнение программы будет прервано.

Поле D задаёт направление расширения сегмента. Обычный сегмент данных расширяется в область старших адресов (расширение вверх). Если же в сегменте расположен стек, расширение происходит в обратном направлении - в область младших адресов (расширение вниз). Для сегментов, в которых организуются стеки, необходимо устанавливать поле D равным 1.

Дескрипторы системных сегментов содержат поле TYPE, определяющее тип системного сегмента. В таблице 1 приведены возможные для этого поля значения

Таблица 1. Типы системных сегментов.

Поле TYPE Тип сегмента

0 Запрещённое значение

1 Доступный TSS для процессора i80286

2 Сегмент LDT

3 Занятый TSS для процессора i80286

4 Вентиль вызова для процессора i80286

5 Вентиль задачи для процессоров i80286 и i80386

6 Вентиль прерывания для процессора i80286

7 Вентиль исключения для процессора i80286

8 Запрещённое значение

9 Доступный TSS для процессора i80386

A Зарезервировано

B Занятый TSS для процессора i80386

C Вентиль вызова для процессора i80386

D Зарезервировано

E Вентиль прерывания для процессора i80386

F Вентиль ловушки для процессора i80386

Мы на время отложим детальное описание всех типов системных дескрипторов, так же как и поля DPL, использующееся для организации защиты сегментов, для того чтобы сконцентрировать своё внимание на схеме преобразования адресов в процессоре i80286.

Итак, перед переводом процессора в защищённый режим нам необходимо сформировать в памяти таблицу GDT и загрузить в регистр GTDR её адрес и предел при помощи команды LGDT.

В терминах языка ассемблера структура дескриптора может быть описана следующим образом:

STRUC desc_struc

limit dw 0 ; предел сегмента

base_lo dw 0 ; младшее слово 24-битового

; физического адреса сегмента

base_hi db 0 ; старший байт 24-битового

; физического адреса сегмента

access db 0 ; поле доступа

reserved dw 0 ; зарезервировано, для сегментов

; процессора i80286 должно быть

; равно нулю

ENDS desc_struc

Тогда мы можем определить таблицу GDT как набор дескрипторов со структурой desc_struc:

GDT_BEG = $ ; отмечаем начало GDT

LABEL gdtadr WORD

gdt_0 desc_struc <0,0,0,0,0>;первый элемент

;не используется

gdt_gdt desc_struc

gdt_ds desc_struc

gdt_cs desc_struc

gdt_ss desc_struc

GDT_SIZE = ($ - GDT_BEG) ; вычисляем размер GDT

В этом примере самый первый дескриптор инициализируется нулями. Так делается всегда. Самый первый дескриптор в таблицах GDT и LDT никогда не используется. Программа может загрузить в сегментный регистр селектор, соответствующий первому дескриптору (поле индекса в таком селекторе равно нулю), однако при попытке использовать такой селектор произойдёт прерывание работы программы. Селектор с нулевым полем индекса (пустой селектор) загружается операционной системой в неинициализированные сегментные регистры перед передачей управления запущенной программе.

Второй дескриптор описывает саму таблицу GDT, в поле предела стоит значение GDT_SIZE-1. Это предел таблицы GDT. В поле доступа стоит значение, соответствующее сегменту данных.

Следующие три дескриптора описывают сегменты, адресуемые регистрами ds, cs и ss соответственно (сегменты данных, кода и стека). В них заполнены поля предела и доступа. Эти поля могут быть определены, например, следующим образом

CODE_ACC equ 10011000b

DATA_ACC equ 10010000b

В нашем примере мы заполнили не все поля дескрипторов в таблице GDT. Остались незаполненными поля base_lo и base_hi, т.е. физический адрес сегмента данных.

Физический адрес сегмента данных должен быть вычислен в реальном режиме на основании значений сегментного адреса и смещения, т.е. на основании двух компонент логического адреса реального режима. Можно предложить следующую процедуру для вычисления физического адреса (на примере вычисления физического адреса таблицы GDT) и записи вычисленного адреса в дескриптор:

; Загружаем в ax адрес сегмента данных DGROUP

mov ax,DGROUP

; Формируем в dl:ax физический адрес, соответствующий

; сегментному адресу DGROUP

mov dl,ah

shr dl,4

shl ax,4

; Складываем со смещением

add ax,OFFSET gdtadr

adc dl,0

; Записываем физический адрес GDT в элемент GDT,

; описывающий саму GDT

mov bx,OFFSET gdt_gdt

mov [(desc_struc bx).base_l],ax

mov [(desc_struc bx).base_h],dl

Аналогично заполняются и другие элементы таблицы GDT.

Так как дескриптор с адресом gdt_gdt описывает саму таблицу GDT (и формат этого дескриптора подходит для команды LGDT), его можно использовать для загрузки регистра GDTR:

l gdt

[QWORD gdt_gdt]

gdt

[QWORD gdt_gdt]

Если вы создаёте программу на языке Си, глобальная таблица дескрипторов GDT может быть определена с помощью типа descriptor следующим образом:

descriptor gdt[5];

В этом примере создаётся таблица GDT, содержащая пять дескрипторов. Тип descriptor определяется так:

typedef struct descriptor {

word limit;

word base_lo;

unsigned char base_hi;

unsigned char access;

unsigned reserved;

} descriptor;

Инициализацию дескрипторов в таблице GDT можно выполнить, например, с помощью следующей функции:

void init_gdt_descriptor(descriptor *descr,

// указатель на инициализируемый дескриптор

unsigned long base, // базовый адрес сегмента

word limit, // предел сегмента

unsigned char acc_byte) // поле доступа

{

descr->base_lo = (word)base;

descr->base_hi = (unsigned char)(base >> 16);

descr->access = acc_byte;

descr->limit = limit;

descr->reserved = 0;

}

Приведём пример использования этой функции для записи в третий по счёту элемент GDT информации о сегменте данных с сегментным адресом _DS и пределом 0xffff:

init_gdt_descriptor(&gdt[2], MK_LIN_ADDR(_DS, 0),

0xffffL, TYPE_DATA_DESCR | SEG_PRESENT_BIT | SEG_WRITABLE);

Преобразовать логический адрес реального режима (сегмент:смещение) в физический адрес можно с помощью следующей макрокоманды:

#define MK_LIN_ADDR(seg,off)

(((unsigned long)(seg))<<4)+(word)(off)

Для формирования поля доступа в нашем примере используются такие определения:

#define TYPE_CODE_DESCR 0x18

#define TYPE_DATA_DESCR 0x10

#define SEG_WRITABLE 0x02

#define SEG_READABLE 0x02

#define SEG_PRESENT_BIT 0x80

К

сожалению, встроенный в Borland C 3.0

Inline-ассемблер не позволяет использовать

команду LGDT в программе, составленной

на языке Си. Аналогичное ограничение

имеется и в Microsoft Visual C++. Поэтому для

загрузки этого и некоторых других

регистров приходится использовать

отдельные модули, составленные полностью

на языке ассемблера.

К

сожалению, встроенный в Borland C 3.0

Inline-ассемблер не позволяет использовать

команду LGDT в программе, составленной

на языке Си. Аналогичное ограничение

имеется и в Microsoft Visual C++. Поэтому для

загрузки этого и некоторых других

регистров приходится использовать

отдельные модули, составленные полностью

на языке ассемблера.

В отличие от регистра GDTR, регистр LDTR имеет только 16 разрядов. Он содержит не адрес и размер таблицы LDT, а селектор дескриптора, описывающего таблицу LDT. Это системный дескриптор, который должен находиться в таблице GDT и иметь в поле TYPE значение 2.

Дескриптор сегмента LDT содержит базовый адрес и предел таблицы LDT.

Мы уже говорили, что простейшие системы защищённого режима могут не использовать таблицу LDT вовсе. Все приведённые в этой книге примеры программ пользуются только GDT. Практическая польза от применения таблиц LDT появляется только в мультизадачных системах. В этом случае назначение каждой задаче собственной LDT позволяет полностью изолировать адресные пространства отдельных задач.

Особенности организации памяти

О сновная

мысль сводится к формированию таблиц

описания памяти, которые определяют

состояние её отдельных сегментов/страниц

и т. п. При нехватке памяти операционная

система может выгрузить часть данных

из оперативной памяти на диск, а в таблицу

описаний внести указание на отсутствие

этих данных в памяти. При попытке

обращения к отсутствующим данным

процессор сформирует исключение

(разновидность прерывания) и отдаст

управление операционной системе, которая

вернёт данные в память, а затем вернёт

управление программе. Таким образом

для программ процесс подкачки данных

с дисков происходит незаметно.

сновная

мысль сводится к формированию таблиц

описания памяти, которые определяют

состояние её отдельных сегментов/страниц

и т. п. При нехватке памяти операционная

система может выгрузить часть данных

из оперативной памяти на диск, а в таблицу

описаний внести указание на отсутствие

этих данных в памяти. При попытке

обращения к отсутствующим данным

процессор сформирует исключение

(разновидность прерывания) и отдаст

управление операционной системе, которая

вернёт данные в память, а затем вернёт

управление программе. Таким образом

для программ процесс подкачки данных

с дисков происходит незаметно.

Объём виртуального адресного пространства

Виртуальное адресное пространство — это максимально доступное приложению адресное пространство. Объём виртуального адресного пространства зависит от архитектуры компьютера и операционной системы. Он зависит от архитектуры компьютера, так как именно архитектура определяет, сколько бит используется для адресации. Он также зависит от операционной системы, так как в зависимости от реализации операционная система может накладывать дополнительные ограничения, помимо ограничений архитектуры.

Прилагательное «виртуальное» применительно к виртуальному адресному пространству означает, что это общее число доступных приложению уникально адресуемых ячеек памяти, но не общий объём памяти, установленной в компьютере, или выделенной в конкретный момент времени данному приложению.

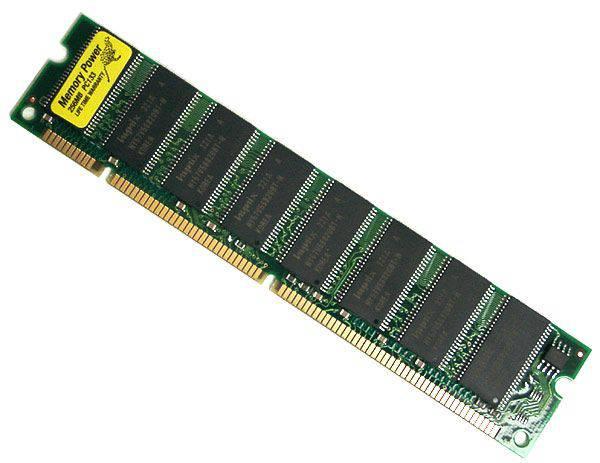

Для реализации виртуальной памяти в компьютере должен быть специальный аппаратный механизм управления памятью. Часто этот механизм называют устройством управления памятью (Memory Management Unit, MMU). Если MMU отсутствует, при обращении процессора к памяти реальный адрес в памяти никогда не меняется — адрес 123 всегда соответствует одной физической ячейке ОЗУ.

М одуль

дополнительного ОЗУ

одуль

дополнительного ОЗУ

Однако с MMU адреса проходят этап преобразования, прежде чем произойдёт обращение к памяти. Это значит, что адресу памяти 123 в одном случае может соответствовать физический адрес 82043, а в другом случае — физический адрес 20468. Но если сопоставлять виртуальные адреса физическим для каждого из миллиардов байт памяти, издержки будут слишком велики. Вместо этого, MMU делит ОЗУ на страницы — непрерывные блоки памяти заданного размера, которые рассматриваются MMU как одно целое.

Может показаться, что введение страниц и преобразования адресов — необязательный и непонятный дополнительный шаг. Однако он очень важен для реализации виртуальной памяти.

Организация защиты памяти

З ащита

памяти (англ. Memory protection) — это способ

управления правами доступа к отдельным

регионам памяти. Используется большинством

многозадачных операционных систем.

Основной целью защиты памяти является

запрет доступа процессу к той памяти,

которая не выделена для этого процесса.

Такие запреты повышают надежность

работы как программ так и операционных

систем, так как ошибка в одной программе

не может повлиять непосредственно на

память других приложений.

ащита

памяти (англ. Memory protection) — это способ

управления правами доступа к отдельным

регионам памяти. Используется большинством

многозадачных операционных систем.

Основной целью защиты памяти является

запрет доступа процессу к той памяти,

которая не выделена для этого процесса.

Такие запреты повышают надежность

работы как программ так и операционных

систем, так как ошибка в одной программе

не может повлиять непосредственно на

память других приложений.

Методы

Чаще всего реализуется в рамках виртуальной адресации памяти.

Сегментирование памяти

Сегментирование памяти означает разбиение компьютерной памяти на фрагменты переменной длины, называемые сегментами.

В архитектуре x86 есть несколько режимов сегментации, которые могут использоваться для защиты памяти. В процессорах архитектуры x86, существуют Global Descriptor Table и Local Descriptor Table, описывающие сегменты памяти. Указатели на сегменты в подобных процессорах хранятся в специализированных сегментных регистрах. Изначально их было 4: CS (code segment), SS (stack segment), DS (data segment) и ES (extra segment); затем добавили еще два: FS и GS.

Страничная память

При страничной организации памяти, все адресное пространство делится на фрагменты фиксированного размера, называемые страницами. Их размер кратен степени 2, и обычно равен 4096, но возможно использование одновременно нескольких размеров страниц (4 кб, 2-4МБ в x86, от 4 до 256 кб в IA64). При помощи механизма виртуальной памяти, каждая страница виртуальной памяти может быть поставлена в соответствие любой странице физической памяти, либо помечена как защищенная. При помощи виртуальной памяти возможно использование линейного адресного пространства виртуальной памяти, которое на самом деле образовано фрагментированными участками адресного пространства физической памяти.

Многие архитектуры, использующие страничную организацию памяти, в том числе и наиболее популярная x86, реализуют защиту памяти на уровне страниц.

Таблица страниц используется для установления соответствия адресов в виртуальной памяти физическим адресам. Обычно эта таблица невидима для программы. Возможность установки в таблицах произвольных отображений позволяет легко выделить новую память, т.к. дополнительная страница, расположенная в нужном месте виртуального адресного пространства, может быть отображена на любую свободную страницу в оперативной памяти.

При таком отображении, приложение не имеет возможности обратиться к странице, отсутствующей в ее таблице страниц. Если при обращении по произвольному адресу не было найдено подходящее отображение, происходит исключительная ситуация page fault (PF).

Следует заметить, что page fault - это не фатальное событие. Эти прерывания могут использоваться не только для защиты памяти, но и другими способами. Так, ОС, перехватив PF, может загрузить страницу в память, например, если она была ранее выгружена на жесткий диск в процессе подкачки страниц, после чего приложение может продолжать работу. Такая схема позволяет прозрачным способом увеличить количество доступной приложениям памяти.

М еханизм

ключей защиты

еханизм

ключей защиты

Применялся в System/360, Itanium и PA-RISC.

Симуляция сегментации

А

IBM 360 (System 360)

дресация основанная на CapabilityCapability-based addressing редко применяется в коммерческих компьютерах. В системах с такой защитой памяти вместо указателей используются защищенные объекты (называемые capabilities), которые могут быть созданы лишь привилегированными инструкциями, исполняемыми либо ядром ОС либо специальными процессами. Использование такой защиты позволяет ограничивать доступ процессов к чужой памяти без использования раздельных адресных пространств и переключений контекста (сброса TLB, изменения глобальных дескрипторов). Использовались в исследовательских проектах KeyKOS, EROS; виртуальных машинах Smalltalk и Java.

Оценка уровня защиты

Защита памяти в различных ОС

С реди

ОС, реализующих защиту памяти

реди

ОС, реализующих защиту памяти

Microsoft Windows начиная с Windows NT 3.1

Solaris

Linux

BSD

BSD

Mac OS X

GNU Hurd

Некоторые

старые ОС жесткого реального времени

не используют защиту памяти, даже на

процессорах, где это возможно. Примером

такой ОС является VxWorks версий до 5

включительно.

Некоторые

старые ОС жесткого реального времени

не используют защиту памяти, даже на

процессорах, где это возможно. Примером

такой ОС является VxWorks версий до 5

включительно.

Контрольные вопросы:

Объясните назначение базовых понятий защищённого режима работы процессора;

Раскройте механизм определения линейного и физического адреса при сегментной, страничной, сегментно-страничной организации в защищённом режиме работы;

Раскройте понятие – объём виртуального адресного пространства;

Раскройте особенности организации сегментной, страничной и сегментно-страничной организации памяти в защищенном режиме;

Объясните принцип защиты памяти.