Министерство образования и науки Украины

Севастопольский национальный технический университет

Кафедра ИС

ПОЯСНИТЕЛЬНАЯ ЗАПИСКА

к курсовому проекту

по дисциплине: «Операционные системы и системное программирование»

на тему «Построение отладчика команд языка ассемблера микропроцессора КР1816ВЕ48»

Выполнила:

ст.гр. И-43д

Бондарева Ю.С.

Проверил:

Забаштанский А.К.

Севастополь

2010

Оглавление

ВВЕДЕНИЕ 3 1 ПОСТАНОВКА ЗАДАЧИ 4 2 АРХИТЕКТУРА И ФУНКЦИОНИРОВАНИЕ К1816ВЕ48 5 2.1 Архитектура микропроцессора 5 2.2 Система команд микроконтроллера 21 2.3 Команды, подлежащие реализации.. 25 3 РАЗРАБОТКА ОТЛАДЧИКА 27 3.1 Разработка дизассемблера машинных кодов 27 3.2 Описание структуры отладчика 28 3.3 Описание интерфейса программы 29 4 ВЫПОЛНЕНИЕ ИНФОРМАЦИОННЫХ РАСЧЕТОВ 32 4.2 Расчёт надёжности программы-отладчика 32 ЗАКЛЮЧЕНИЕ 33 БИБЛИОГРАФИЧЕСКИЙ СПИСОК 34 ПРИЛОЖЕНИЕ А 35

|

||||||||||||

|

|

|

|

|

КУРСОВОЙ ПРОЕКТ |

|||||||

|

|

|

|

|

||||||||

Из |

Лист |

N докум. |

Подп |

Дат |

||||||||

Разраб. |

Бондарева |

|

|

ПОЯСНИТЕЛЬНАЯ ЗАПИСКА |

Лит |

Лист |

Листов |

|||||

|

|

|

|

|||||||||

Проверил |

Забаштанс-кий |

|

|

|

|

|

2 |

67 |

||||

Н. Контр |

|

|

|

|

||||||||

Утв. |

|

|

|

|||||||||

ВВЕДЕНИЕ

Одной из актуальных задач, решаемых в рамках системного программирования, является разработка компонентов программного обеспечения, наделённых функциями синтаксического и семантического анализа. К таким программным продуктам, в частности, относятся ассемблеры, интерпретаторы и отладчики для различных микропроцессоров.

Известный прогресс в области создания специализированных микропроцессоров объективно сопряжён с трудностями построения средств интерактивного программирования и отладки прикладного и специализированного программного обеспечения, разрабатываемых для указанных микропроцессоров.

Отмеченные проблемы традиционно разрешают путём построения аппаратных или программных комплексов, которые выполняют полное или частичное моделирование функций микропроцессора.

Отладчик содержит в своём составе процедуры моделирования операций, выполняемых в ходе функционирования и интерфейс.

Интерфейсная часть отладчика, помимо пассивного отображения, предоставляет возможности оперативного вмешательства в последовательность выполнения и коррекцию данных, используемых ею.

Отладчик позволяет анализировать работу программы во время ее исполнения. С его помощью можно автоматически или пошагово выполнять отдельные операторы исходного кода, наблюдая при этом, как меняются значения различных регистров.

В первом разделе указана постановка задачи к курсовому проекту.

Во втором разделе описывается архитектура микропроцессора и система команд с подробным рассмотрением реализуемых команд.

В четвёртом разделе описывается разработка отладчика.

Информационные расчёты выполнены в пятом разделе данной пояснительной записки.

1 Постановка задачи

В соответствии с вариантом № 3 необходимо написать транслятор и отладчик команд языка ассемблера микропроцессора К1816ВЕ48, интерпретирующие директиву DD и следующие команды:

- ANL;

- JNC;

- OUTL;

- ORDL;

- RETR;

- RL A;

- NOP;

- HLT.

2 Архитектура и функционирование к1816ве48

2.1 Архитектура микропроцессора

Микроконтроллер К1816ВЕ48 (аналог MCS-48) представляет собой 8-битную однокристальную микро-ЭВМ из серии К1816 (аналог Intel 8048). Для данной серии характерно применение гарвардской архитектуры.

К особенностям именно этой ОМЭВМ относят внутреннее перепрограммируемое ПЗУ размером 1 Кбайт с ультрафиолетовым стиранием, ОЗУ размером 64 байта, работу с тактовой частотой 6МГц. В остальном она является взаимозаменяемой и совместимой по выводам и системе команд с другими ОМЭВМ данной серии.

Структурная схема ОМЭВМ К1816ВЕ48 (далее для сокращения ВЕ48) показана на рисунке 2.1.1. Основу структуры ВЕ48 образует внутренняя двунаправленная 8-битная шина, которая связывает между собой все устройства БИС: арифметико-логическое устройство (АЛУ), устройство управления, память и порты ввода/вывода информации. Рассмотрим последовательно основные элементы структуры и особенности организации ОМЭВМ.

Арифметико-логическое устройство. В состав АЛУ входят: регистры временного хранения TMP1 и TMP2, аккумулятор (ACC), ПЗУ констант, арифметико-логическое устройство, регистр состояния программ (PSW).

Аккумулятор используется в качестве регистра операнда и регистра результата. Регистр временного хранения операнда Т1 программно недоступен и используется для временного хранения второго операнда при выполнении двухоперандных команд. АЛУ может выполнять следующие операции:

сложение байтов с переносом и без; логические операции И, ИЛИ, исключающее ИЛИ; инкремент, декремент, инверсию;

циклический сдвиг влево, вправо через (или минуя) флаг переноса, обмен тетрад в байте;

десятичную коррекцию содержимого аккумулятора.

При выполнении операций в АЛУ устанавливаются флаги, некоторые из которых не фиксируются на триггерах. К таким флагам относятся флаг нулевого содержимого аккумулятора Z и флаг наличия единицы в селектируемом бите аккумулятора Bn. Флаги переноса и вспомогательного переноса (перенос из младшей тетрады в старшую) фиксируются на триггерах,входящих в состав регистра слова состояния программы (ССП).

Кроме того, логика условных переходов ОМЭВМ оперирует флагами F0 и F1, функциональное назначение которых определяется разработчиком; флагом переполнения таймера TF, сигналами на входах Т0 и Т1. В ходе работы используются также флаги рабочего банка регистров BS и выбранного банка внешней памяти программ MB. Логикой переходов после окончания каждого машинного цикла опрашивается флаг разрешения/запрета прерываний.

2.1.1 Построение памяти микроконтроллеров семейства MCS-48

Микроконтроллеры семейства MCS-48 построены по гарвардской архитектуре. Это означает, что память данных и память программ в этих микросхемах разделены и имеют отдельное адресное пространство. В этих микроконтроллерах имеется три адресных пространства: память программ, внешняя память данных и внутренняя память данных. Такое построение памяти позволяет реализовывать максимально надёжные системы.

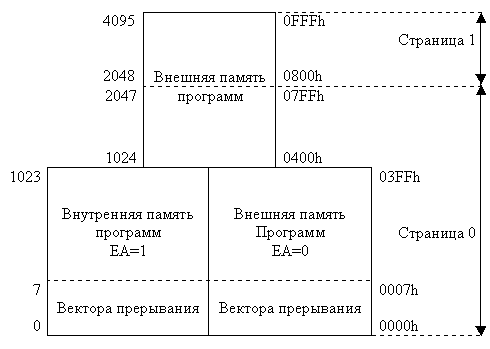

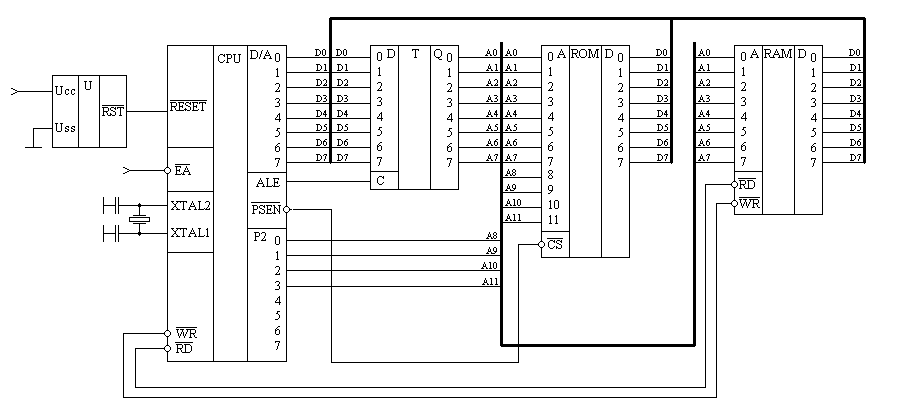

Для обращения к памяти данных и к памяти программ используются одни и те же шина адреса и шина данных, но разные управляющие сигналы. Для чтения памяти программ вырабатывается сигнал PSEN, а для чтения памяти данных вырабатывается сигнал RD. Для записи информации в память данных вырабатывается сигнал WR. То есть память программ доступна только для чтения, а память данных доступна и для чтения и для записи любой информации, записанной в двоичном коде (рисунок 2.1.2).

Память программ предназначена для хранения программ и имеет отдельное от памяти данных адресное пространство объемом 4 Кбайта, причем для некоторых микросхем (например КР1816ВЕ48, КМ1816ВЕ49) для хранения программ на кристалле микроконтроллера расположено ПЗУ. Это ПЗУ отображается в область младших адресов памяти программ. Учитывая, что выполнение программы после сброса микроконтроллера всегда начинается с нулевого адреса памяти программ, то при включении питания начнет выполняться программа, записанная во внутреннем ПЗУ микроконтроллера. Микроконтроллеры, не имеющие внутреннего ПЗУ (например КР1816ВЕ35 или 8035) могут работать только с внешней микросхемой ПЗУ емкостью до 4 Кбайт. Микроконтроллеры семейства MCS-48 имеют внешний вывод EA, с помощью которого можно запретить работу внутренней памяти, для чего необходимо подать на вывод EA логический "0" (соединить этот вывод с корпусом). При этом внутренняя память программ отключается и, начиная с нулевого адреса, все обращения происходят к внешней памяти программ.

Доступ к внешней памяти программ осуществляется в двух случаях:

при действии сигнала EA=0 независимо от адреса обращения,

в любом случае, если программный счетчик (РС) содержит число большее, чем максимальная ячейка внутренней памяти программ.

Распределение памяти программ микроконтроллера КР1816ВЕ48 представлено ниже.Для чтения таблиц элементарных функций, перекодировок или строк, выводимых на дисплей, из памяти программ используются команды:

MOVP A, @A и MOVP3 A, @A.

Переключение страниц памяти программ осуществляется командами:

SEL MB1 ;Выбрать первую страницу

SEL MB0 ;Выбрать нулевую страницу

Рисунок 2.1.2 - Адресное пространство памяти программ

Для других микроконтроллеров этого семейства изменяется только объем внутренней памяти программ. При использовании портов P1 и P2 в качестве дополнительных адресных расширителей объём доступной внешней памяти программ может быть увеличен до 16 Мбайт.

Ниже в таблице 2.2 приведены адреса векторов прерываний и соответствующие им аппаратурные источники прерываний программы:

Таблица 2.1 – Таблица, содержащая адреса векторов прерываний

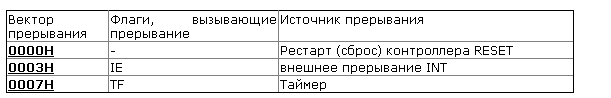

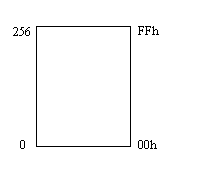

Внешняя память данных предназначена для временного хранения информации, используемой в процессе выполнения программы. Эта память физически должна быть подключена к микросхеме микроконтроллера. Максимальный объем этой памяти определяется регистрами R0 и R1 и составляет 256 байт. Точно так же, как и в случае внешней памяти программ, объем внешней памяти данных может быть увеличен за счет использования портов P1 и P2 до 16 Мбайт. Для обращения к внешней памяти данных используются команды:

MOVX A, @R0 или MOVX A, @R1 (команды чтения)

MOVX @R0, или MOVX @R1, A (команды записи)

Рисунок 2.3 - Адресное пространство внешней памяти данных.

Отметим, что в качестве внешней памяти данных могут быть использованы как микросхемы ОЗУ так и микросхемы ПЗУ.

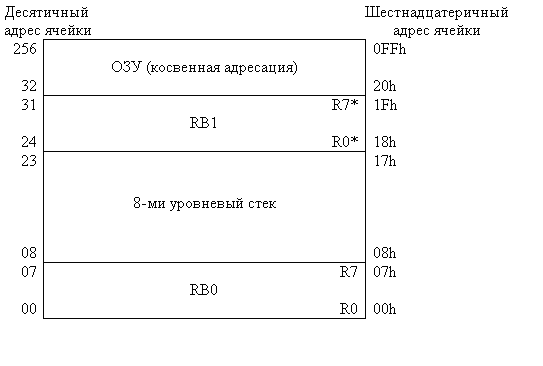

Внутренняя память данных (RAM) предназначена для временного хранения информации, используемой в процессе выполнения программы. Адресное пространство внутренней памяти данных представляет собой 256 восьмиразрядных ячеек, с адресами от 000h до 0FFh. Для микроконтроллеров 8048, 8035, КР1816ВЕ35, КР1816ВЕ48 из них доступно только 64 ячейки памяти. Для микроконтроллеров 8049, КР1816ВЕ49 из них доступно 128 ячеек памяти. И только для микроконтроллеров 1850ВЕ49 доступны все 256 ячеек внутренней памяти данных. Распределение адресного пространства памяти данных микроконтроллеров серии MCS-48 приведено на рисунке 2.3.

Младшие 32 байта внутреннего ОЗУ данных объединены с 2-мя банками регистров (RB0 - RB1) и восьмиуровневым стеком микроконтроллера. Банк регистров состоит из восьми восьмиразрядных регистров с именами R0, R1, …, R7. Два банка регистров служат для организации независимой работы основной программы и подпрограмм обслуживания прерываний. Переключение банков регистров производится при помощи особого бита BS регистра слова состояния программы PSW командами SEL RB0 и SEL RB1.

Команды программы могут обращаться к регистрам, используя их имена R0-R7 (MOV A, R0 или MOV R7, A), или используя их адрес во внутренней памяти данных (доступна только косвенно-регистровая адресация).

Рисунок 2.3 - Адресное пространство внутренней памяти данных

Следующие после второго банка регистров ячейки памяти образуют обычное ОЗУ.

Ячейки внутренней памяти данных с адресами 8 - 23 представляют из себя аппаратный 8 - ми уровневый стек, где сохраняются адреса возвратов из подпрограмм. В составе системы команд отсутствуют команды сохранения регистров в стеке. То есть разработчик программы вынужден следить за использованием регистров во вложенных подпрограммах. Это, наряду с малой глубиной аппаратного стека, сильно ограничивает возможности по написанию программ для микроконтроллеров семейства MCS-48.

2.1.2 Организация ввода/вывода информации

Для связи ВЕ48 с объектом управления, для ввода и вывода информации используются 27 линий. Эти линии сгруппированы в три порта по восемь линий и три отдельных линии, влияющие на ход работы программы:

линия ЗПР (ввод в ОМЭВМ сигнала запроса прерывания от внешнего источника);

линия Т0 (используется для ввода тестирующего сигнала от двоичного датчика объекта управления);

линия Т1 (используется для ввода тестирующего сигнала или в качестве входа счетчика событий).

Порты ввода-вывода Р1 и Р2 являются квазидвунаправленными, т.е. каждая линия портов может быть программным путем настроена на ввод, вывод или на работу с двунаправленной линией передачи. Для настройки линии на режим ввода в МК, необходимо в буферный триггер этой линии записать 1. Сигнал СБР автоматически записывает во все линии портов Р1 и Р2 единицы. В процессе ввода информации выполняется операция логического И над вводимыми данными и текущими (последними) выведенными данными. В ОМЭВМ отсутствует возможность выполнить операцию чтения значений портов Р1 и Р2 для определения прежнего состояния порта вывода.

Порт Р2 отличается от порта Р1 тем, что через его младшую тетраду по специальным командам обращения возможен доступ к четырем внешним четырехбитным портам ввода/вывода Р4-Р7. Работа этих внешних портов синхронизируется сигналом ПРОГ/СТВВ.

Порты P1, P2 являются квазидвунаправленными портами ввода - вывода и предназначены для обеспечения обмена информацией микроконтроллера с внешними устройствами, образуя 16 линий ввода- вывода. Каждый из портов содержит восьмиразрядный регистр, позволяющий устанавливать (запись '1') или сбрасывать (запись '0') любой разряд этого регистра с помощью программного обеспечения.

Один разряд регистра - защелки порта представляет собой D-триггер. Данные с внутренней шины микроконтроллера записываются в регистр-защелку по сигналу "запись в защелку". Значение сигнала с внешнего вывода порта считывается по сигналу "чтение вывода". При чтении ножки микросхемы осуществляется операция логического "И" между сигналом на ножке микросхемы и содержимым триггера квазидвунаправленного порта. Поэтому перед чтением ножки микросхемы необходимо записать в соответствующий разряд порта логическую единицу. Чтение внешних ножек микросхемы осуществляется командами:

IN A, P1 ;Скопировать состояние ножек порта P1 в аккумулятор

IN A, P2 ;Скопировать состояние ножек порта P2 в аккумулятор

Вывод информации через параллельные порты осуществляется командами:

OUTL P1, A ;Скопировать содержимое аккумулятора в порт P1

OUTL P2, A ;Скопировать содержимое аккумулятора в порт P2

При выводе информации обычно требуется работать с каждым битом порта отдельно. Так как при считывании значения порта на самом деле будет считываться напряжение на внешней ножке микросхемы, то для модификации кода, записываемого в порт нужно хранить его копию во внутренней памяти микроконтроллера. Модификация обычно производится при помощи операции маскирования с использованием команд ORL и ANL.

Для записи числа в порт (изменения потенциалов на ножках микросхемы) можно воспользоваться следующими способами:

OUTL (выдача в порт константы), например

MOV A, #56h ;Установить единичный сигнал на ножках 1,2,4 и 6 порта P2

OUTL P2, A ;и нулевой потенциал на ножках 0,3,5 и 7

MOV A, #01110011b ;Выдать на все восемь выводов порта P1

OUTL P1, A ;двоичное число 01110011

ANL (использование логического 'И' для обнуления выбранных маской бит), например:

MOV A, 56 ;Занести в аккумулятор копию порта P1

ANL P1, #11110011b ;сформировать низкий потенциал на ножках P1.2 и P1.3

OUTL P1, A ;записать новое значение в порт P1

XRL (использование операции исключающее 'ИЛИ' для инвертирования выбранных бит), например

MOV A, 56 ;Занести в аккумулятор копию порта P1

XRL A, #01000010b ;инвертировать состояние ножек P1.1 и P1.6

OUTL P1, A ;записать новое значение в порт P1

ORL (использование операции логическое 'ИЛИ' для записи единиц в выбранные биты), например

MOV A, 56 ;Занести в аккумулятор копию порта P1

ORL A, #00100001b ;выдать высокий потенциал на ножках P1.0 и P1.5

OUTL P1, A ;записать новое значение в порт P1

Порт P1. Этот квазидвунаправленный порт никаких особенностей не имеет. При сбросе микросхемы во все разряды порта P2 записываются '1'.

Рисунок 2.4 - Подключение внешней памяти программ и памяти данных

Порт P2. Младшая тетрада порта может быть использована для передачи старших четырёх бит адреса при работе с внешней памятью программ и внешней памятью данных (с 12- разрядным адресом). Схема использования порта P2 в качестве шины адреса приведена на рисунке 2.4. При сбросе микросхемы во все разряды порта P2 записываются '1'. Кроме того через младшие четыре разряда порта 2 могут быть использованы для подключения микросхемы расширителя портов.

Порт D/A. Может быть использован для стробируемого вывода данных. Стробирование данных производится сигналом WR. Над этим портом возможно выполнение логических операций, что может сократить длину программ, приведённых выше, до одной команды.

Порт ввода/вывода BUS представляет собой двунаправленный буфер с тремя состояниями и предназначен для побайтного ввода, вывода или ввода/вывода информации. При выводе байта генерируется стробирующий сигнал 3П, а выводимый байт фиксируется в буферном регистре. При вводе байта генерируется стробирующий сигнал ЧТ, но вводимый байт в буферном регистре не фиксируется. В отсутствие передач порт BUS по своим выходам находится в высокоимпедансном состоянии.

В устройствах, имеющих внешнюю память программ, порт BUS используется для выдачи адреса внешней памяти и для приема команды из внешней памяти программ.

Устройство управления микроконтроллера совместно с логической схемой переходов в каждом цикле команды формирует последовательность сигналов, управляющих функциями всех блоков ОМЭВМ и системой их взаимосвязи.

Синхронизация ВЕ48. Опорную частоту синхронизации в диапазоне от 1 до 6 МГц определяет или кварцевый резонатор, подключаемый к выводам X1 и Х2, или LC-цепь. На вход X1 может подаваться сигнал от источника внешней синхронизации. В состав генератора ОМЭВМ входят два счетчика с модулями пересчета 3 и 5: для формирования сигнала системной синхронизации СС с периодом 0,5 мкс и сигнала САВП (2,5 мкс), идентифицирующего машинный цикл и используемого в расширенных микропроцессорных системах для стробирования адреса внешней памяти.

Системный сброс. Для инициализации ВЕ48 к входу СБР обеспечивается подача сигнала, близкого к потенциалу корпуса, длительностью не менее 50 мс после того, как напряжение установится до номинального значения. Сигнал СБР производит следующие действия: сбрасывает счетчик команд и указатель стека; устанавливает порт BUS в высокоимпедансное состояние, а порты Р1 и Р2 – на режим ввода; выбирает банк регистров 0 и банк памяти 0; запрещает прерывания; останавливает таймер и выдачу синхросигнала на вывод Т0; сбрасывает флаг переполнения таймера TF и флаги пользователя F0 и F1.

Логика условных переходов. Логическая схема условных переходов позволяет осуществлять переходы по нулевому значению аккумулятора, по флагу переноса C, флагам пользователя F0 и F1, флагу переполнения таймера TF и по значению тестовых входов Т0 и Т1.

Режим прерывания. Линия запроса прерывания от внешнего источника ЗПР проверяется каждый машинный цикл во время действия сигнала САВП, но передача управления ячейке 3 выполняется только по завершению цикла команды. При обработке прерывания состояние МК сохраняется в стеке. Режим прерывания может быть запрещен или разрешен программно. Прерывание по входу ЗПР имеет приоритет выше прерывания по таймеру.

2.1.3 Устройство таймера микроконтроллера MCS-48

В микроконтроллерах семейства MCS-48 внутренний таймер может быть использован как в режиме таймера так и в режиме счетчика внешних событий.

Режим таймера.

Таймер состоит из пятиразрядного предварительного делителя на 32 и восьмиразрядного суммирующего счётчика. На вход предделителя поступают сигналы основной синхронизации ALE с периодом 2,5 мкс (15 периодов задающего генератора тактовой частоты). Таким образом минимальный промежуток времени, задаваемый при помощи таймера равен 80 мкс. Путём предварительной записи информации в таймер можно регулировать время, задаваемое таймером от 80 мкс до 20,48 мс. Эти значения определяются тем, что в таймер T можно записать 256 различных чисел. Если требуется больший временной интервал, то его можно получить программным путём с использованием любой ячейки внутренней памяти. Схема таймера приведена на рисунке 2.5.

Рисунок 2.5 - Схема таймера микроконтроллеров семейства MCS-48

Когда содержимое счетчика изменяется из состояния все "1" в состояние все "0" , то устанавливается (принимает значение "1") флаг прерывания таймера TF0 или TF1.

Обычно пользователя интересует не максимальный интервал времени, а свой конкретный интервал времени, меньший максимально возможного. Для уменьшения интервала времени в регистр таймера можно предварительно занести число и тем самым сформировать произвольный интервал времени

В режиме счетчика содержимое счетчика инкрементируется под воздействием перехода из 1 в 0 внешнего входного сигнала, подаваемого на вывод микроконтроллера T1. Так как на распознавание периода требуются три машинных цикла то, минимальное время между импульсами равно 7,5 мкс. Минимальная длительность единичного сигнала на входе T1 при частоте кварцевого резонатора 6 МГц равна 0,5 мкс. На длительность периода входных сигналов ограничений сверху нет.

Запуск счётчика осуществляется командой STRT CNT, а остановка STOP TCNT. Количество подсчитанных импульсов можно считать командой MOV A, T.

Таймер/счетчик. Внутренний 8-битный двоичный суммирующий счетчик может быть использован для формирования временных задержек и для подсчета внешних событий. Содержимое таймера/счетчика (Т/С) можно прочитать или изменить программно. Из максимального состояния FFH таймер/счетчик переходит в начальное состояние 00Н, при этом устанавливается в 1 флаг переполнения. Прерывание от таймера/счетчика может быть запрещено, а флаг переполнения – опрошен программно. Выполнение перехода по флагу TF сбрасывает этот флаг.

2.1.4 Краткое описание выводов микросхемы

ОМЭВМ ВЕ48 конструктивно выполнена в корпусе БИС с 40 внешними выводами. Все выводы электрически совместимы с элементами ТТЛ: входы представляют собой единичную нагрузку, а выходы могут быть нагружены одной ТТЛ-нагрузкой. Ниже приводятся символические имена выводов корпуса и даются краткие пояснения их назначения:

Общ (VSS) – потенциал корпуса (сигнальное заземление);

+5 В Осн (VCC) – основное напряжение питания +5 В; подается во время работы и при программировании РПП;

+5 В Доп (VDD) – дополнительное напряжение питания +5 В; во время работы обеспечивает электропитание только для РПД; на этот вывод при программировании РПП подается уровень +25 В;

ПРОГ (PROG) – вход для подачи программирующего импульса +25 В при загрузке РПП; выход стробирующего сигнала для БИС расширителя ввода/ вывода;

Х1- вход для подключения вывода кварцевого резонатора или вход для сигнала от внешнего источника синхронизации;

Х2- вход для подключения второго вывода резонатора;

СБР (RST) – вход сигнала общего сброса при запуске ОМЭВМ; сигнал 0 при программировании и проверке РПП;

ШАГ (SS) – сигнал, который совместно с сигналом САВП позволяет при отладке выполнять программу по шагам с остановом после исполнения очередной команды;

РВПП (PSEN)- разрешение внешней памяти программ; сигнал выдается только при обращении к внешней памяти программ;

САВП (ALE) – строб адреса внешней памяти; сигнал используется для приема и фиксации адреса внешней памяти на внешнем регистре; сигнал является идентификатором машинного цикла, так как всегда выводится из ОМЭВМ с частотой, в 5 раз меньшей основной частоты синхронизации;

ЧТ (RD) – стробирующий сигнал при чтении из внешней памяти данных или УВВ;

ЗП (WR) – стробирующий сигнал при записи во внешнюю память данных или УВВ;

Т0- входной сигнал, опрашиваемый по командам условного перехода JT0 и JNT0; кроме того, используется при программировании РПП; может быть использован для вывода сигнала синхронизации после команды ENT0 CLK;

Т1- входной сигнал, опрашиваемый командами условного перехода JT1 и JNT1; кроме того, используется в качестве входа внутреннего счетчика внешних событий после исполнения команды STRT CNT;

ЗПР (INT)— сигнал запроса прерывания от внешнего источника; вызывает подпрограмму обслуживания прерывания, если прерывание разрешено ранее по команде ENI; сигнал СБР запрещает прерывания;

ОРПП (ЕА)— отключение РПП; уровень 1 на этом входе заставляет ВЕ48 выполнять выборку команд только из внешней памяти программ; используется при тестировании прикладной программы и отладке ОМЭВМ; 25 В при программировании РПП;

Порт 1 (PI)— 8-битный квазидвунаправленный порт ввода/вывода информации; каждый разряд порта может быть запрограммирован на независимый ввод или вывод;

Порт 2 (Р2)— 8-битный квазидвунаправленный порт ввода/ вывода информации; каждый разряд порта может быть запрограммирован на ввод или вывод; биты Р2о-з во время чтения из ВПП содержат старшие четыре бита счетчика команд CК8-11; используются для подключения БИС расширителя ввода/вывода (порты Р4—Р7);

Порт BUS (DB) 8-битный двунаправленный порт ввода/вывода информации; может быть отключен от нагрузки; может выполнять прием и выдачу байтов синхронно с сигналами ЧТ и ЗП; при обращении к ВПП содержит 8 младших бит счетчика команд и затем по сигналу РВПП принимает выбранную команду; при обращении к ВПД содержит младшие 8 бит адреса синхронно с сигналом САВП и байт данных синхронно с сигналами ЧТ или ЗП.

2.2 Система команд микроконтроллера

В машинном коде команда занимает один или два байта, в зависимости от типа команды. Команды выполняются за один или два машинных цикла. При этом большинство команд выполняются за один машинный цикл длительностью 2,5 мкс (при 6 МГц кварцевом резонаторе). В таблице 2.2 приведены инструкции, влияющие на установку флагов.

Таблица 2.2 – Таблица, содержащая инструкции, влияющие на установку флагов

-

Мнемоника

Флаги

C

AC

F0

F1

TF

BS

DBF

ADD, ADDC

+

+

-

-

-

-

-

DA

+

+

-

-

-

-

-

CLR C

0

-

-

-

-

-

-

CPL C

+

-

-

-

-

-

-

CLR F0

-

-

0

-

-

-

-

CPL F0

-

-

+

-

-

-

-

CLR F1

-

-

-

0

-

-

-

CPL F1

-

-

-

+

-

-

-

JTF

-

-

-

-

0

-

-

RRC

+

-

-

-

-

-

-

RLC

+

-

-

-

-

-

-

MOV A, PSW

+

+

+

-

-

+

-

RETR

+

+

+

-

-

+

-

SEL MB0, SEL MB1

-

-

-

-

-

-

+

SEL RB0, SEL RB1

-

-

-

-

-

+

-

Систему команд микроконтроллера условно можно разбить на пять групп:

арифметические команды;

логические команды;

команды передачи данных;

команды ветвления программ и передачи управления;

команды управления режимами работы микроконтроллера;

В наборе команд микроконтроллера имеются следующие арифметические операции:

сложение ADD,

сложение с учетом флага переноса ADDC,

инкрементирование (увеличение на 1) INC,

декрементирование (уменьшение на 1) DEC,

десятичная коррекция DA.

Действия производятся над целыми числами без знака. Команды сложения ADD позволяют сформировать перенос в следующий разряд. Команды сложения с учётом знака переноса позволяют выполнять многобайтное сложение. Вычитание может быть реализовано переводом одного из операндов в дополнительный код с последующим выполнением операции суммирования. Более сложные операции такие как умножение или деление могут быть реализованы только программным способом.

Система команд микроконтроллера позволяет реализовать логические операции:

И ( ANL ANLD),

ИЛИ ( ORL ORLD),

ИСКЛЮЧАЮЩЕЕ ИЛИ ( XRL).

сброс и инвертирование всех восьми разрядов аккумулятора ( CPL A; CLR A);

сброс и инвертирование флагов микроконтроллера ( CLR C; CLR F0; CLR F1; CPL C; CPL F0; CPL F1);

циклический сдвиг влево и вправо с учетом переноса и без ( RR A; RRC A; RL A; RLC A);

обмен местами старшей и младшей тетрад внутри аккумулятора ( SWAP A).

Как было рассмотрено ранее, арифметические и логические команды могут быть выполнены только над содержимым регистра аккумулятора, поэтому исключительно важное значение в системе команд приобретают команды пересылки данных. С помощью этих команд можно скопировать содержимое любой ячейки памяти в регистр-аккумулятор или наоборот скопировать содержимое аккумулятора в любую ячейку памяти. Так как в микроконтроллере присутствует три независимых области памяти, то для обращения к ним введены различные команды:

обмен данными во внутреннем ОЗУ: MOV, XCH

обмен данными из внешней памяти данных: MOVX

копирование данных из памяти программ: MOVP

обмен данными параллельных портов IN, OUTL, MOVD

Содержимое аккумулятора может быть обменено с содержимым рабочих регистров выбранного банка:

XCH A, R0.

Для работы с параллельными портами используется отдельные команды пересылки данных IN и OUTL:

IN A, P0 ;Скопировать число из порта P0, в аккумулятор

OUTL P1, A ;Скопировать число из аккумулятора, в порт P1

Команды ветвления позволяют реализовывать условные операторы и операторы циклов. В микроконтроллерах семейства КР1816 доступны следующие команды:

безусловный переход: JMP

вызов и возврат из подпрограммы: CALL, RET, RETR

проверка содержимого аккумулятора: JZ, JNZ, JMPP, JB0 ... JB7

проверка флага переноса С: JC, JNC

проверка сигнала на ножке T0: JT0, JNT0

проверка сигнала на ножке T1: JT1, JNT1

проверка сигнала на ножке INT: JNI

проверка состояния флагов пользователя JF0, JF1

Команды безусловных переходов и вызовов подпрограмм позволяют осуществить переход в любую точку адресного пространства памяти программ в пределах страницы 2 Кбайт. Примеры команд:

JMP Metka ;Переход к команде, расположенной по адресу обозначенному меткой ‘Metka’

CALL Podprogramma ;Вызов подпрограммы по адресу, обозначенному меткой ‘Podprogramma’

Команды управления микроконтроллером позволяют:

запускать и останавливать таймер/счётчик ( STRT CNT STRT T, STOP TCNT),

разрешать и запрещать прерывания ( EN I, EN TCNTI, DIS I, DIS TCNTI),

выбирать рабочий банк регистров ( SEL RB0, SEL RB1),

выбирать страницы памяти программ ( SEL MB0, SEL MB1),

разрешать выдачу синхросигнала на ножке T0 ( ENT0 CLC).

Микроконтроллер данного вида имеет несколько способов адресации. Наибольшее количество видов адресации используется в командах пересылки данных. При определении способа адресации операндов в команде необходимо учитывать, что адресация для каждого операнда команды своя. В общем случае адресация определяется для каждого операнда отдельно.

При неявной адресации регистр-источник или регистр-приёмник подразумевается в самом коде операции. Например:

RR A ;сдвиг содержимого аккумулятора вправо

DA A ;десятичная коррекция аккумулятора

Регистровая адресация используется для обращения к восьми рабочим регистрам выбранного банка рабочих регистров. Номер регистра записывается в трех младших битах команды. Например:

MOV A, R7 ;Во втором операнде использована регистровая адресация (в первом операнде неявная адресация)

Косвенно-регистровая адресация используется для обращения к ячейкам внутреннего ОЗУ данных. В качестве регистров-указателей используются регистры R0, R1 выбранного банка регистров. Примеры использования косвенно-регистровой адресации:

MOV A,@R1

Косвенно - регистровая адресация используется также для обращения к внешней памяти данных. В этом случае с помощью регистров- указателей R0 и R1 (рабочего банка рабочих регистров) выбирается ячейка из блока 256 байт внешней памяти данных. Номер блока предварительно задается содержимым порта Р2.

Непосредственная адресация позволяет выбрать из адресного пространства памяти программ константы, явно указанные в команде, например:

MOV A, #11h ;помещает в аккумулятор число 11h

MOV R5, #48 ;помещает в регистр R5 число 48

В системе команд имеются команды условных переходов. Эти команды позволяют осуществлять переход в пределах страницы 256 байт.

2.3 Команды, подлежащие реализации

Согласно варианту задания эмулированию подлежат не все команды ВЕ48, а лишь представленные в таблице 2.3.1. В перечне приведены: название команды, её аргументы, описание действий, производимых при выполнении, машинный код и количество байт, занимаемых ею.

Таблица 2.3.1 – Таблица, содержащая описание команд, подлежащих реализации

мнемоника |

Код команды |

Пояснение |

|

||

RL A |

11100111 |

Циклический сдвиг содержимого А влево; А[0]:= А[7];А[1+1]:= А[1]; (1=0-6) |

|

||

ANL A,Rr |

01011rrr |

Логическое И содержимого А и регистра; А := A AND Rr |

|

||

ANL A,@Rr |

0101000r |

Логическое И содержимого А и ячейки Внутренней памяти данных; А := A AND (Rr) |

|||

ANL A,#d |

01010011 |

Логическое И содержимого А с непосредственным операндом; А := A AND d |

|||

ANL Pp,#d (P=1,2) |

100110pp |

Логическое И порта Р1(Р2) с непосредственНым операндом; Рр := Рр AND d |

|||

OUTL Pp,A |

001110pp |

Вывод содержимого А в порт Р1(Р2) Рр := А |

|||

ANLD Pp,A (P-4-7) |

100111pp |

Логическое И порта Р4(Р5-Р7) с A; Рр := Рр AND A[3-0] |

|||

ORLD Pp,A (P=4~7) |

100011pp |

Логическое ИЛИ порта Р4(Р5-Р7) с А; Рр := Рр OR А[3-0] |

|||

ANL BUS,ffd |

10011000 |

Логическое И порта BUS с непосредственным Операндом; BUS := BUS AND d |

|||

OUTL BUS,A |

00000010 |

Вывод содержимого А в порт BUS; BUS := A |

|||

JNC а |

11100110 |

Переход, если С = 0 |

|||

RETR |

10010011 |

Возврат из подпрограммы с восстановлением Состояния; SP :- SP-1; PC := (Sp[11-0]) PSW [7-4] := (SP[15-12]) |

|||

Также дополнительно необходима реализация директивы DD, которая имеет представленный ниже формат:

<имя> DB <начальное значение>, [< начальное значение>].