- •Введение

- •Раздел 1. Математические основы цифровой схемотехники Представление информации в эвм

- •Коды с выявлением ошибок

- •Коды с исправлением ошибок

- •Раздел 2. Алгебра логики и теоретические основы синтеза цифровых устройств Элементы математической логики

- •Формы логических функций и их использование для синтеза логических схем

- •Логические элементы и схемы. Классификация логических устройств

- •Методы минимизации логических функций

- •Раздел 3. Синтез комбинационных схем Этапы построения логической схемы

- •Мультиплексоры и демультиплексоры

- •Дешифраторы и шифраторы

- •Компараторы, сумматоры

- •Раздел 4. Триггерные элементы цифровых устройств Классификация триггеров и их общие характеристики. Асинхронный rs-триггер и его разновидности

- •Асинхронные триггеры с одним входом

- •Cинхронные триггеры Синхронные триггеры со статическим управлением.

- •Синхронные триггеры, построенные по принципу двухступенчатого запоминания информации.

- •Раздел 5. Синтез цифровых автоматов Регистры. Регистр сдвига

- •Счетчики по mod m. Реверсивные счетчики. Синтез последовательных схем

- •Раздел 6. Современное состояние и перспективы развития элементной базы и средств вычислительной техники

Раздел 3. Синтез комбинационных схем Этапы построения логической схемы

Знания из области математической логики можно использовать для конструирования электронных устройств. Электронные схемы, которые преобразовывают сигналы только двух фиксированных напряжений электрического тока, стали называть логическими элементами.

Логические элементы имеют один или несколько входов и один выход, через которые проходят электрические сигналы. Другие логические элементы построены из этих трех простейших и выполняют более сложные логические преобразования информации. Сигнал, выработанный одним логическим элементом, можно подавать на вход другого элемента, это дает возможность образовывать цепочки из отдельных логических элементов.Такие цепи из логических элементов называются логическими устройствами. Логические устройства же, соединяясь, в свою очередь образуют функциональные схемы (их еще называют структурными или логическими схемами). По заданной функциональной схеме можно определить логическую формулу, по которой эта схема работает, и наоборот.

Обработка любой информации на компьютере сводится к выполнению процессором различных арифметических и логических операций. Для этого в состав процессора входит так называемое арифметико-логическое устройство (АЛУ). Оно состоит из ряда устройств, построенных на рассмотренных выше логических элементах. Важнейшими из таких устройств являются триггеры, полусумматоры, сумматоры, шифраторы, дешифраторы, счетчики, регистры.

Конструирование логического устройства состоит из следующих этапов:

1. Построение таблицы истинности по заданным условиям работы проектируемого узла (т.е. по соответствию его входных и выходных сигналов).

2. Конструирование логической функции данного узла по таблице истинности, ее преобразование (упрощение), если это возможно и необходимо.

3. Составление функциональной схемы проектируемого узла по формуле логической функции.

После этого остается только реализовать полученную схему. Попробуем, действуя по этому плану, сконструировать устройство для сложения двух двоичных чисел (одноразрядный полусумматор).

Пусть нам необходимо сложить двоичные числа X и Y. Через P и Z обозначим первую и вторую цифру суммы: X + Y = PZ. Вспомните таблицу сложения двоичных чисел.

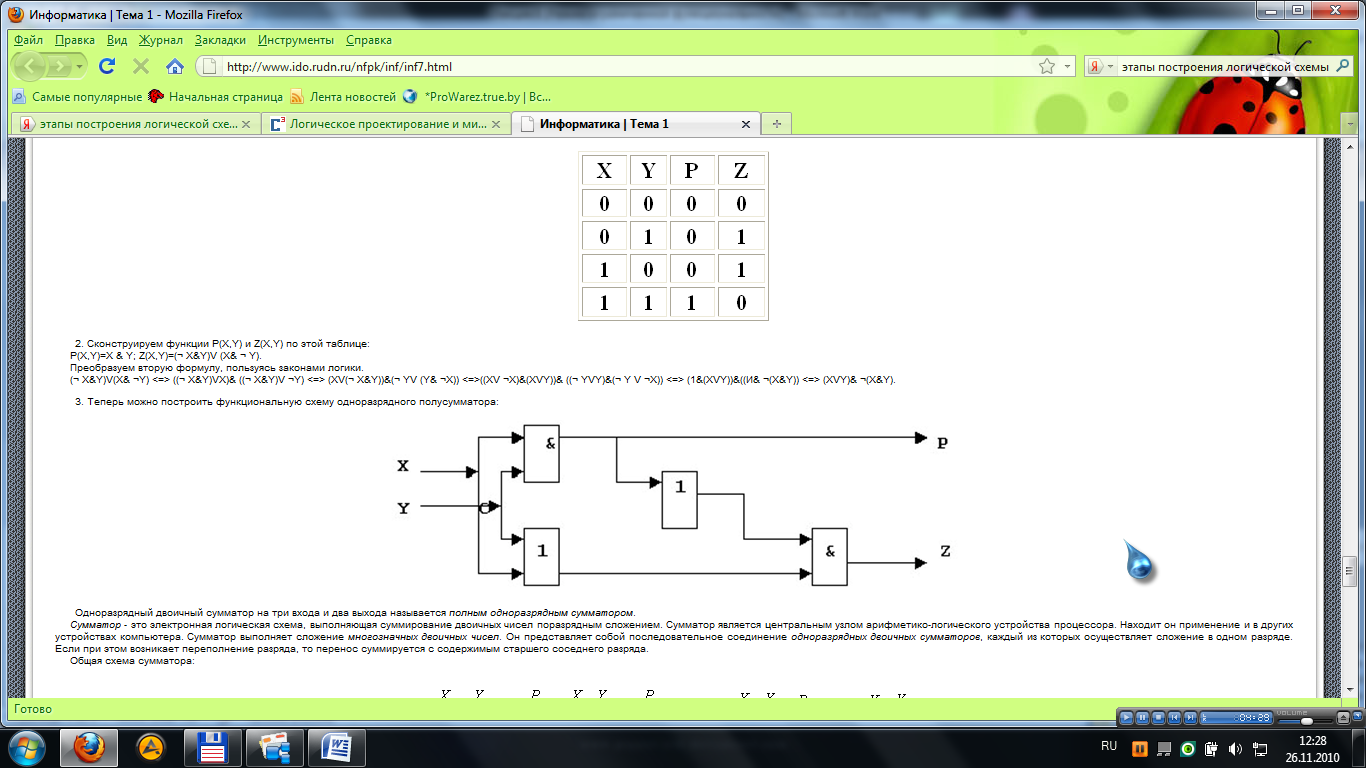

1. Таблица истинности, определяющая результат сложения, имеет вид:

2. Сконструируем функции P(X,Y) и Z(X,Y) по этой таблице: P(X,Y)=X & Y; Z(X,Y)=(¬ X&Y)V (X& ¬ Y).

3. Теперь можно построить функциональную схему одноразрядного полусумматора:

Одноразрядный двоичный сумматор на два входа и два выхода называется полным одноразрядным сумматором.

Мультиплексоры и демультиплексоры

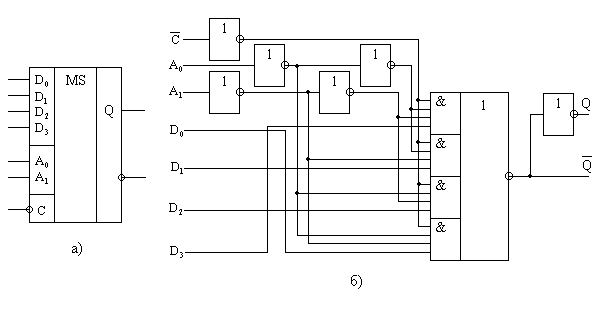

Мультиплексор является устройством, которое осуществляет выборку одного из нескольких входов и подключает его к своему выходу. Мультиплексор имеет несколько информационных входов (D0, D1, ...), адресные входы (А0 А1, ...), вход для подачи стробирующего сигнала С и один выход Q. На рис. 1 показано символическое изображение мультиплексора с четырьмя информационными входами.

|

Рисунок 1 |

Таким образом, подавая на адресные входы адреса различных информационных входов, можно передавать цифровые сигналы с этих входов на выход Q. Очевидно, число информационных входов nинф и число адресных входов nадр связаны соотношением nинф = 2nадр.

При отсутствии стробирующего сигнала (C = 0) связь между информационными входами и выходом отсутствует (Q = 0). При подаче стробирующего сигнала (C = l) на выход передается логический уровень того из информационных входов Di, номер которого i в двоичной форме задан на адресных входах. Так, при задании адреса AlA0 = ll2 = 310 на выход Q будет передаваться сигнал информационного входа с адресом 310, т. е. D3. Можно записать следующее логическое выражение для выхода Q:

|

((1) |

В тех случаях, когда требуется передавать на выходы многоразрядные входные данные в параллельной форме, используется параллельное включение мультиплексоров по числу разрядов передаваемых данных.

Мультиплексоры могут быть использованы для синтеза логических функций. При этом число используемых в схеме элементов (корпусов интегральных микросхем) может быть значительно уменьшено.

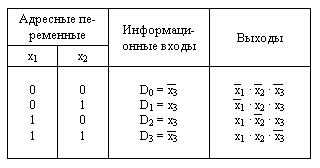

Логическое выражение мультиплексора (1) содержит члены со всеми комбинациями адресных переменных. Следовательно, если требуется синтезировать функцию трех переменных f(x1, x2, х3), то две из этих переменных (например, x1, х2) могут быть поданы на адресные входы А1, и А0, и третья x3 - на информационный вход.

![]()

|

Таблица 1 |

|

|

Рисунок 2 |

При синтезе комбинационных схем мультиплексоры могут быть использованы совместно с элементами некоторого базиса. Пусть общее число переменных функций n. Тогда, если мультиплексор имеет nадр адресных входов, то на них подаются nадр переменных, а на его информационные входы подаются функции n-nадр переменных.

Следует иметь в виду, что синтезируя логическое устройство с использованием мультиплексора, необходимо также построить вариант схемы без использования мультиплексора. Затем сравнением полученных вариантов определить, какой из вариантов оказывается лучшим по числу используемых в схеме корпусов интегральных схем.

Максимальное число входов мультиплексоров, выполненных в виде интегральных схем, равно восьми. Если требуется построить мультиплексорное устройство с большим числом входов, можно объединить мультиплексоры в схему так называемого дерева.

|

Рисунок 3 |

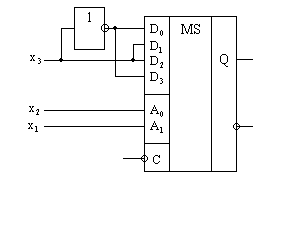

На рис. 3 показано символическое изображение демультиплексора с четырьмя выходами. Функционирование этого демультиплексора определяется табл. 4.

Таблица 4 |

|||||

Адресные входы |

Выходы |

||||

A1 |

A0 |

Y0 |

Y1 |

Y2 |

Y3 |

0 |

0 |

D |

0 |

0 |

0 |

0 |

1 |

0 |

D |

0 |

0 |

1 |

0 |

0 |

0 |

D |

0 |

1 |

1 |

0 |

0 |

0 |

D |

|

Рисунок 4 |