- •5.2. Single-chip microcontrollers with risc-architecture

- •5.3. Signaling processors

- •5.4. Basic concepts and tasks of neuron calculators

- •Part 6. Peripheral devices

- •6.1. External memory − magnetic and optical disk drives, flash memory

- •6.2. Video systems − monitors, video cards, devices of video data processing

- •6.3. Audiosystems − sound card, microphone, acoustic system

- •6.4. Input devices − keyboard, manipulators, scanners, digital photo- and video camera

- •6.5. Output devices − printers, plotters, projectors

- •6.6. Modems

5.2. Single-chip microcontrollers with risc-architecture

СІSС- microcontrollers are characterized by the developed enough system, for example, the microcontrollers of series i80x51 have 111 commands. The analysis of the programs showed however, that 20% commands were used in 80% cases, and decoder of commands occupies over 70% all area of crystal. Therefore for MP developers there was an idea to reduce the amount of commands, give to them common format and to decrease the area of crystal, id est to use RІSС (Reduced Instruction Set Computer) architecture.

The feature of controllers, executed under RISС- architecture, is that all commands are executed for one-three cycles, while in СІSС-controllers − for one-three computer cycles, each of which consists of a few clocks, for example for і80 х 51 − of 12 clocks. Therefore RІSС-controllers have a considerably more operating speed. However more complete set of instructions of СІSС- controllers in some cases assists the economy of execution time of certain fragments of the program and economy of the programs memory.

The typical representatives of RІSС-processors are РІС- controllers (Реriferial Іnterface Соntroller) of firm production "Місrochip". РІС-controllers are applied in the systems of high-speed control by motor-car and by electromotors, devices of domestic electronics, telephone attachments with АВН, systems of guard with a report on a telephone line, miniATS. Separate LSI differ in a bit of ROM: from 12 to 14 bits for the series РІСІ6Схх and 16 bits for the series РІС17Схх. Due to the brief amount of commands (from 33 to 35) all commands occupy one word in memory. Duration of every instruction execution, except the commands of branching, presents four clocks − one cycle (200 ns at frequency 20 Mhz). Operative storages of data are executed under a circuit with a random sample and possibility of the immediate addressing in code of command for any cell. A stack is realized hardwarily with a depth 2, 8 or 16 cells. There is the system of interrupt almost in all РІС-controllers, a source of which is a timer, and also change of signals state at some inputs. In РІС- controllers the bit of defence is foreseen of ROM, that prevents an illegal printing-down.

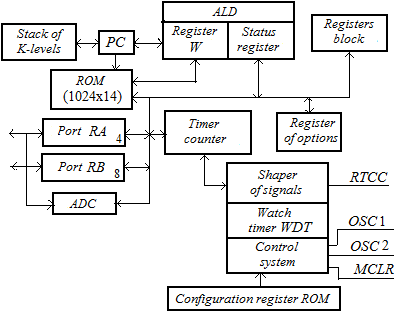

Architecture of РІС-controllers. Let us consider architecture of РІС-controllers on an example of LSI РІС16С71 (fig. 5.5). Basis of architecture are separate busses and storage areas for data and commands. A data bus and cell of RAM are a 8-bit, and bus of commands and programmatic memory (ROM) − by a 14-bit; a 14-bit command gets out for one cycle.

A two-step conveyer provides a simultaneous choice and execution of commands. The set of instructions contains 35 commands. All commands are executed for one cycle, except for the commands of transitions which are executed for two cycles.

Fig. 5.5. Block diagram of controller РІС16С71

The block diagram of controller contains:

-

eightlevel hardware stack;

-

13-bit programmatic counter РС;

-

8-bit ALD;

-

RAM, which consists of 36-th 8-bit РЗП;

-

15 registers of the special functions SER (on fig. 5.5 the register of the indirect addressing W and registers of status, options and configuration of ROM are represented);

− 8-bit timer-counter with 8-bit programmatic prescaler;

-

the module of ADC with four inputs;

-

13 lines of input-output (fourdigit port RА, 8-bit port RВ, line of RТСС);

-

watch timer;

− shaper of external signal RТСС or signal of watch timer;

-

system of control and synchronization with an internal generator.

РІС-controllers compete with single-chip microcomputer and SCM after parameters. Some modifications of РІС- controllers have a greater operating speed, than SCM. РІС- controllers and SCM are applied in built-in control systems of different purpose.

Single-chip АVR-microcontrollers are 8-bit highly productive RISC-controllers of general purpose. They were created by the group of developers of research center of firm "Аtmel Соrр" (Norway), the initials of which formed the brand АVR. The feature of АVR-microcontrollers is their wide nomenclature which enables to the user to choose a microcontroller with minimum hardware redundancy and, thus, the least cost. So, devices enter into the nomenclature of group АТ90S with ROM of a capacity 1÷8 Kb with the different sets of periphery in corps with the amount of terminals 8÷48. Presently there are three families of АVR − Тіnу, Сlаssіс and Меgа. The microcontrollers of Тіnу − are cheaper in all and have the simplest structure, Меgа − most powerful, and Сlаssіс − occupy intermediate position between them.

The set of АVR instructions counts to 133 different instructions. Distinguish five groups of АVR commands: conditional branching, absolute branching, arithmetic and logical operations, commands of data transfer, commands of opeation with bits. In the last developments of АVR of Меgа family the function of hardware multiplication is realized. After the amount of the realized constructions of АVR-microcontrollers they use СІSС-processors more, than processors of RІSС type. In РІС-controllers the set of instructions counts similar up to 75 different instructions, and in МСS51 it presents 111.

On the whole progressive RISC-architecture АVR in combination with the extended set of instructions enables to create the compact programs with high-rate of implementation.