- •Введение.

- •Цели и задачи дисциплины.

- •Связь с другими дисциплинами и необходимый уровень подготовки.

- •Кодирование логической и двоичной информации электрическими сигналами.

- •Характеристики электрических сигналов.

- •Простейшие логические операции и их схемотехническая реализация (диодные схемы).

- •Ттл элемент, работа схемы, основные характеристики.

- •Разновидности логических элементов и серии интегральных микросхем.

- •Соединения логических элементов и радиокомпонентов.

- •Схемотехника функциональных устройств.

- •Схемотехника последовательностных устройств.

- •Триггеры.

- •Счётчики.

- •Двоичные счетчики.

- •Недвоичные счетчики.

- •Регистры.

- •Параллельные регистры.

- •Последовательные (сдвиговые) регистры.

- •Комбинационные устройства.

- •Дешифраторы.

- •Линейный дешифратор.

- •Матричный дешифратор.

- •Пирамидальный дешифратор.

- •Дешифраторы интегрального исполнения.

- •Мультиплексор и демультиплексор.

- •Мультиплексоры интегрального исполнения.

- •Сумматоры.

- •Одноразрядные комбинационные сумматоры.

- •Многоразрядные сумматоры.

- •Последовательный многоразрядный сумматор.

- •Параллельный многоразрядный сумматор.

- •Ускоренный перенос.

- •Арифметико-логическое устройство.

- •Устройства памяти.

- •Статические элементы оперативных запоминающих устройств.

- •Запоминающий элемент на биполярных транзисторах.

- •Запоминающий элемент на полевых транзисторах.

- •Динамический запоминающий элемент оперативных запоминающих устройств.

- •Запоминающие элементы пзу.

- •Организация бис зу.

- •Построение запоминающих устройств эвм.

- •Программируемые логические матрицы.

- •Формирователи.

- •Определение интервала времени по заданным уровням сигналов в цепях первого порядка.

- •Формирователи периодических сигналов.

- •Несимметричный мультивибратор на логических элементах.

- •Формирователь фронтов (спадов) — триггер Шмитта.

- •Формирователи импульсов.

- •Формирователь на интегрирующей rc цепи.

- •Одновибратор с дифференцирующей rc цепью.

- •Одновибраторы интегрального исполнения.

- •Интерфейсные устройства.

- •Буферные устройства.

- •Передача сигналов по линиям связи.

- •Несимметричные линии связи.

- •Согласование линий связи.

- •Симметричные линии связи.

- •Цифро-аналоговые и аналого-цифровые преобразователи.

- •Цифро-аналоговые преобразователи (цап).

- •Цифро-аналоговый преобразователь на суммировании токов.

- •Цифро-аналоговый преобразователь на матрице r-2r.

- •Аналого-цифровые преобразователи (ацп).

- •Параллельный ацп.

- •Ацп последовательного приближения (последовательные ацп).

- •Ацп двойного интегрирования.

- •Системы индикации.

- •Индикация состояния логического элемента.

- •Индикация состояния шин.

-

Ацп двойного интегрирования.

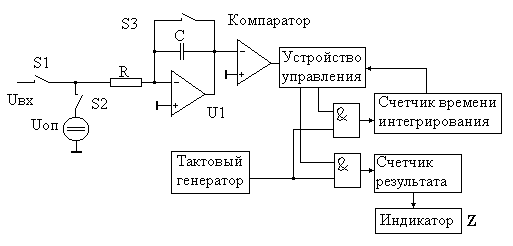

Структурно функциональная схема АЦП двойного интегрирования приведена на рис. 129.

Р ассматриваемое

устройство состоит из следующих

функциональных блоков:

ассматриваемое

устройство состоит из следующих

функциональных блоков:

устройство управления с ключами S1, S2, S3,

интегратор,

компаратор,

счетчик времени интегрирования,

счетчик результата,

т

Рис. 129. Структурно функциональная схема

АЦП двойного интегрирования.

индикатор.

Рассмотрим работу этого АЦП.

В исходном состоянии ключи S1,

S2 разомкнуты а ключ S3

замкнут. Замкнутый ключ S3

закорачивая конденсатор С превращает

интегратор в повторитель и его выходное

напряжение равно нулю. На первом этапе

измерения ключ S1 замыкается

, а ключ S3 размыкается.

Начинается процесс интегрирования

входного напряжения, длительность t1

которого постоянна и определяется

счетчиком времени интегрирования.

Выходное напряжение интегратора по

окончании первого этапа составляет

![]()

г![]() де

ni -- количество тактовых импульсов,

а Т -- период тактового генератора.

де

ni -- количество тактовых импульсов,

а Т -- период тактового генератора.

По окончании первого этапа ключ S1

размыкается, а ключ S2 замыкается,

начинается этап интегрирования эталонного

напряжения Uоп. При этом знак эталонного

напряжения выбирается противоположным

знаку входного напряжения. Так как

интегрируется эталонное напряжение,

то длительность второго этапа зависит

от U1(t1). По окончании второго этапа U1(t1)

= 0, срабатывает компаратор и устройство

управления останавливает счетчик

результата. Длительность второго этапа

определяется

![]() ,

а результат появляющийся на индикаторе

определяется

,

а результат появляющийся на индикаторе

определяется

![]() .

Эти выражения показывают, что отличительной

особенностью метода двойного интегрирования

является независимость получаемого

результата ни от частоты тактового

генератора 1/Т, ни от постоянной времени

τ = RC. Возможно получение результатов с

погрешностью не превышающей 0,01%, для

этого необходимо чтобы тактовая частота

на интервале t1+t2 оставалась постоянной.

Выполнение этого требования не

представляет сложности.

.

Эти выражения показывают, что отличительной

особенностью метода двойного интегрирования

является независимость получаемого

результата ни от частоты тактового

генератора 1/Т, ни от постоянной времени

τ = RC. Возможно получение результатов с

погрешностью не превышающей 0,01%, для

этого необходимо чтобы тактовая частота

на интервале t1+t2 оставалась постоянной.

Выполнение этого требования не

представляет сложности.

По методу двойного интегрирования работают микросхемы КР572ПВ5, ICL7136.

Лекция 40.

-

Системы индикации.

-

Индикация состояния логического элемента.

-

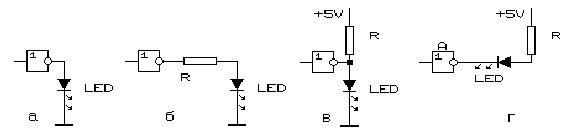

С целью определения состояния переменных на выходах как отдельных микросхем, так и устройств необходимы различные системы индикации. Наибольшее распространение получили визуальные (оптические) системы индикации с применением светоизлучающих диодов.

На рисунке приведены схемы включения светодиода для индикации состояния переменной на выходе логического элемента. Схема на рис.130 а применима для стандартных элементов, у которых выходной ток не превышает 16ма. Схема на рис.130 б используется для индикации на выходе элемента с повышенной нагрузочной способностью.

Рис.130. Индикация выхода логического элемента.

Величина добавочного резистора

рассчитывается по формуле

![]() ,

где

,

где

![]() —

напряжение и ток на светодиоде.

—

напряжение и ток на светодиоде.

Схема рис.130в применима для логических элементов с выходным каскадом выполненным с открытым коллектором. Величина резистора определяется соотношением

![]() .

.

Схемы на рис.118 а,б,в индицируют единичное

состояние. Схема рис.118г предназначена

для индикации нулевого состояния

переменной на выходе логического

элемента и величина резистора

рассчитывается по формуле ![]() ,

где

,

где

![]() —

напряжение питания,

—

напряжение питания,

![]() —

выходное напряжение логического элемента

низкого уровня.

—

выходное напряжение логического элемента

низкого уровня.

Лекция 41.