- •Введение.

- •Цели и задачи дисциплины.

- •Связь с другими дисциплинами и необходимый уровень подготовки.

- •Кодирование логической и двоичной информации электрическими сигналами.

- •Характеристики электрических сигналов.

- •Простейшие логические операции и их схемотехническая реализация (диодные схемы).

- •Ттл элемент, работа схемы, основные характеристики.

- •Разновидности логических элементов и серии интегральных микросхем.

- •Соединения логических элементов и радиокомпонентов.

- •Схемотехника функциональных устройств.

- •Схемотехника последовательностных устройств.

- •Триггеры.

- •Счётчики.

- •Двоичные счетчики.

- •Недвоичные счетчики.

- •Регистры.

- •Параллельные регистры.

- •Последовательные (сдвиговые) регистры.

- •Комбинационные устройства.

- •Дешифраторы.

- •Линейный дешифратор.

- •Матричный дешифратор.

- •Пирамидальный дешифратор.

- •Дешифраторы интегрального исполнения.

- •Мультиплексор и демультиплексор.

- •Мультиплексоры интегрального исполнения.

- •Сумматоры.

- •Одноразрядные комбинационные сумматоры.

- •Многоразрядные сумматоры.

- •Последовательный многоразрядный сумматор.

- •Параллельный многоразрядный сумматор.

- •Ускоренный перенос.

- •Арифметико-логическое устройство.

- •Устройства памяти.

- •Статические элементы оперативных запоминающих устройств.

- •Запоминающий элемент на биполярных транзисторах.

- •Запоминающий элемент на полевых транзисторах.

- •Динамический запоминающий элемент оперативных запоминающих устройств.

- •Запоминающие элементы пзу.

- •Организация бис зу.

- •Построение запоминающих устройств эвм.

- •Программируемые логические матрицы.

- •Формирователи.

- •Определение интервала времени по заданным уровням сигналов в цепях первого порядка.

- •Формирователи периодических сигналов.

- •Несимметричный мультивибратор на логических элементах.

- •Формирователь фронтов (спадов) — триггер Шмитта.

- •Формирователи импульсов.

- •Формирователь на интегрирующей rc цепи.

- •Одновибратор с дифференцирующей rc цепью.

- •Одновибраторы интегрального исполнения.

- •Интерфейсные устройства.

- •Буферные устройства.

- •Передача сигналов по линиям связи.

- •Несимметричные линии связи.

- •Согласование линий связи.

- •Симметричные линии связи.

- •Цифро-аналоговые и аналого-цифровые преобразователи.

- •Цифро-аналоговые преобразователи (цап).

- •Цифро-аналоговый преобразователь на суммировании токов.

- •Цифро-аналоговый преобразователь на матрице r-2r.

- •Аналого-цифровые преобразователи (ацп).

- •Параллельный ацп.

- •Ацп последовательного приближения (последовательные ацп).

- •Ацп двойного интегрирования.

- •Системы индикации.

- •Индикация состояния логического элемента.

- •Индикация состояния шин.

-

Запоминающий элемент на полевых транзисторах.

Известно несколько структур полевых транзисторов, отличающихся полярностью питающих и управляющих напряжений. Поэтому при построении ячейки памяти необходимо использовать структуры, которые наилучшим образом подходят к используемым сериям логических элементов. Для серий логических элементов, имеющих положительное напряжение питания, лучше всего использовать МОП транзисторы с индуцированным каналом типа “n”, так как у этих транзисторов напряжение питания и напряжение отсечки -- положительны. Схемотехнической основой построения ячейки является статический триггер, у которого в стоковых цепях транзисторов использованы n - канальные полевые транзисторы в режиме источников тока. Схема ячейки приведена на рис. 78.

Транзисторы VT1, VT2 -- n - канальные с изоляцией канала от затвора обратносмещённым p-n переходом в режиме источника тока используются в качестве стоковых нагрузок транзисторов VT3,VT4, которые образуют статический триггер. Транзисторы VT5,VT6 , так называемые боковые транзисторы, предназначены для управления записью и считыванием информации в статическом триггере.

Рис. 78. NMOP элемент памяти.

NMOP элемент памяти имеет преимущества состоящие в том, что в схеме используются только транзисторы (резисторов нет) а это существенно упрощает технологию и удешевляет микросхему памяти.

Рассмотренные схемы ячеек памяти используются в микросхемах статической памяти и на кристалле кремния они занимают много места, что при ограниченных размерах кристалла приводит к ограничению объема микросхем статической памяти.

С целью увеличения объема запоминаемой информации в одной микросхеме необходимо искать другие схемотехнические решения для ячеек памяти.

Лекция 26.

-

Динамический запоминающий элемент оперативных запоминающих устройств.

В настоящее время для построения оперативных запоминающих устройств находят повсеместное применение динамические запоминающие элементы.

Принцип работы таких устройств основан на относительно длительном времени хранения заряда конденсатором. В качестве запоминающей емкости используют псевдоконденсатор, образованный на кристалле между электродами затвор (З) -- исток (И).

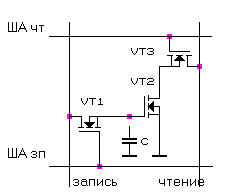

На рис.79 приведена одна из схем динамического запоминающего элемента.

Как видно из схемы, запоминание осуществляется на псевдоконденсаторе С затвор - исток транзистора VT2. Транзисторы VT1 и VT3 предназначены для управления записью и чтением информации. Если “1” будем кодировать высоким уровнем (+5В), то для записи “1” этот сигнал нужно подать на шину записи. При наличии выборки данной ячейки -- на ШАзп подан высокий уровень , транзистор VT1 откроется и псевдоконденсатор С зарядится до высокого уровня напряжения. Для чтения запомненной информации шину чтения предварительно заряжают высоким уровнем, и при подаче высокого уровня на ШАчт -- выборка данной ячейки при чтении, откроется транзистор VT3.

Рис. 79. Динамический запоминающий элемент.

Наличие высокого уровня напряжения на затворе транзистора VT2 приводит и к его открытию, и предварительный заряд с шины чтения стечет через открытые транзисторы VT2 и VT3. При чтении “1” на выходе ( на шине чтения) получаем низкий уровень, т.е. инверсию единицы. Хотя затворные и истоковые цепи МОП транзисторов имеют высокие сопротивления, псевдоконденсатор С довольно быстро разряжается, что приводит к потере запомненной информации, чтобы зто не происходило нужно примерно каждые 3мсек подзаряжать конденсатор С. Этот процесс называют регенерацией памяти.