Цифровая электроника

.pdf

61

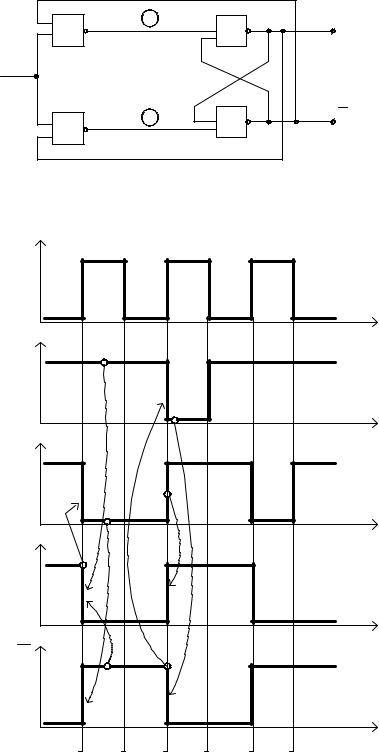

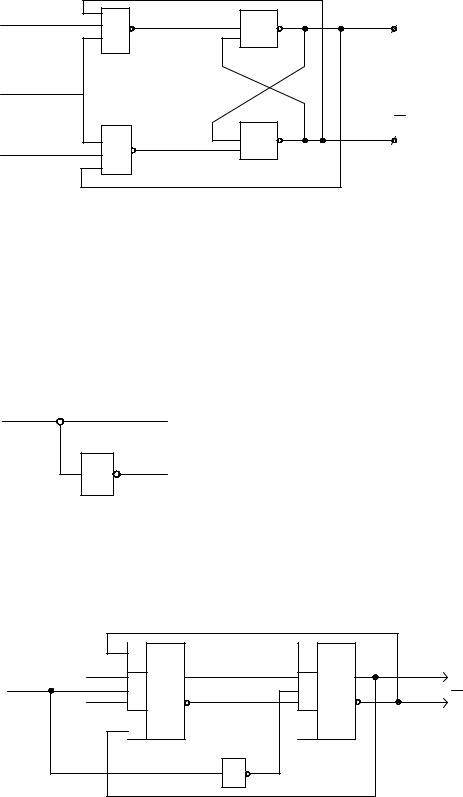

I. Т-три(счгглиетртный)иггер |

|

|

– предподсчеталяназначенвходныхдвоичных |

|||

(прямоуго)импу. льсовных |

|

Дополнительно |

их |

используютвкачдествелителей |

||

частоты. |

|

|

|

|

|

|

Различаютодно |

- идвух |

ступенчатыеТ |

-триггеры. |

|

||

А)Схемотехникаодноступенчатого: |

|

|

|

|

|

|

& |

|

а |

|

& |

|

Q |

|

|

|

|

|||

T-вход |

|

|

|

|

|

|

& |

|

b |

|

& |

|

Q |

|

|

|

|

|

||

|

|

|

R-S триггер |

|

|

|

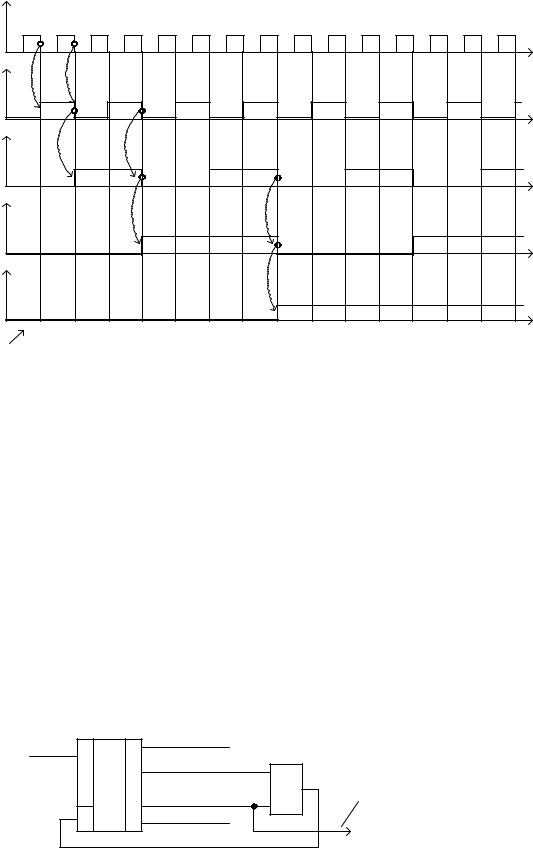

Рассмотримвременную |

|

диаграммуработытакогостройства: |

|

|||

T -вход |

|

|

|

|

|

|

|

|

Режим |

Режим |

|

|

|

|

хранения |

хранения |

|

|

||

|

|

|

|

|

|

t |

a |

|

|

|

|

|

|

|

|

|

|

|

|

t |

b |

|

|

|

|

|

|

|

|

|

|

|

|

t |

Q |

|

|

|

|

|

|

|

|

|

|

|

|

t |

Q |

|

|

|

|

|

|

|

|

|

|

|

|

t |

62

Каквидноизвременныхдиаграмм,данномслучаеТ |

|

-триггер – этоустройство, |

|

котороеменясв т |

оесостояннапротивоположное |

пофронтукаждоговходного |

|

импульса.Т.е.впотокепрямоугольных |

импульсоввыполняетсяследующееусловие: |

|

|

~

i

T -вход

t

t

Q -выход |

t |

~

2i

Каквиизданныхнодиаграмм,периодследования |

|

|

|

|

|

|

|

|

|

|

|

ыходныхимпульсо |

в |

||||||||

увеличиваетсяровновдв,следовательно |

|

|

|

|

|

|

|

частотавыходныхимпульсовровновдв е |

|

|

|||||||||||

уменьшае.Т..отдельновзяТ ыйся |

|

|

|

|

|

|

|

|

-триггерявляетсяделителемчастотынадва. |

|

|

||||||||||

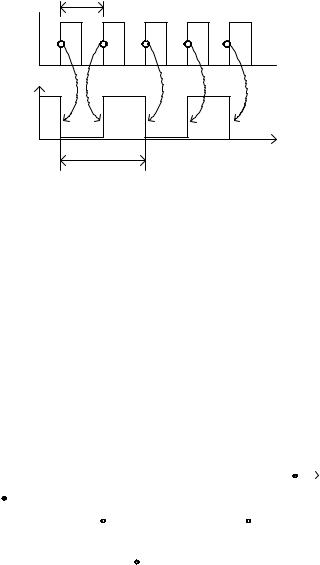

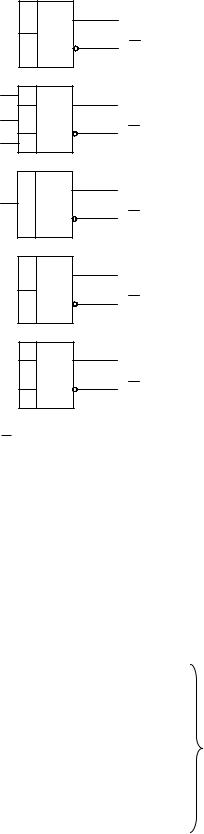

Б) Припостроениидвоичныхсчетчик,основукот ставляютрыхТ |

|

|

|

|

|

|

|

|

-триггеры, |

||||||||||||

желательноиспользованиедвухст |

|

|

|

|

|

упенчатыхТ |

-триггер,схемотехникав |

построения |

|||||||||||||

которыхследующая: |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q -выход |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

T -вход |

|

S |

|

|

|

|

|

|

|

S |

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

C |

|

|

|

|

|

|

|

C |

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

R |

|

|

|

|

|

|

|

R |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

R -S -C |

|

|

|

|

R -S -C |

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

T |

|

|

|

|

|

|

|

T2 |

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

Slave |

|

|

|

|

|

|

Master |

|

|

|

|

|

|

|||

Вданномслуча |

|

|

епринципработыТ |

|

|

-триггеаналогиченпредыдуще |

му,стем |

|

|||||||||||||

отлич,чтопрТ=ием |

|

|

0, |

T1 |

- врежимехр,ан ния |

|

T2 - врабочемрежиме. |

|

|

||||||||||||

=>ранееза |

писаннаяв |

T1 инфопермацезаписываетсятр ггер |

T2 . |

|

|||||||||||||||||

ПриТ= |

|

1,наоборот, |

T1 - врабсостояниичем,а |

|

|

T2 - врежимехран. ния |

|

||||||||||||||

=>и |

нверснаяинформация |

|

|

с T2 |

переписывается T1 . |

|

|

||||||||||||||

63

Т.о.данноеустройствотакжеиз |

менясвоестояннапротпоивоположное |

каждовходимно,пульсувыполняомуэтупроцсрезу: дурут

T -вход

Q -выход |

T1 Хр. Раб. Хр. Раб.

T2 Раб. Хр. Раб. Хр.

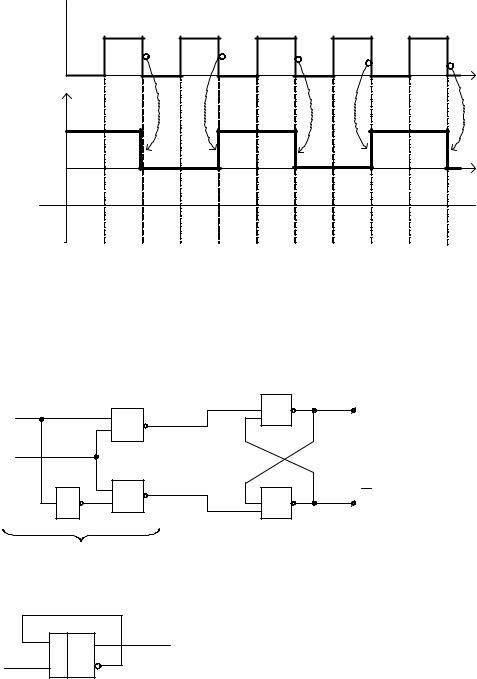

II. D-триггер( зад)ержки |

– используетсядляформированиярасчетов |

хранения.

А) Одноступенчатый D-триггер:

D -вход |

& |

& |

Q |

|

|

|

|

C -запись |

|

|

|

1 |

& |

& |

Q |

|

R-S триггер

Схема управления

D-триггрежимевсчетномвключаетсятак:

выход

D T -вход C

НаличиевсхемэлементаНЕавтоматическиустраняетвозмп явленияжность |

|

|

запрещенногосостояниядля |

R-S-триггера. |

Востальномработаустройствааналогична |

работесинхронного |

R-S-триггера. |

|

Т.е.реализуетсяследующаявременндиагр: аммая

64

D -вход

t |

C -вход |

t |

Q -выход |

|

Хра- |

Раб. |

Хран |

|

|

|

|

|

нение |

запись |

запись "0" |

запись "0" |

запись "1" |

t |

|

|

ение |

||||||

|

|

"1" |

|

|

|

||

Данноеустройствоосуществляетзаписьинфвходармации |

|

|

|

D втриггерпо |

|||

фронтуимпС льса |

. Всвязиэт |

имвходСчастоназываютвходомзаписи, |

|

|

D – |

||

информационнымвходом.

Б)Двухступенчатый D-триггер:

D -вход |

S |

|

S |

Q |

|

|

|

||

C -запись |

C |

|

C |

|

|

|

Q |

||

1 |

R |

|

R |

|

|

|

|||

|

T1 |

|

T2 |

|

|

Slave |

1 |

Master |

|

Принципработыаналогиченодноступенчатому |

|

|

D-триггеру,стойлишьразницей, |

|

чтопокончимпульсазапнтр сиггер |

|

T2 записываетсебяинформациютриггера |

|

|

T1 =>н авыходепереписанная |

D-входаинфпоявитсярмация |

оокончанииимпульса |

||

записи. |

|

|

|

|

III. J-K-триггеруниверсальный( ) |

|

|

|

|

А)Одноступенчатый J-K-триггер:

65

J |

& |

& |

Q |

|

|

||

C -вход |

|

|

|

K |

& |

& |

Q |

|

|||

|

|

||

|

|

|

Спомощьюанализаработыустройслегкодоказ,чтовходывать |

|

J и K |

|

эквивалентнывходам |

R и S |

синхронного R-S-триггера. |

Вход J устанавливает«1»,входК |

– «0». |

|

|

|

Если J=K = то«1»,получаемклассическийодноступенчатыйТ |

-триггер. |

||

Есливход |

дополнитьэлементомНЕ |

: |

|

- |

J |

D вход |

|

1 |

K |

|

,тополучаем D-триггер. |

Т.о.действительно |

J-K-триггерпозволяетсоздатьлюбойизранеерассмотренных |

триггеров.

Б)Двухступенчатый J-K-триггер:

C -вход |

J |

& |

S |

Q |

|

C |

C |

|

|

|

K |

Q |

||

|

|

|

||

|

|

& |

R |

|

|

|

|

1 |

|

|

|

Slave |

Master |

|

Наличиеархитектуры |

Slave – Master указываетнато,чтоинформациянавыходе |

|

||

появитсятолькосрезуили(покончанию)импульсанаС |

|

-входеимпульс( записи). |

|

|

Графическиеобозначения: |

|

|

|

|

66

R |

T |

Q |

|

R-S – триггер |

|

|

|

|

S |

|

Q * |

|

|

|

S |

T |

Q |

C |

|

Синхронный R-S – триггер |

R |

|

Q * |

|

|

|

|

T |

Q |

T |

|

Т – триггер |

|

|

Q * |

D |

T |

Q |

|

D – триггер |

|

S |

|

|

|

Q * |

|

J |

T |

Q |

C |

|

J-K – триггер |

|

Q * |

|

K |

|

|

|

|

|

Q * - можеттсутствовать. |

||

§ 3.4 Классификация, назначениерегистров

Регистры – это цифровыеустройства,предназдляхраненияесколькихаченные |

|

||

бит информации одновременно. |

Какправило,количествобит, |

хранимыхврегистрах, |

|

кратночетырем |

. Приэтомобщепринятаследующметрика: я |

|

|

4бит |

– тетрада |

|

|

8бит |

– байт |

|

|

16бит |

– слово |

|

|

32бит |

– двойноеслово |

|

|

64бит |

– квадрослово |

|

|

илих -разрядныйрегистр. |

|

|

|

Взависимостиотназначения |

,всер гистрыподразделяются |

: |

|

67

А) |

Регистрыхранения |

|

|

|

|

|

|

|

|

|

– предляназхраначеныенияопределенного |

количествабит |

||||||||||||||||||||||||||

одновременно. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

Б) |

Сдвиговыерегистры |

|

|

|

|

|

|

|

|

– предлянзаипзначиоссдвигаленыдующего |

|

|||||||||||||||||||||||||||

инфовправоиливлевомацтермин.Приэтомвправоиливлевоноусловныйит |

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||

характер. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

Болееточнаятерминологпоявиласьизобретениемкропроцессора. |

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||

Рассмотримнапримере8 |

|

|

|

|

|

|

|

|

|

|

|

-разрядного регистра: |

|

|||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Сдвиг влево |

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D7 |

|

D6 |

|

D5 |

|

|

|

|

D4 |

|

D3 |

|

D2 |

|

|

D1 |

|

D0 |

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

Стар |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Млад |

|

||||||||||

|

|

|

ший |

|

|

|

Сдвиг вправо |

|

|

|

|

|

ший |

|

||||||||||||||||||||||||

|

|

|

бит |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

бит |

|

||||||||||

В) |

Униврерсальныегистры |

|

|

|

|

|

|

|

|

|

|

|

|

– |

предляназначенывыполненияодновременно |

|

||||||||||||||||||||||

функцийсдвиговогорегистрахранения.

РегистрыявляютсяосновойдляпостроенияЛЮБЫХинтеллектуальныхустройств

(микропроцессоры, |

микроконт,конве.д.),атакжертороволявляютсяеров |

|

|

||

оптимальнымипреобразователями |

|

двоичного кодаизп раллельногоформатав |

|||

последовательный.Основнойхарактеристикойрегистраявляетсяегоинформационная |

|

|

|||

емкостьилиразрядность. |

|

|

Основойдляпостро |

ениярегистровслужат |

D-триггеры. |

Количество D – триггеровопределяе |

т информационнуюемкость |

регистра. |

|||

Вкачествепримрассмо |

|

|

тримсхемпотехникустроения4 |

|

-разрядныхрегистров: |

А)Регистрхранения: |

|

|

|

|

|

D0 |

D |

T |

Q0 |

|

|

|

C |

|

|

|

|

D1 |

D |

T |

Q |

|

|

|

C |

1 |

|

|

|

Входная |

|

Выходная |

|

|

|

информация |

|

|

информация |

|

|

D2 |

D |

T |

Q2 |

|

|

|

C |

|

|

|

|

D3 |

D |

T |

Q3 |

|

|

C -запись C

|

|

|

|

|

|

|

|

68 |

Каквидноизсхемотехн |

|

|

ики, попримпульсаходузаписиС,инфвходармация |

|

||||

переписываерегистрхранинемдопотсследующеготупленияимпульсазаписи. |

|

|

|

|

|

|

||

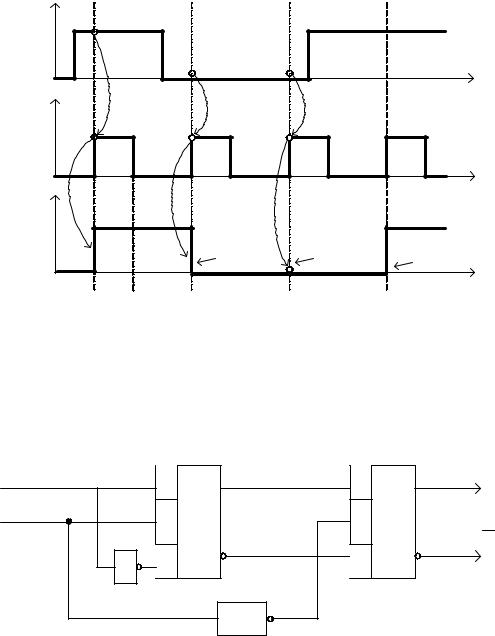

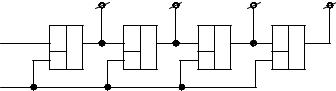

Б)Сдвире:гистровый |

|

|

|

|

|

|

|

|

|

|

D0 |

|

D1 |

|

D2 |

D3 |

|

D -вход D |

T |

D |

T |

D |

T |

D |

T |

|

C |

|

C |

|

C |

|

C |

|

|

C -запись/ сдвиг |

|

|

|

|

|

|

|

|

Рассмотримработуданногоустройстванапримеревременныхдиаграм |

|

|

|

|

м: |

|||

C |

|

|

|

|

|

|

|

|

D |

|

|

|

|

|

|

t |

|

|

|

|

|

|

|

|

|

|

"1" |

|

"0" |

|

"0" |

"1" |

|

t |

|

|

|

|

|

|

|

|

||

D0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

"1" |

|

D1 |

|

|

|

|

|

|

t |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

"0" |

|

D2 |

|

|

|

|

|

|

t |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

"0" |

|

D3 |

|

|

|

|

|

|

t |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

"1" |

|

|

|

|

|

|

|

|

t |

|

Пустьпри |

t |

=все0 |

|

ti = 0. |

Такимобр,д устройствонноезомд йствительно |

|

||

выполняетзаписдвигинформациись одновременно. |

|

|

|

|

Приэтом |

есликоличество |

||

импульсовпадазапиразирегисядностью, ав оматическираосуществляется |

|

|

|

|

||||

переводинформацииизпоследова |

|

|

|

тельногоформатавпараллельный. |

|

|||

|

|

§ 3.5 Классификация,назначениедвоичныхсчетчико |

в |

|||||

Счетчики – цифровыеустр,которыйства |

|

|

епредляназначеныподсчета |

количества |

||||

входных импульсвыдачиинформацииэб |

|

|

|

|

томколичествеопределенном |

ходе. |

||

|

|

|

|

|

|

|

|

|

69 |

Взависимостиотназначения |

|

|

|

всчетчикиподразделяются |

: |

|

|||

А)Суммирующие |

– увеличиваютсвостоянаедипокаждониецу |

|

муочередном у |

||||||

входномуимпульсу. |

|

|

|

|

|

|

|

|

|

Б)Вычитающие |

|

– уменьшсвостоянаедиютниецу |

|

покаждомуочередному |

|||||

входномуимпульсу. |

|

|

|

|

|

|

|

|

|

В)Универсальныеили(ре |

|

|

|

версивные) |

– одномогутвыполнятьремефу кциино |

|

|

||

суммирующеговычитающего |

|

|

|

счетчиков. |

|

|

|

||

Основнойхарактсчеристикой |

|

|

чикаявляетмаксимальнаяего информационная |

|

|

||||

емкость. |

ОсновойдляпостроениясчетчиковслужатТ |

|

|

|

-триггеры. |

КоличествоТ |

-триггеров |

||

какразиопределяетмаксимальнуюинформационнуюемкость,именноемкость[ ] = |

|

|

|

|

|

2n , |

|||

где n – количествоТ |

-триггеров. |

|

Вкачествепримрассмотрим |

схемотехнипринципку |

|

||||

работы4 |

-разрядногосуммирующегосчетчика: |

|

|

|

|

|

|

||

|

|

D0 |

|

D |

|

D2 |

D |

|

|

|

|

|

|

1 |

|

3 |

|

|

|

T-вход T |

|

T |

|

|

T |

T |

|

|

|

|

R |

|

R |

|

|

R |

R |

|

|

Reset |

|

|

|

|

|

|

|

|

|

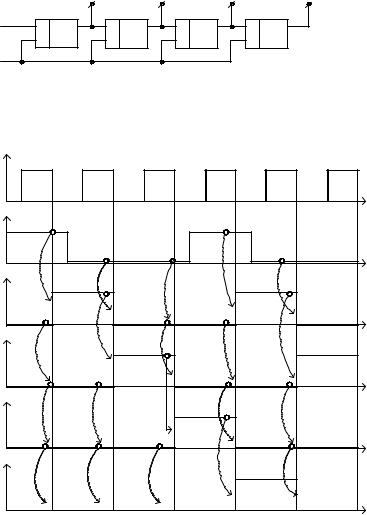

Рассмотримвременные |

|

|

диаграммы: |

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

70 |

1 |

2 |

|

4 |

|

6 |

8 |

10 |

12 |

14 |

15 |

|

|

D0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

"1" |

|

"0" |

|

"0" |

|

|

|

D1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

"0" |

|

"0" |

|

"0" |

|

|

|

D2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

"1" |

|

"0" |

|

"1" |

|

|

|

D3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

"0" |

|

"1" |

|

"1" |

|

|

|

Reset |

|

|

|

|

|

|

|

|

|

|

|

|

Сделаемнескольковремср:послнныхзов |

|

|

|

|

е5 |

им,послеульи8по12але |

|

. Т.е. |

||||

сколькоимпоступилоульсов,ровнотакуюинформацию,новдвоичномкоде,мы |

|

|

|

|

|

|

|

|

||||

снимаем. |

Каквидноизвременныхдиаграмм,действительно,навыходах |

|

|

|

|

|

D3 − D0 |

в |

||||

двоичномк детражаетсяинформацияколичест |

|

|

|

|

веп |

оступвходныхимпульсоввших |

|

, |

||||

т.е.даннустройствосуществляетихподсчет. |

|

|

|

|

|

|

|

|

|

|

||

Дляполучениявычитающегосчетчика,достатвыхпоследующегочноТ |

|

|

|

|

|

-триггера |

||||||

соединитьсовходомпредыдущего |

|

|

|

. |

|

|

|

|

|

|

||

Особыйкласспредставляютсчетчики,которыеиспользуюткачдестве |

|

|

|

|

|

|

лителей |

|||||

часпеременнымтотыкоэффициентомделения. |

|

|

|

|

Типоваясхемаихвключенияследующая: |

|

|

|

||||

T -вход |

T Ст |

1 |

D0 |

1 |

0 |

|

|

|

|

|

|

|

D1 |

0 1 |

|

|

|

|

|

|

|||||

( f0 ) |

|

|

2 |

& |

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4 |

D2 |

1 |

1 |

f |

|

|

|

|

|

|

|

R |

D3 |

0 |

1 |

0 6 |

|

|

|

|||

|

|

8 |

|

|

|

|

||||||

|

|

|

|

|

:6 |

|

|

|

|

|

|

|

Дляпостроенделителейпроизвольнымкоэффициентомядел обходимония |

|

|

|

|

|

|

|

|||||

выводыдвоичногосчетч,гдепр единицакасутствуетдлядвоичног |

|

|

|

|

|

|

очисделаителя |

, |

||||