МК

.pdfПродовження табл. 4

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

10 |

11 |

12 |

13 |

14 |

15 |

16 |

17 |

18 |

19 |

20 |

21 |

22 |

23 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Atmega163 |

16 |

512 |

1K |

130 |

32 |

17 |

1 |

1 |

1 |

2 |

1 |

3 |

Y |

Y |

Y |

8 |

Y |

- |

Y |

4,0-5,5 |

0-8 |

40-Pin DIP |

|

44-Pin TQFP |

|||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

40-Pin DIP |

|

Atmega16L |

16 |

512 |

1K |

130 |

32 |

17 |

1 |

1 |

1 |

2 |

1 |

3 |

Y |

Y |

Y |

8 |

Y |

- |

Y |

2,7-5,5 |

0-8 |

|

|

44-Pin TQFP |

|||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Atmega16 |

16 |

512 |

1K |

130 |

32 |

17 |

1 |

1 |

1 |

2 |

1 |

3 |

Y |

Y |

Y |

8 |

Y |

- |

Y |

4,0-5,5 |

0-16 |

40-Pin DIP |

|

|

|||||||||||||||||||||||

44-Pin TQFP |

|||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

40-Pin DIP |

|

Atmega323L |

32 |

1K |

2K |

130 |

32 |

19 |

1 |

1 |

1 |

2 |

1 |

4 |

Y |

Y |

Y |

8 |

Y |

- |

Y |

2,7-5,5 |

0-4 |

|

|

44-Pin TQFP |

|||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Atmega323 |

32 |

1K |

2K |

130 |

32 |

19 |

1 |

1 |

1 |

2 |

1 |

4 |

Y |

Y |

Y |

8 |

Y |

- |

Y |

4,0-5,5 |

0-8 |

40-Pin DIP |

|

|

|||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

44-Pin TQFP |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Atmega103L |

128 |

4K |

4K |

121 |

48 |

16 |

1 |

1 |

- |

2 |

1 |

4 |

Y |

Y |

Y |

8 |

- |

- |

Y |

2,7-3,6 |

0-4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Atmega128L |

128 |

4K |

4K |

133 |

48 |

27 |

1 |

2 |

1 |

2 |

2 |

6+2 |

Y |

Y |

Y |

8 |

Y |

- |

Y |

2,7-6,0 |

0-8 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Atmega128 |

128 |

4K |

4K |

133 |

48 |

27 |

1 |

2 |

1 |

2 |

2 |

6+2 |

Y |

Y |

Y |

8 |

Y |

Y |

Y |

4,0-5,5 |

0-16 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

51

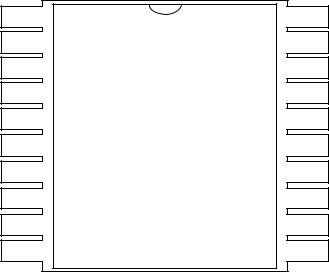

RESET – вхід скидання. Утримання на вході низького рівня протягом двох машинних циклів (якщо працює тактовий генератор), перезапускає мікроконтролер.

XTAL1 – вхід підсилювача генератора і вхід зовнішнього тактового сигналу.

XTAL2 – вихід підсилювача генератора.

PDIP / SOIC

RESET |

1 |

(RXD) PD0 |

2 |

(TXD) PD1 |

3 |

XTAL2 |

4 |

XTAL1 |

5 |

(INT0) PD2 |

6 |

(INT1) PD3 |

7 |

(T0) PD4 |

8 |

(T1) PD5 |

9 |

GND |

10 |

11 |

VCC |

12 |

PB7 (SCK) |

13 |

PB6 (MISO) |

14 |

PB5 (MOSI) |

15 |

PB4 |

16 |

PB3 (OC1) |

17 |

PB2 |

18 |

PB1 (AIN1) |

19 |

PB2 (AIN0) |

20 |

PD6 (ICP) |

Рис. 8. Виводи мікроконтролера AT90S2313.

Система команд мікроконтролера

Таблиця 5

Арифметичні і логічні команди

Мнемо- |

|

Операнд |

Опис команди |

Операція |

Ознаки |

Цикл |

|

ніка |

|

|

|

|

|

|

|

1 |

2 |

|

3 |

4 |

5 |

6 |

|

ADD |

|

Rd,Rr |

Сумування без переносу |

Rd = Rd + Rr |

Z,C,N,V,H,S |

1 |

|

|

|

|

|

|

|

|

|

ADC |

|

Rd,Rr |

Сумування з переносом |

Rd = Rd + Rr + +C |

Z,C,N,V,H,S |

1 |

|

|

|

|

|

|

|

|

|

SUB |

|

Rd,Rr |

Віднімання без переносу |

Rd = Rd - Rr |

Z,C,N,V,H,S |

1 |

|

|

|

|

|

|

|

|

|

SUBI |

|

Rd,K8 |

Віднімання константи |

Rd = Rd - K8 |

Z,C,N,V,H,S |

1 |

|

|

|

|

|

|

|

|

|

SBC |

|

Rd,Rr |

Віднімання з переносом |

Rd = Rd - Rr -C |

Z,C,N,V,H,S |

1 |

|

|

|

|

|

|

|

|

|

SBCI |

|

Rd,K8 |

Віднімання константи з |

Rd = Rd - K8 - -C |

Z,C,N,V,H,S |

1 |

|

|

переносом |

||||||

|

|

|

|

|

|

|

|

AND |

|

Rd,Rr |

Логічне І |

Rd = Rd і Rr |

Z,N,V,S |

1 |

|

|

|

|

|

|

|

|

|

ANDI |

|

Rd,K8 |

Логічне І з константою |

Rd = Rd і K8 |

Z,N,V,S |

1 |

|

|

|

|

|

|

|

|

|

OR |

|

Rd,Rr |

Логічне АБО |

Rd = Rd V Rr |

Z,N,V,S |

1 |

|

|

|

|

|

|

|

|

|

ORI |

|

Rd,K8 |

Логічне АБО з константою |

Rd = Rd V K8 |

Z,N,V,S |

1 |

|

|

|

|

|

|

|

|

|

EOR |

|

Rd,Rr |

Логічне вимикаюче АБО |

Rd = Rd EOR Rr |

Z,N,V,S |

1 |

|

|

|

|

|

|

|

|

|

COM |

|

Rd |

Побітна інверсія |

Rd = $FF - Rd |

Z,C,N,V,S |

1 |

|

52

Продовження табл. 5

1 |

|

2 |

3 |

4 |

5 |

6 |

|||||

NEG |

|

Rd |

Зміна знака (Додатковий |

Rd = $00 - Rd |

Z,C,N,V,H,S |

1 |

|||||

|

код) |

||||||||||

|

|

|

|

|

|

|

|

|

|

||

SBR |

|

Rd,K8 |

Встановити біт (біти) в |

Rd = Rd V K8 |

Z,C,N,V,S |

1 |

|||||

|

регістрі |

||||||||||

|

|

|

|

|

|

|

|

|

|

||

CBR |

|

Rd,K8 |

Скинути біт (біти) в регістрі |

Rd = Rd T ($FF - |

Z,C,N,V,S |

1 |

|||||

|

K8) |

||||||||||

|

|

|

|

|

|

|

|

|

|

||

INC |

|

Rd |

Інкримент значення |

Rd = Rd + 1 |

Z,N,V,S |

1 |

|||||

|

регістра |

||||||||||

|

|

|

|

|

|

|

|

|

|

||

DEC |

|

Rd |

Декремент значення |

Rd = Rd -1 |

Z,N,V,S |

1 |

|||||

|

регістра |

||||||||||

|

|

|

|

|

|

|

|

|

|

||

TST |

|

Rd |

Перевірка на нуль або |

Rd = Rd T Rd |

Z,C,N,V,S |

1 |

|||||

|

від'ємність |

||||||||||

|

|

|

|

|

|

|

|

|

|

||

CLR |

|

Rd |

Обнулити регістр |

Rd = 0 |

Z,C,N,V,S |

1 |

|||||

SER |

|

Rd |

Встановити регістр |

Rd = $FF |

None |

1 |

|||||

ADIW |

|

Rdl,K6 |

Скласти константу і слово |

Rdh:Rdl = |

Z,C,N,V,S |

2 |

|||||

|

Rdh:Rdl + K6 |

||||||||||

|

|

|

|

|

|

|

|

|

|

||

SBIW |

|

Rdl,K6 |

Відняти константу із слова |

Rdh:Rdl = |

Z,C,N,V,S |

2 |

|||||

|

Rdh:Rdl - K 6 |

||||||||||

|

|

|

|

|

|

|

|

|

|

||

MUL |

|

Rd,Rr |

Множення чисел без знака |

R1:R0 = Rd*Rr |

Z,C |

2 |

|||||

|

|

|

|

|

|

|

|

|

|

||

MULS |

|

Rd,Rr |

Множення чисел із знаком |

R1:R0 = Rd*Rr |

Z,C |

2 |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

MULSU |

|

Rd,Rr |

Множення числа із знаком з |

R1:R0 = Rd*Rr |

Z,C |

2 |

|||||

|

числом без знака |

||||||||||

|

|

|

|

|

|

|

|

|

|

||

FMUL |

|

Rd,Rr |

Множення дробових чисел |

R1:R0 = (Rd * Rr) |

Z,C |

2 |

|||||

|

без знака |

<< 1 |

|||||||||

|

|

|

|

|

|

|

|

|

|||

FMULS |

|

Rd,Rr |

Множення дробових чисел |

R1:R0 = (Rd *Rr) |

Z,C |

2 |

|||||

|

із знаком |

<< 1 |

|||||||||

|

|

|

|

|

|

|

|

|

|||

FMULSU |

Rd,Rr |

Множення дробового числа |

R1:R0 = (Rd * Rr) |

Z,C |

2 |

||||||

із знаком з числом без знака |

<< 1 |

||||||||||

|

|

|

|

|

|

|

|

|

|||

RJMP |

|

|

|

|

k |

Відносний перехід |

PC = PC + k +1 |

None |

2 |

||

IJMP |

|

|

|

|

|

|

Непрямий перехід на (Z) |

PC = Z |

None |

2 |

|

|

|

|

|

|

|

|

Команди переходів |

|

|

||

|

|

|

|

|

|

|

|

STACK=PC+1, |

|

|

|

EIJMP |

|

|

|

|

|

|

Розширений непрямий |

PC(15:0) = Z, |

None |

2 |

|

|

|

|

|

|

|

перехід на (Z) |

PC(21:16) = |

||||

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

EIND |

|

|

|

JMP |

|

|

|

|

k |

Перехід |

PC = k |

None |

3 |

||

RCALL |

|

|

|

|

k |

Відносний виклик |

STACK=PC+1, |

None |

3/4* |

||

|

|

|

|

підпрограми |

PC = PC +k + 1 |

||||||

|

|

|

|

|

|

|

|

|

|||

ICALL |

|

|

|

|

|

|

Непрямий виклик (Z) |

STACK=PC+1, |

None |

3/4* |

|

|

|

|

|

|

|

PC = Z |

|||||

|

|

|

|

|

|

|

|

|

|

||

CALL |

|

|

|

|

k |

Виклик підпрограми |

STACK=PC+2, |

None |

4/5* |

||

|

|

|

|

PC = k |

|||||||

|

|

|

|

|

|

|

|

|

|

||

RET |

|

|

|

|

|

|

Повернення з підпрограми |

PC = STACK |

None |

4/5* |

|

RETI |

|

|

|

|

|

|

Повернення з перериванням |

PC = STACK |

I |

4/5* |

|

CPSE |

|

|

Rd,Rr |

Порівняти, пропустити, |

if (Rd ==Rr) PC |

None |

1/2/3 |

||||

|

|

якщо рівні |

= PC 2 or 3 |

||||||||

|

|

|

|

|

|

|

|

|

|||

CP |

|

|

Rd,Rr |

Порівняти |

Rd -Rr |

Z,C,N,V,H,S |

1 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

53

Продовження табл. 5

1 |

|

2 |

3 |

4 |

5 |

6 |

||||||

CPC |

|

|

Rd,Rr |

Порівняти з перенесенням |

Rd - Rr - C |

Z,C,N,V,H,S |

1 |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

CPI |

|

Rd,K8 |

Порівняти з константою |

Rd - K |

Z,C,N,V,H,S |

1 |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

SBRC |

|

|

|

Rr,b |

Пропустити, якщо біт у |

if(Rr(b)=0) |

None |

1/2/3 |

||||

|

|

|

регістрі обнулений |

PC=PC+2 or 3 |

||||||||

|

|

|

|

|

|

|

|

|

|

|

||

SBRS |

|

|

|

Rr,b |

Пропустити, якщо біт у |

if(Rr(b)=1) |

None |

1/2/3 |

||||

|

|

|

регістрі встановлений |

PC=PC+2 or 3 |

||||||||

|

|

|

|

|

|

|

|

|

|

|

||

SBIC |

|

|

|

|

P,b |

Пропустити, якщо біт у |

if(I/O(P,b)=0) |

None |

1/2/3 |

|||

|

|

|

|

порту обнулений |

PC=PC+2 or 3 |

|||||||

|

|

|

|

|

|

|

|

|

|

|

||

SBIS |

|

|

|

|

P,b |

Пропустити, якщо біт у |

if(I/O(P,b)=1) |

None |

1/2/3 |

|||

|

|

|

|

порту встановлений |

PC=PC+2 or 3 |

|||||||

|

|

|

|

|

|

|

|

|

|

|

||

BRBC |

|

|

|

|

s,k |

Перейти, якщо ознака в |

if(SREG(s)=0) |

None |

1/2 |

|||

|

|

|

|

SREG обнулена |

PC = PC+k+ 1 |

|||||||

|

|

|

|

|

|

|

|

|

|

|

||

BRBS |

|

|

|

|

s,k |

Перейти, якщо ознака в |

if(SREG(s)=1) |

None |

1/2 |

|||

|

|

|

|

SREG встановлена |

PC = PC +k+1 |

|||||||

|

|

|

|

|

|

|

|

|

|

|

||

BREQ |

|

|

|

|

k |

Перейти, якщо рівно |

if(Z=1) |

None |

1/2 |

|||

|

|

|

|

PC=PC+ k + 1 |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

BRNE |

|

|

|

|

k |

Перейти, якщо не рівно |

if(Z=0) |

None |

1/2 |

|||

|

|

|

|

PC=PC+k + 1 |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

BRCS |

|

|

|

|

k |

Перейти, якщо перенос |

if(C=1) |

None |

1/2 |

|||

|

|

|

|

встановлений |

PC=P + k + 1 |

|||||||

|

|

|

|

|

|

|

|

|

|

|

||

BRCC |

|

|

|

|

k |

Перейти, якщо перенос |

if(C=0) |

None |

1/2 |

|||

|

|

|

|

обнулений |

PC=PC+ k + 1 |

|||||||

|

|

|

|

|

|

|

|

|

|

|

||

BRSH |

|

|

|

|

k |

Перейти, якщо рівно або |

if(C=0) |

None |

1/2 |

|||

|

|

|

|

більше |

PC=PC+ k + 1 |

|||||||

|

|

|

|

|

|

|

|

|

|

|

||

BRLO |

|

|

|

|

k |

Перейти, якщо менше |

if(C=1) |

None |

1/2 |

|||

|

|

|

|

PC=PC+ k + 1 |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

BRMI |

|

|

|

|

k |

Перейти, якщо мінус |

if(N=1) |

None |

1/2 |

|||

|

|

|

|

PC=PC+ k + 1 |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

BRPL |

|

|

|

|

k |

Перейти, якщо плюс |

if(N=0) |

None |

1/2 |

|||

|

|

|

|

PC=PC+ k + 1 |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

BRGE |

|

|

|

|

k |

Перейти, якщо більше або |

if(S=0) |

None |

1/2 |

|||

|

|

|

|

рівно (зі знаком) |

PC=PC+ k + 1 |

|||||||

|

|

|

|

|

|

|

|

|

|

|

||

BRLT |

|

|

|

|

k |

Перейти, якщо менше (зі |

if(S=1) |

None |

1/2 |

|||

|

|

|

|

знаком) |

PC=PC+ k + 1 |

|||||||

|

|

|

|

|

|

|

|

|

|

|

||

BRHS |

|

|

|

|

k |

Перейти, якщо ознака внут- |

if(H=1) |

None |

1/2 |

|||

|

|

|

|

рішнього переносу встановл. |

PC=PC+ k + 1 |

|||||||

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

Перейти, якщо ознака внут- |

if(H=0) |

|

|

BRHC |

|

|

|

|

k |

рішнього переносу |

None |

1/2 |

||||

|

|

|

|

PC=PC+ k + 1 |

||||||||

|

|

|

|

|

|

|

|

|

обнулена |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

BRTS |

|

|

|

|

k |

Перейти, якщо ознака T |

if(T=1) |

None |

1/2 |

|||

|

|

|

|

встановлена |

PC=PC+ k + 1 |

|||||||

|

|

|

|

|

|

|

|

|

|

|

||

BRTC |

|

|

|

|

k |

Перейти, якщо ознака T |

if(T=0) |

None |

1/2 |

|||

|

|

|

|

обнулена |

PC=PC+ k + 1 |

|||||||

|

|

|

|

|

|

|

|

|

|

|

||

BRVS |

|

|

|

|

k |

Перейти, якщо ознака |

if(V=1) |

None |

1/2 |

|||

|

|

|

|

переповнення встановлена |

PC=PC+ k + 1 |

|||||||

|

|

|

|

|

|

|

|

|

|

|

||

BRVC |

|

|

|

|

k |

Перейти якщо ознака |

if(V=0) |

None |

1/2 |

|||

|

|

|

|

переповнення обнулена |

PC=PC+ k + 1 |

|||||||

|

|

|

|

|

|

|

|

|

|

|

||

54

Продовження табл. 5

1 |

2 |

3 |

4 |

5 |

6 |

|

BRIE |

k |

Перейти якщо переривання |

if(I=1) |

None |

1/2 |

|

дозволені |

PC=PC+ k + 1 |

|||||

|

|

|

|

|||

BRID |

k |

Перейти якщо переривання |

if(I=0) |

None |

1/2 |

|

заборонені |

PC=PC+ k + 1 |

|||||

|

|

|

|

Для операцій доступу до даних, кількість циклів вказана за умови доступу до внутрішньої пам’яті даних і некоректна в роботі із зовнішнім ОЗП. Для команд CALL, ICALL, EICALL, RCALL, RET і RETI необхідно додати три цикли плюс по два цикли для кожного чекання в контролерах з PC меншим 16

біт (128 кбайт пам’яті програм). Для пристроїв із пам’яттю програм більше 128

кбайт додати п’ять циклів і плюс по три цикли на кожне чекання.

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Таблиця 6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Команди передачі даних |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Мнемо- |

Операнд |

Опис команди |

Операція |

Ознаки |

|

Цикл |

|||||||||||

ніка |

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

2 |

|

3 |

4 |

5 |

|

6 |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

MOV |

|

|

|

Rd,Rr |

Копіювати регістр |

Rd = Rr |

None |

|

1 |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Rd+1:Rd = |

|

|

|

MOVW |

|

|

|

Rd,Rr |

Копіювати пару регістрів |

Rr+1:Rr, r,d |

None |

|

1 |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

even |

|

|

|

LDI |

|

|

Rd,K8 |

Завантажити константу |

Rd = K |

None |

|

1 |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

LDS |

|

|

|

|

|

Rd,k |

Пряме завантаження |

Rd = (k) |

None |

|

2* |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

LD |

|

|

|

|

Rd,X |

Непряме завантаження |

Rd = (X) |

None |

|

2* |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

LD |

|

|

Rd,X+ |

Непряме завантаження з |

Rd = (X), |

None |

|

2* |

|||||||||

|

|

постінкрементом |

X=X+1 |

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

LD |

|

|

|

|

Rd,Y |

Непряме завантаження |

Rd = (Y) |

None |

|

2* |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

LD |

|

|

Rd,Y+ |

Непряме завантаження з |

Rd = (Y), |

None |

|

2* |

|||||||||

|

|

постінкрементом |

Y=Y+1 |

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

LD |

|

|

Rd,-Y |

Непряме завантаження з |

Y=Y-1, |

None |

|

2* |

|||||||||

|

|

предекрементом |

Rd = (Y) |

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

LDD |

|

Rd,Y+q |

Непряме завантаження із |

Rd = (Y+q) |

None |

|

2* |

||||||||||

|

заміщенням |

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

LD |

|

|

|

|

Rd,Z |

Непряме завантаження |

Rd = (Z) |

None |

|

2* |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

LD |

|

|

Rd,Z+ |

Непряме завантаження з |

Rd = (Z), |

None |

|

2* |

|||||||||

|

|

постінкрементом |

Z=Z+1 |

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

LD |

|

|

|

Rd,-Z |

Непряме завантаження з |

Z=Z-1, |

None |

|

2* |

||||||||

|

|

|

предекрементом |

Rd = (Z) |

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

LDD |

|

Rd,Z+q |

Непряме завантаження із |

Rd = (Z+q) |

None |

|

2* |

||||||||||

|

заміщенням |

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

55

Продовження табл. 6

1 |

2 |

|

3 |

4 |

5 |

6 |

|||||||||||

STS |

|

|

|

|

|

k,Rr |

Пряме збереження |

(k) = Rr |

None |

2* |

|||||||

ST |

|

|

|

|

X,Rr |

Непряме збереження |

(X) = Rr |

None |

2* |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ST |

|

|

X+,Rr |

Непряме збереження з |

(X) = Rr, X=X+1 |

None |

2* |

||||||||||

|

|

постінкрементом |

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ST |

|

|

|

-X,Rr |

Непряме збереження з |

X=X-1, (X)=Rr |

None |

2* |

|||||||||

|

|

|

предекрементом |

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ST |

|

|

|

|

Y,Rr |

Непряме збереження |

(Y) = Rr |

None |

2* |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ST |

|

|

Y+,Rr |

Непряме збереження з |

(Y) = Rr, Y=Y+1 |

None |

2 |

||||||||||

|

|

постінкрементом |

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ST |

|

|

|

-Y,Rr |

Непряме збереження з |

Y=Y-1, |

None |

2 |

|||||||||

|

|

|

предекрементом |

(Y) = Rr |

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

ST |

|

Y+q,Rr |

Непряме збереження із |

(Y+q) = Rr |

None |

2 |

|||||||||||

|

заміщенням |

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ST |

|

|

|

|

|

Z,Rr |

Непряме збереження |

(Z) = Rr |

None |

2 |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ST |

|

|

|

Z+,Rr |

Непряме збереження з |

(Z) = Rr, Z=Z+1 |

None |

2 |

|||||||||

|

|

|

постінкрементом |

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ST |

|

|

|

-Z,Rr |

Непряме збереження з |

Z=Z-1, |

None |

2 |

|||||||||

|

|

|

предекрементом |

(Z) = Rr |

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

ST |

|

Z+q,Rr |

Непряме збереження із |

(Z+q) = Rr |

None |

2 |

|||||||||||

|

заміщенням |

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

LPM |

|

|

|

|

|

|

|

|

|

|

|

|

|

Завантаження з програмної |

R0 = (Z) |

None |

3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

пам’яті |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

LPM |

|

|

|

|

Rd,Z |

Завантаження з програмної |

Rd = (Z) |

None |

3 |

||||||||

|

|

|

|

пам’яті |

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

LPM |

|

|

Rd,Z+ |

Завантаження з програмної |

Rd = (Z), Z=Z+1 |

None |

3 |

||||||||||

|

|

пам’яті з постінкрементом |

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ELPM |

|

|

|

|

|

|

Нет |

Розширене завантаження з |

R0 = (RAMPZ:Z) |

None |

3 |

||||||

|

|

|

|

|

|

програмної пам’яті |

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ELPM |

|

|

|

|

Rd,Z |

Розширене завантаження з |

Rd = (RAMPZ:Z) |

None |

3 |

||||||||

|

|

|

|

програмної пам’яті |

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Розширене завантаження з |

Rd = (RAMPZ:Z), |

|

|

ELPM |

|

|

Rd,Z+ |

програмної пам’яті з |

None |

3 |

|||||||||||

|

|

Z = Z+1 |

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

постінкрементом |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SPM |

|

|

|

|

|

|

|

|

|

|

|

|

|

Збереження в програмній |

(Z) = R1:R0 |

None |

- |

|

|

|

|

|

|

|

|

|

|

|

|

|

пам’яті |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ESPM |

|

|

|

|

|

|

|

|

|

|

|

|

|

Розширене збереження в |

(RAMPZ:Z) = |

None |

- |

|

|

|

|

|

|

|

|

|

|

|

|

|

програмній пам’яті |

R1:R0 |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

IN |

|

|

|

|

Rd,P |

Читання порта |

Rd = P |

None |

1 |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

||||||

OUT |

|

|

|

|

|

P,Rr |

Запис у порт |

P = Rr |

None |

1 |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

PUSH |

|

|

|

|

|

|

Rr |

Занесення регістра в стек |

STACK = Rr |

None |

2 |

||||||

POP |

|

|

|

|

|

|

Rd |

Зчитування регістра зі стеку |

Rd = STACK |

None |

2 |

||||||

LPM |

|

|

Rd,Z+ |

Завантаження з програмної |

Rd = (Z), Z=Z+1 |

None |

3 |

||||||||||

|

|

пам’яті з постінкрементом |

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ELPM |

|

|

|

|

|

|

Нет |

Розширене завантаження з |

R0 = (RAMPZ:Z) |

None |

3 |

||||||

|

|

|

|

|

|

програмної пам’яті |

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ELPM |

|

|

|

|

Rd,Z |

Розширене завантаження із |

Rd = (RAMPZ:Z) |

None |

3 |

||||||||

|

|

|

|

програмної пам'яті |

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

56

Продовження табл. 6

1 |

|

2 |

3 |

4 |

5 |

6 |

||||

|

|

|

|

|

|

|

Розширене завантаження із |

Rd = (RAMPZ:Z), |

|

|

ELPM |

|

Rd,Z+ |

програмної пам'яті з |

None |

3 |

|||||

|

Z = Z+1 |

|||||||||

|

|

|

|

|

|

|

постінкриментом |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SPM |

|

|

|

|

|

|

Збереження в програмній |

(Z) = R1:R0 |

None |

- |

|

|

|

|

|

|

пам’яті |

||||

|

|

|

|

|

|

|

|

|

|

|

ESPM |

|

|

|

|

|

|

Розширене збереження в |

(RAMPZ:Z) = |

None |

- |

|

|

|

|

|

|

програмній пам’яті |

R1:R0 |

|||

|

|

|

|

|

|

|

|

|

||

IN |

|

|

Rd,P |

Читання порта |

Rd = P |

None |

1 |

|||

|

|

|

|

|

|

|

|

|

||

OUT |

|

|

P,Rr |

Запис в порт |

P = Rr |

None |

1 |

|||

|

|

|

|

|

|

|

|

|

||

PUSH |

|

|

Rr |

Занесення регістра в стек |

STACK = Rr |

None |

2 |

|||

POP |

|

|

Rd |

Зчитування регістра з стеку |

Rd = STACK |

None |

2 |

|||

Для операцій доступу до даних кількість циклів вказана за умови доступу до внутрішньої пам’яті даних, і некоректна в роботі із зовнішнім ОЗП. Для команд LD, ST, LDD, STD, LDS, STS, PUSH і POP необхідно додати один цикл плюс по одному циклу для кожного чекання.

Таблиця 7

Команди роботи з бітами

Мнемо |

Опер |

Опис команди |

Операція |

Ознаки |

Цикл |

|||||

ніка |

|

|

анд |

|||||||

|

|

|

|

|

|

|||||

LSL |

|

|

|

Rd |

Логічний зсув вліво |

Rd(n+1)=Rd(n), |

Z,C,N,V, |

1 |

||

|

|

|

Rd(0)=0, C=Rd(7) |

H,S |

||||||

|

|

|

|

|

|

|

|

|

||

LSR |

|

|

|

Rd |

Логічний зсув вправо |

Rd(n)=Rd(n+1), |

Z,C,N,V, |

1 |

||

|

|

|

Rd(7)=0, C=Rd(0) |

S |

||||||

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

Rd(0)=C, |

Z,C,N,V, |

|

ROL |

|

|

|

Rd |

Циклічний зсув вліво через C |

Rd(n+1)=Rd(n), |

1 |

|||

|

|

|

H,S |

|||||||

|

|

|

|

|

|

|

|

C=Rd(7) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Rd(7)=C, |

Z,C,N,V, |

|

ROR |

|

|

|

Rd |

Циклічний зсув вправо через C |

Rd(n)=Rd(n+1), |

1 |

|||

|

|

|

S |

|||||||

|

|

|

|

|

|

|

|

C=Rd(0) |

|

|

|

|

|

|

|

|

|

|

|

|

|

ASR |

|

|

|

Rd |

Арифметичний зсув вправо |

Rd(n)=Rd(n+1), |

Z,C,N,V, |

1 |

||

|

|

|

n=0,...,6 |

S |

||||||

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

Rd(3..0) = |

|

|

SWAP |

|

|

|

Rd |

Перестановка тетрад |

Rd(7..4), Rd(7..4) |

None |

1 |

||

|

|

|

|

|

|

|

|

= Rd(3..0) |

|

|

BSET |

|

|

|

s |

Встановлення ознаки |

SREG(s) = 1 |

SREG(s) |

1 |

||

BCLR |

|

|

|

s |

Обнулення ознаки |

SREG(s) = 0 |

SREG(s) |

1 |

||

SBI |

|

|

|

P,b |

Встановлення біт в порту |

I/O(P,b) = 1 |

None |

2 |

||

|

|

|

|

|

|

|

|

|

|

|

CBI |

|

|

|

P,b |

Обнулити біт в порту |

I/O(P,b) = 0 |

None |

2 |

||

|

|

|

|

|

|

|

|

|

|

|

BST |

|

|

Rr,b |

Зберегти біт із регістра в T |

T = Rr(b) |

T |

1 |

|||

|

|

|

|

|

|

|

|

|

||

BLD |

|

Rd,b |

Зберегти біт із T в регістрі |

Rd(b) = T |

None |

1 |

||||

|

|

|

|

|

|

|

|

|

|

|

SEC |

|

|

|

|

|

|

Встановити ознаку переносу |

C =1 |

C |

1 |

CLC |

|

|

|

|

|

|

Обнулити ознаку переносу |

C = 0 |

C |

1 |

57

Продовження табл. 7

1 |

2 |

3 |

4 |

5 |

6 |

SEN |

|

Встановити ознаку від’ємного числа |

N = 1 |

N |

1 |

CLN |

|

Обнулити ознаку від’ємного числа |

N = 0 |

N |

1 |

SEZ |

|

Встановити ознаку нуля |

Z = 1 |

Z |

1 |

CLZ |

|

Обнулити ознаку нуля |

Z = 0 |

Z |

1 |

SEI |

|

Встановити ознаку переривання |

I = 1 |

I |

1 |

CLI |

|

Обнулити ознаку переривання |

I = 0 |

I |

1 |

SES |

|

Встановити ознаку числа зі знаком |

S = 1 |

S |

1 |

CLN |

|

Обнулити ознаку числа зі знаком |

S = 0 |

S |

1 |

SEV |

|

Встановити ознаку переповнення |

V = 1 |

V |

1 |

CLV |

|

Обнулити ознаку переповнення |

V = 0 |

V |

1 |

SET |

|

Встановити ознаку T |

T = 1 |

T |

1 |

CLT |

|

Обнулити ознаку T |

T = 0 |

T |

1 |

SEH |

|

Встановити ознаку внутрішнього |

H = 1 |

H |

1 |

|

переносу |

||||

|

|

|

|

|

|

CLH |

|

Обнулити ознаку внутрішнього |

H = 0 |

H |

1 |

|

переносу |

||||

|

|

|

|

|

|

NOP |

|

Немає операції |

|

None |

1 |

SLEE |

|

Зменшення енергоспоживання |

|

None |

1 |

P |

|

|

|||

|

|

|

|

|

|

WDR |

|

Скидання сторожевого таймера |

|

None |

1 |

Операнди мають наступне призначення:

Rd: Результуючий (і вихідний) регістр у регістровому файлі; Rr: Вихідний регістр у регістровому файлі;

b: Константа (3 біта), може бути константний вираз; s: Константа (3 біта), може бути константний вираз; P: Константа (5-6 біт), може бути константний вираз; K6: Константа (6 біт), може бути константний вираз; K8: Константа (8 біт), може бути константний вираз;

k: Константа (розмір залежить від команди), може бути константний вираз; q: Константа (6 біт), може бути константний вираз;

Rdl:= R24, R26, R28, R30.

Для команд ADIW і SBIW X,Y,Z – регістри непрямої адресації (X =

R27:R26, Y = R29:R28, Z = R31:R30)

Порядок виконання роботи

1. Ознайомитись із системою команд мікроконтролера фірми ATMEL.

58

2.Завантажити програмну оболонку емулятора мікроконтролера.

3.Ввести по порядку команди різного призначення і ознайомитись з результатами їхньої дії, стану регістрів, ознак тощо.

4.Завершити роботу емулятора.

Зміст звіту:

1.Тема, мета, обладнання і матеріали для лабораторної роботи.

2.Система команд мікроконтролера фірми ATMEL.

3.Перелік команд, які виконувались емулятором, результати їх виконання (значення регістрів, пам’яті, регістра ознак, портів тощо).

4.Висновки.

Питання для самоконтролю

7.Як групуються команди процесора ?

8.Охарактеризуйте виконання команд процесора.

9.Що таке цикл виконання команди ?

10.Що таке такт виконання команди ?

11.Поясніть принцип роботи наведених часових діаграм виконання команд процесора.

12.Поясніть функціональне призначення шин процесора.

Бібліографічний список

8. Бучма І.М. Мікропроцесорні пристрої: Навчальний посібник. – Львів:

Видавництво Національного університету “Львівська політехніка“, 2005. – 306 с.

9.Джордейн Р. Справочник программиста персональных компьютеров типа IBM PC, XT, AT: Пер. с англ./Предисл. Н. В. Гайского. –М.: Финансы и статистика, 1992. – 544 c. ил.

10.Преснухин и др. Расчет элементов цифровых устройств: Учеб.

Пособие/ Л.Н. Преснухин, Н.В. Воробьев, А.А. Шишкевич; Под ред. Л. Н.

Преснухина. – 2-е изд., перераб. и доп. – М.: Высш. шк., 1991. – 526 с.: ил.

59

11. Зубчик В. И. и др. Справочник по цифровой схемотехники / В. И.

Зубчик, В. П. Сигорский, А. Н. Шкуро. – К.: Техника, 1990. 448 с.

12. Лю Ю-Чжен, Гибсон Г. Микропроцессоры семейства 8086/8088. –

М.:Радио и связь, 1987. 512 с.

13. Гивоке Д., Россер Р. Микропроцессоры и микрокомпьютеры – М.:

Мир, 1983.– 464с.

14. Бойко В.И., Гуржий А. Н., Жуйков В.Я. и др. Схемотехника электронных систем. Микропроцессоры и микроконтроллеры. СПб.: БХВ-

Петербург, 2004. –464 с.

60