МК

.pdf

ЛАБОРАТОРНА РОБОТА №3

ВИВЧЕННЯ СИСТЕМИ КОМАНД ОДНОКРИСТАЛЬНОЇ МІКРО-ЕОМ

Мета роботи: ознайомлення із системою команд однокристальної мікро-ЕОМ типу К1816ВЕ-48 (МК51), особливістю виконання команд, оволодіння роботою емулятора процесора.

Обладнання, прилади та інструменти: ПЕОМ, система команд одно-

кристальної мікро-ЕОМ типу К1816ВЕ-48 (МК51), програма-емулятор роботи мікро-ЕОМ, інструкція користувача.

Загальні відомості

МК51 – це серія з ядром 80С51. У країнах СНД МК51 випускаються на базі n-МОП технології (серія 1816) і КМОП технології (серія 1830).

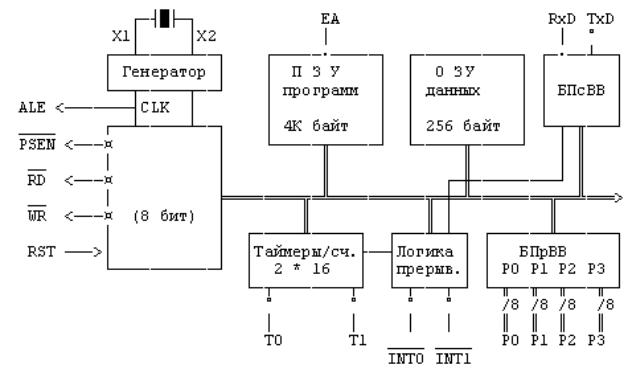

Структура МК51 (рис. 5)

У МК51 використовуються наступні сигнали: ALE – строб адреси; PSEN\ –

строб читання зовнішньої пам'яті програм; RD\,WR\– строби читання і запису

ПЗП |

|

ОЗПр |

програм |

|

даних |

|

|

|

|

|

|

процесор

|

|

Логіка |

Таймер/Лч |

|

|

2*16 |

|

перерив. |

|

|

|

|

|

|

Рис. 5. Структурна схема МК51.

31

зовнішньої пам'яті даних; ЕА\ – дозвіл обігу у внутрішню пам'ять програм;

Т0,Т1 – входи лічильників зовнішніх подій; INT0, JNT1– запити зовнішніх радіальних переривань; RxD – вхід даних послідовного каналу; TxD – вихід даних послідовного каналу.

До складу МК51 входять паралельні 8-розрядні квазідвонаправлені порти

P0…P3. Порт Р3 може використовуватись для введення і виведення управляючих сигналів.

Таким чином, у циклах звернення до зовнішніх ресурсів на лініях порту Р3 працюють управляючі сигнали, а за відсутності необхідності управління зовнішніми ресурсами ці ж лінії можуть бути використані як лінії порту.

Архітектурні особливості МК51

МК51 дозволяє управляти п'ятьма (частково пересічними) адресними областями пам'яті, чотири з яких є областями даних:

RSEG – облясть регістрів (4*8 байт);

DSEG – область внутрішньої пам'яті даних (256 байт);

BSEG – бітова область даних (256 біт);

XSEG – область зовнішньої пам'яті даних (до 64 К байт);

CSEG – область програмного коду (до 64 К байт).

Області RSEG і BSEG частково перетинаються, фізично поєднуються з

DSEG і утворюють єдине внутрішнє середовище для зберігання даних. Це дозволяє одні й ті самі дані розглядати з різних позицій (елемент пам'яті,

регістр, бітове поле, порт уведення-виведення тощо) і організовувати найзручніший для кожного випадку доступ до них.

Характерно, що всі порти уведення-виведення, системні регістри,

таймери також відображені на простір DSEG.

Область регістрів представлено чотирма банками регістрів по 8 в

кожному, а також 16-розрядним програмним лічильником PC і регістром непрямої адреси DPTR, 8-розрядними акумуляторами А і В, покажчиком стека

SP і регістром PSW.

32

Усі регістри, окрім PC, відображаються на DSEG. PSW|7] – СY – перенесення із старшого (7) розряду АЛБ;

PSW[6] – АС – перенесення з третього розряду АЛБ;

PSW[5] – F0 – ознака користувача.

Крім того, формат PSW охоплює двобітове поле PSW[4:3] – RS номера банку регістрів й ознаки арифметичного переповнювання OV (PSW[2]) і

парності Р (PSW[0]).

Ознаки СY, АС і OV відображають ознаки результату останньої ариф-

метичної операції, а Р – парність вмісту акумулятора А. Розширення акумулятора А використовується в командах множення і ділення, в решти операцій – як звичайний елемент пам'яті. Програмний лічильник адресує простір пам'яті програм CSEG обсягом до 64 Кбайт. Перехід з області внутрішньої пам'яті програм до зовнішньої здійснюється автоматично.

Покажчик даних DPTR використовується для звернення до XSEG і під час пересилання констант з CSEG до А. Крім того, вміст DPTR використову-

ється як зсув у команді переходу. Покажчик стека SP утворює системний стек глибиною до 256 байт; SP береже адресу останнього занесеного байта і росте у разі запису у бік великих адрес. Регістри R0, R1 кожного банку використовуються як покажчики даних. У разі скидання машини в А, В, PC і DPTR завантажуються 0h, а в SP – 07h.

Організація внутрішньої пам'яті даних

Простір DSEG охоплює 256 елементів пам'яті, частина з яких є одночасно елементами інших просторів (рис. 6). Зокрема, перші 32 байти ОЗП займають 4

банки. Службові регістри, порти введення-виведення, таймери, акумулятори тощо так само суміщені з елементами пам'яті і полями бітового сегмента. Це дає змогу звернутися до одного фізичного об'єкта різними способами. Так, до осередку DSEG[E0] можна звернутися за прямою і непрямою адресою,

звернутися як до акумулятора А і як до поля BSEG [E0..E7] (до кожного біта окремо).

33

|

0 1 2 |

3 |

... 7 |

8 |

9 |

А В C D.. |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

8 |

Р0 |

SР |

DPTL |

DPTH |

|

PCОМ |

ТСON |

THOD |

TOL |

ТОН |

TIL |

T1H |

|

|

|

|

|

|

|

|

|

|

|

|

|

9 |

Р1 |

|

|

|

|

|

SCOM |

SBUF |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

А |

Р2 |

|

|

|

|

|

IE |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

В |

РЗ |

|

|

|

|

|

IP |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

С |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D |

Р51 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

E |

А |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

F |

В |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис. 6. Область внутрішньої пам'яті даних DSEG.

Пам'ять програм адресується РС[15:0] і може складати до 64 Кбайт,

причому молодші 4 К можуть розташовуватися безпосередньо на кристалі, а

решта пам'яті – зовнішнє ЗПр. З погляду програміста зовнішня і внутрішня пам'ять програм складає єдиний адресний простір. Є "особливі крапки"

CSEG:

RESET 0000h – стартова адреса;

EXTIO 0003h – зовнішнє переривання 0;

TIMERO 000Bh – переривання від таймера/лічильника ТО;

ЕХТІ1 0013h – зовнішнє переривання 1;

TIMER1 00lBh – переривання від таймера/лічильника Т1;

SINT 0023h – переривання послідовного порту;

Машинні цикли і синхронізація мікро-ЕОМ

Живлення МК51 здійснюється від одного джерела +5В. Кварцовий резонатор 3,5…12 МГц під’єднується до виводів X1, Х2; можливе під’єднання зовнішнього тактового генератора через X1.

OSC/2 – основна внутрішня тактова частота CLK. Перша половина періоду

CLK фаза Р1, друга – Р2. Кожний машинний цикл складається з шести періодів

CLK: станів S1, S2… S6 або дванадцяти періодів OSC, званих фазами S1P1,

34

S1P2, S2P1 … S6P, S6P2. Кожний машинний цикл супроводжується генерацією двох стробів ALE тривалістю в один період CLK - S1P2…S2P1, S4P2… S5P1.

Командний цикл (КЦ) містить один або декілька машинних циклів (МЦ) і

відлічується від S1P1. За фазою S1P2 в IR фіксується код операції, другий байт двобайтової команди читається в S4P2 того самого МЦ, третій байт трибайтової

– в S1Р2 наступного МЦ. Таким чином, для введення кожного байта команди потрібен один напівцикл.

Під час усіх напівциклів, що залишилися, у фазах S1P2 і S4P2 читається код операції наступної розміщеної в пам'яті команди, проте він не поміщається в IR і не інкримінується PC. Поточний КЦ завжди завершується в S6P2. Услід за цим починається S1, в якому в IR вводиться новий байт.

Звернення до зовнішньої пам'яті даних XSEG за командою MOVX вимагає другого МЦ, в якому не виробляється перший строб ALE.

Для приведення МК51 в початковий стан необхідно подати на вхід RST

імпульс Н-рівня тривалістю не менше 24 періодів OSC (два МЦ) за умови, що генератор запущений.

Зовнішні пристрої МК51

До "зовнішніх" пристроїв МК51 віднесемо:

•4 паралельні двонаправлені порти уведення-виведення P0...P3;

•буфер SBUF і регістр управління SCON послідовного каналу;

•таймери/лічильники Т0, Т1, їх регістр управління TCON і регістр режимів

TMOD;

•регістри управління підсистемою переривань: регістр пріоритетів IP і

регістр маски IE;

•регістр управління машиною PCON.

До складу МК51 входить дуплексний послідовний канал зв'язку з буферизацією, який може бути запрограмований для роботи в одному з чотирьох режимів:

• режим "0" – синхронне уведення-виведення з частотою OSC/12;

35

•режим "1" – асинхронний з 8-біт. кадром, частота k*f;

•режим "2" – асинхронний з 9-біт. кадром, частота k*OSC/32;

•режим "3" – асинхронний з 9-біт. кадром, частота k*f; де до {1, 1/2}, f –

частота переповнювання Tl (FOV), ділена на 16.

Підсистема переривань МК51

Архітектура МК51 підтримує дворівневу радіальну пріоритетну підсистему переривань (ПП) з шістьма джерелами запитів.

Для прийому зовнішніх переривань слугують входи INT0\, INT1\.

Джерелами внутрішніх запитів можуть слугувати сигнали переповнення таймерів ТО, Т1 і сигнал завершення роботи послідовного каналу.

Система команд МК51

Система команд охоплює 111 команд – однобайтових (49), двобайтових

(45) і трибайтових (17). Усі команди виконуються за 1 або 2 МЦ (16 тактів CLK

у кожному), за винятком команд множення і розподілу MUL і DIV, для виконання яких необхідно 4 МЦ. Більшість двобайтових команд – одноциклові,

а всі трибайтові – двоциклові. За один МЦ в МК51 можна вводити до двох байтів програмного коду.

МК51 працює з даними чотирьох основних типів – бітами, півбайтами (4

біти), байтами і адресами (16 бітів). Одиницею даних, що часто використо-

вується, є байт: внутрішні магістралі даних мають 8-бітовий розмір. Програмна пам'ять, внутрішня пам'ять і зовнішня пам'ять даних запам'ятовують і повертають дані у вигляді байтів. Окрім того, є багато команд, які працюють з одиничними бітами. Біт може бути встановлений, вирахований,

проінвертований, логічно скомбінований з ознакою перенесення і перевірений для виконання подальших переходів. Півбайт (двійково-десяткова упакована цифра) зазвичай рідко застосовується в МК51, але двійково-десяткова арифметика може виконуватися без перетворення операндів у двійкове уявлення.

36

Команди, які використовують 16-бітові адреси, стосуються даних (16-

бітовий регістр DPTR) і з програмним лічильником (переходи і виклики підпрограми). Використання команд складання з бітом переносу (ADDC) і

віднімання із займанням (SUBB) робить програмування 16-бітової арифметики відносно простим.

Програмно-доступними об'єктами у складі ОМЕВМ є: апаратні регістри,

чотири банки по вісім регістрів R0...R7,R0...R7 і 128 елементів внутрішньої пам'яті даних – з адресами 00H...7FH. Крім того, за спеціальними командами

MOVX і MOVC може бути доступна зовнішня пам'ять даних і програм. У МК51

можлива бітова адресація апаратних регістрів і частини внутрішньої пам'яті.

У програмуванні слід мати на увазі, що як регістри R0...R7 банку 0

використовуються елементи внутрішньої пам'яті даних з адресами 00Н...07Н,

банку 1 – 08H...0FH, банку 2 – 1 ВІН... 17Н, банку 3 – 18H...1FH.

У системі команд МК51 використовуються регістрова, пряма, непряма і безпосередня адресація.

За регістрової адресації операнди знаходяться в регістрах, імена яких визначаються кодом операції команди. Ця адресація використовується для звернення до регістрів вибраного банку робочих регістрів, до регістрів А, В,

DPTR і до прапора перенесення С.

За прямою адресою можна звертатися до апаратних регістрів і внутрішньої пам'яті. Використовується також пряма бітова адресація.

Побічно можна адресуватися до елементів внутрішньої і зовнішньої пам'яті даних через регістри R0,R1 поточного банку.

До будь-якого елемента зовнішньої пам'яті (даних і програм) можна звернутися з використанням регістра DPTR.

За типом операцій можна виділити наступні класи команд: пересилки;

арифметичні і логічні; передачі управління; спеціальні команди.

Система команд мікроконтролера К1816ВЕ51

37

|

|

|

|

|

|

Таблиця 2 |

Команди передачі даних |

|

|

|

|

||

|

|

|

|

|

|

|

Команда |

Мнемокод |

КОП |

Т |

Б |

Ц |

Операція |

|

|

|

|

|

|

|

1 |

2 |

3 |

4 |

5 |

6 |

7 |

Пересилання в акумулятор |

MOV A,Rn |

11101rrr |

1 |

1 |

1 |

(A)<-(Rn) |

із регістра (n = 0…7) |

|

|

|

|

|

|

Пересилання в акумулятор |

MOV A,ad |

11100101 |

3 |

2 |

1 |

(A)<-(ad) |

прямоадресуюого байта |

|

|

|

|

|

|

Пересилання в акумулятор |

MOV A,@Ri |

1110011i |

1 |

1 |

1 |

(A)<-((Ri)) |

байта з РПД (i=0;1) |

|

|

|

|

|

|

Завантаження в акумулятор |

MOV A,#d |

01110100 |

2 |

2 |

1 |

(A)<-#d |

константи |

|

|

|

|

|

|

Пересилання в регістр із |

MOV Rn,A |

11111rrr |

1 |

1 |

1 |

(Rn)<-(A) |

акумулятора |

|

|

|

|

|

|

Пересилання в регістр |

MOV Rn,ad |

10101rrr |

3 |

2 |

2 |

(Rn)<-(ad) |

прямоадресуючого байта |

|

|

|

|

|

|

Завантаження в регістр |

MOV Rn,#d |

01111rrr |

2 |

2 |

1 |

(Rn)<-#d |

константи |

|

|

|

|

|

|

Пересилання за прямою |

MOV ad,A |

11110101 |

3 |

2 |

1 |

(ad)<-(A) |

адресою акумулятора |

|

|

|

|

|

|

Пересилання за прямою |

MOV ad,Rn |

10001rrr |

3 |

2 |

2 |

(ad)<-(Rn) |

адресою регістра |

|

|

|

|

|

|

Пересилання |

MOV add,ads |

10000101 |

9 |

3 |

2 |

(add)<-(ads) |

прямоадресуючого байта за |

|

|

|

|

|

|

прямою адресою |

|

|

|

|

|

|

Пересилання байта із РПД за |

MOV ad,@Ri |

1000011i |

3 |

2 |

2 |

(ad)<-((Ri)) |

прямою адресою |

|

|

|

|

|

|

Пересилання за прямою |

MOV ad,#d |

01110101 |

7 |

3 |

2 |

(ad)<-#d |

адресою константи |

|

|

|

|

|

|

Пересилання в РПД з |

MOV @Ri,A |

1111011i |

1 |

1 |

1 |

((Ri))<-(A) |

акумулятора |

|

|

|

|

|

|

Пересилання в РПД прямо- |

MOV @Ri,ad |

0110011i |

3 |

2 |

2 |

((Ri))<-(ad) |

адресуючого байта |

|

|

|

|

|

|

Пересилання в РПД |

MOV @Ri,#d |

0111011i |

2 |

2 |

1 |

((Ri))<-#d |

константи |

|

|

|

|

|

|

Завантаження покажчика |

MOV |

10010000 |

1 |

3 |

2 |

(DPTR)<-#d16 |

даних |

DPTR,#d16 |

|

3 |

|

|

|

Пересилання в акумулятор |

MOVC |

10010011 |

1 |

1 |

2 |

(A)<-((A)+ |

байта із ПП |

A,@A+DPTR |

|

|

|

|

+(DPTR)) |

|

|

|

|

|

|

|

Пересилання в акумулятор |

MOVC |

10000011 |

1 |

1 |

2 |

(PC)<-(PC)+1 |

байта із ПП |

A,@A+PC |

|

|

|

|

(A)<-((A)+(PC)) |

38

Продовження табл. 2

1 |

2 |

3 |

4 |

5 |

6 |

7 |

Пересиляння в акумулятор |

MOVX |

1110001i |

1 |

1 |

2 |

(A)<-(Ri) |

байта із ВПД |

A,@Ri |

|

|

|

|

|

Пересилання в акумулятор |

MOVX |

11100000 |

1 |

1 |

2 |

(A)<-((DPTR)) |

байта з розширеної ЗПД |

A,@DPTR |

|

|

|

|

|

|

|

|

|

|

|

|

Пересилання в ЗПД з |

MOVX |

1111001i |

1 |

1 |

2 |

((Ri))<-(A) |

акумулятора |

@Ri,A |

|

|

|

|

|

Пересилання в розширену |

MOVX |

11110000 |

1 |

1 |

2 |

((DPTR))<-(A) |

ЗПД з акумулятора |

@DPTR,A |

|

|

|

|

|

Завантаження в стек |

PUSH ad |

11000000 |

3 |

2 |

2 |

(SP)<-(SP)+1 |

|

|

|

|

|

|

((SP))<-(ad) |

Вивантаження зі стеку |

POP ad |

11010000 |

3 |

2 |

2 |

(ad)<-(SP) |

|

|

|

|

|

|

(SP)<-(SP)-1 |

Обмін акумулятора з |

XCH A,Rn |

11001rrr |

1 |

1 |

1 |

(A)↔(Rn) |

регістром |

|

|

|

|

|

|

Обмін акумулятора з |

XCH A,ad |

11000101 |

3 |

2 |

1 |

(A)↔(ad) |

прямоадресуючим байтом |

|

|

|

|

|

|

Обмін акумулятора з байтом |

XCH A,@Ri |

1100011i |

1 |

1 |

1 |

(A)↔((Ri)) |

із РПД |

|

|

|

|

|

|

Обмін молодшої тетради |

XCHD |

1101011i |

1 |

1 |

1 |

(A0..3)↔((Ri)0 |

акумулятора з молодшою |

A,@Ri |

|

|

|

|

..3) |

тетрадою байта РПД |

|

|

|

|

|

|

Команди арифметичних операцій |

|

|

|

|||

|

|

|

|

|

|

|

Складання акумулятора з |

ADD A,Rn |

00101rrr |

1 |

1 |

1 |

(A)<-(A)+(Rn) |

регістром (n = 0...7) |

|

|

|

|

|

|

Складання акумулятора з |

ADD A,ad |

00100101 |

3 |

2 |

1 |

(A)<-(A)+(ad) |

прямоадресуючим байтом |

|

|

|

|

|

|

Складання акумулятора з |

ADD |

0010011i |

1 |

1 |

1 |

(A)<- |

байтом із РПД (i = 0,1) |

A,@Ri |

|

|

|

|

(A)+((Ri)) |

Складання акумулятора з |

ADD A,#d |

00100100 |

2 |

2 |

1 |

(A)<-(A)+#d |

константой |

|

|

|

|

|

|

Складання акумулятора з |

ADDC |

00111rrr |

1 |

1 |

1 |

(A)<- |

регістром і переносом |

A,Rn |

|

|

|

|

(A)+(Rn)+(C) |

Складання акумулятора з |

ADDC |

00110101 |

3 |

2 |

1 |

(A)<- |

прямоадресуючим байтом і |

A,ad |

|

|

|

|

(A)+(ad)+(C) |

переносом |

|

|

|

|

|

|

Складання акумулятора з |

ADDC |

0011011i |

1 |

1 |

1 |

(A)<- |

байтом із РПД і переносом |

A,@Ri |

|

|

|

|

(A)+((Ri))+(C) |

Складання акумулятора з |

ADDC |

00110100 |

2 |

2 |

1 |

(A)<- |

константою і переносом |

A,#d |

|

|

|

|

(A)+#d+(C) |

39

Продовження табл. 2

1 |

2 |

3 |

4 |

5 |

6 |

7 |

|

|

|

|

|

|

|

Десяткова корекція |

DA A |

11010100 |

1 |

1 |

1 |

Якщо |

акумулятора |

|

|

|

|

|

(А0..3)>9 V |

|

|

|

|

|

|

((AC)=1), то |

|

|

|

|

|

|

(А0..3)<- |

|

|

|

|

|

|

(А0..3)+6, |

|

|

|

|

|

|

потім якщо |

|

|

|

|

|

|

(A4..7)>9 V |

|

|

|

|

|

|

((С)=1), то |

|

|

|

|

|

|

(A4..7)<- |

|

|

|

|

|

|

(А4..7)+6 |

Віднімання з акумулятора |

SUBB |

10011rrr |

1 |

1 |

1 |

(A)<-(A)-(C)- |

регістра і переносу |

A,Rn |

|

|

|

|

(Rn) |

Віднімання з акумулятора |

SUBB |

10010101 |

3 |

2 |

1 |

(A)<-(A)-(C)- |

прямоадресуючого байта і |

A,ad |

|

|

|

|

(ad)) |

переносу |

|

|

|

|

|

|

Віднімання з акумулятора |

SUBB |

1001011i |

1 |

1 |

1 |

(A)<-(A)-(C)- |

байта РПД і переносу |

A,@Ri |

|

|

|

|

(Ri)) |

Порядок виконання роботи

1.Ознайомитись із системою команд мікроконтролера К1816ВЕ48 (МК51).

2.Завантажити програмну оболонку емулятора мікроконтролера МК51.

3.Ввести по порядку команди різного призначення і ознайомитись з результатами їхньої дії, стану регістрів, ознак тощо.

4.Завершити роботу емулятора.

Зміст звіту

1.Тема, мета, обладнання і матеріали для лабораторної роботи.

2.Система команд мікроконтролера К1816ВЕ48 (МК51).

3.Перелік команд, які виконувались емулятором, результати їх виконання (значення регістрів, пам’яті, регістра ознак, портів тощо).

4.Висновки.

Завдання для самоконтролю

1. Як групуються команди процесора ?

40