МК

.pdf

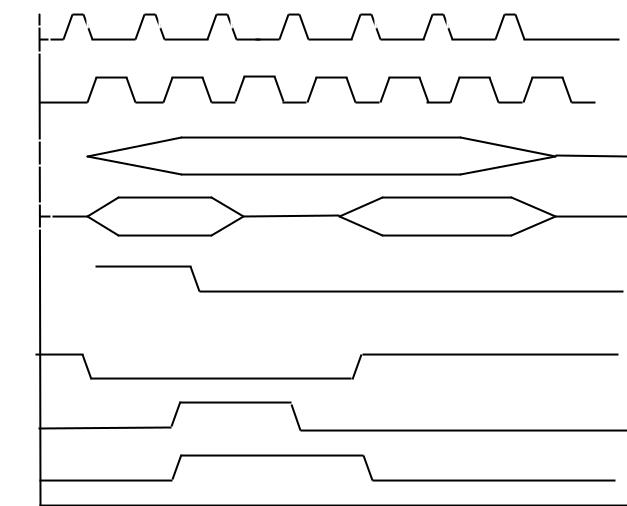

D6 – введення (з УВв); |

|

|

|

|

|

T1 |

T2 |

Tw |

T3 |

T4 |

T5 |

F1 |

|

|

|

|

|

F2

А

D |

PSW |

Вхідні дані |

SYN

RDY

Wait

RD

WR

Рис. 3. Часова діаграма МЦ „Введення даних”.

Таким чином, у машинному циклі виконуються наступні дії:

-видача адреси;

-видача інформації про початий МЦ (PSW);

-аналіз значення вхідних сигналів;

-за необхідності – очікування сигналу READY= 1;

-введення/виведення даних;

-за необхідності – внутрішня обробка/пересилка даних.

У разі реалізації одного МЦ процесор може:

1)прийняти з пам'яті байт команди;

2)прийняти з пам'яті байт даних;

21

3)прийняти з УВв байт даних;

4)прийняти зі стека байт даних;

5)прийняти вектор переривання;

6)видати в пам'ять байт даних;

7)видати в стек байт даних;

8)видати на УВив байт даних.

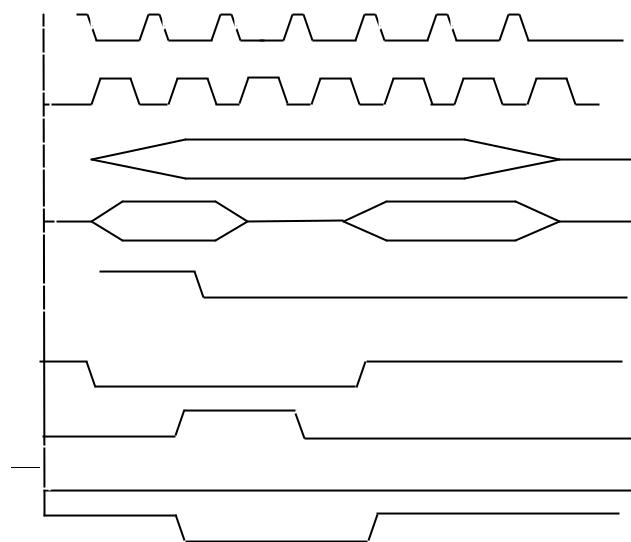

Щодо вихідних сигналів МП всі перелічені вище різновиди МЦ різняться тільки напрямом передачі даних: в МП – цикли 1..5 (Введення), з МП – цикли

6..8 „Виведення” (див. рис. 4).

F1

T1 |

T2 |

Tw |

T3 |

T4 |

T5 |

F2

А

D |

PSW |

Вхідні дані |

SYN

RDY

Wait

RD

WR

Рис. 4. Часова діаграма МЦ „Виведення”.

22

Таблиця 1

|

|

Система команд процесора і80 |

|

|

|

Команда |

Код |

Опис |

1 |

2 |

3 |

ADD A |

87 |

A<-(A) + (A) |

ADD B |

80 |

A<-(B) + (A) |

ADD C |

81 |

A<-(C) + (A) |

ADD D |

82 |

A<-(D) + (A) |

ADD E |

83 |

A<-(E) + (A) |

ADD H |

84 |

A<-(H) + (A) |

ADD L |

85 |

A<-(L) + (A) |

ADD M |

86 |

A<-Loc(HL) + (A) |

ADI d8 |

C6 |

A<-d8 + (A) |

ADC A |

8F |

A<-(A) + (A) + CY |

ADC B |

88 |

A<-(B) + (A) + CY |

ADC C |

89 |

A<-(C) + (A) + CY |

ADC D |

8A |

A<-(D) + (A) + CY |

ADC E |

8B |

A<-(E) + (A) + CY |

ADC H |

8C |

A<-(H) + (A) + CY |

ADC L |

8D |

A<-(L) + (A) + CY |

ADC M |

8E |

A<-Loc(HL) + (A) + CY |

ACI d8 |

CE |

A<-d8 + (A) + CF |

ANA A |

A7 |

Перевірка A |

ANA B |

A0 |

Логічне І B з A |

ANA C |

A1 |

Логічне І C з A |

ANA D |

A2 |

Логічне І D з A |

ANA E |

A3 |

Логічне І E з A |

ANA H |

A4 |

Логічне І H з A |

ANA L |

A5 |

Логічне І L з A |

ANA M |

A6 |

Логічне І Loc(HL) з A |

ANI d8 |

E6 |

Логічне І безпосередніх даних з A |

CALL a16 |

CD |

Передати управління підпрограмі за адресою a16 |

CZ a16 |

CC |

Викликати підпрограму за адресою a16, якщо нуль |

СNZ a16 |

C4 |

Те саме, якщо не нуль |

СP a16 |

F4 |

Те саме, якщо плюс |

СM a16 |

FC |

Те саме, якщо мінус |

CC a16 |

DD |

Те саме, якщо перенос |

CNC a16 |

D4 |

Те саме, якщо відсутній перенос |

CPE a16 |

EC |

Те саме, якщо ділиться на 2 |

CPO a16 |

E4 |

Те саме, якщо не ділиться на 2 |

CMA |

2F |

Інвертувати А |

23

Продовження табл. 1

1 |

2 |

3 |

|

CMC |

3F |

Інвертувати перенос |

|

CMP A |

BF |

Встановити ознаку FZ |

|

CMP B |

B8 |

Порівняти A з B |

|

CMP C |

B9 |

Порівняти A з C |

|

CMP D |

BA |

Порівняти A з D |

|

CMP E |

BB |

Порівняти A з E |

|

CMP H |

BC |

Порівняти A з H |

|

CMP L |

BD |

Порівняти A з L |

|

CMP M |

BE |

Порівняти A з Loc(HL) |

|

CPI d8 |

FC |

Порівняти A з безпосередніми даними, заданими в |

|

команді |

|||

|

|

||

DAA |

27 |

Десяткова корекція акумулятора |

|

DAD |

B |

Скласти BC з HL |

|

DAD |

D |

Скласти DE з HL |

|

DAD |

H |

Скласти HL з HL (подвоєння HL) |

|

DAD |

SP |

Скласти SP з HL |

|

DCR A |

3D |

A<-(A) - 1 (декремент A) |

|

DCR B |

05 |

B<-(B) - 1 |

|

DCR C |

0D |

C<-(C) - 1 |

|

DCR D |

15 |

D<-(D) - 1 |

|

DCR E |

1D |

E<-(E) - 1 |

|

DCR H |

25 |

H<-(H) - 1 |

|

DCR L |

2D |

L<-(L) - 1 |

|

DCR M |

3D |

Loc (HL)<-(Loc(HL)) -1 |

|

DCX B |

0B |

BC<-(BC) - 1 |

|

DCX D |

1B |

DE<-(DE) -1 |

|

DCX H |

2B |

HL<-(HL) - 1 |

|

DCX SP |

0B |

SP<-(SP) -1 |

|

DI |

F3 |

Заборона переривання |

|

EI |

FB |

Дозвіл переривання |

|

HLT |

76 |

Зупинка процесора |

|

IN pp |

DB |

Введення даних через порт pp |

|

INR A |

3C |

A<-(A) + 1 (інкремент A) |

|

INR B |

04 |

Інкремент B |

|

INR C |

0C |

Інкремент C |

|

INR D |

3C |

Інкремент D |

|

INR E |

3C |

Інкремент E |

|

INR H |

3C |

Інкремент H |

|

INR L |

3C |

Інкремент L |

24

Продовження табл. 1

1 |

2 |

3 |

INR M |

34 |

Інкремент вміст Loc(HL) |

INX B |

03 |

Інкремент BС |

INX D |

13 |

Інкремент DE |

INX H |

23 |

Інкремент HL |

INX SP |

33 |

Інкремент SP |

JMP a16 |

C3 |

Перейти по адресу a16 |

JZ a16 |

CA |

Те саме, якщо нуль |

JNZ a16 |

C2 |

Те саме, якщо не нуль |

JP a16 |

F2 |

Те саме, якщо плюс |

JM a16 |

FA |

Те саме, якщо мінус |

JC a16 |

DA |

Те саме, якщо перенос |

JNC a16 |

D2 |

Те саме, якщо відсутній перенос |

JPE a16 |

EA |

Перейти по адресу a16, якщо паритет парний |

JPO a16 |

E2 |

Перейти по адресу a16, якщо паритет непарний |

LDA aaaaa |

3A |

Завантажити в A з комірки за адресою a16 |

LDAX B |

0A |

Завантажити в A з комірки за Loc(BC) |

LDAX D |

1A |

Завантажити в A з комірки за Loc(DE) |

LHLD a16 |

2A |

Завантажити в HL вміст комірки за адресом a16 |

LXI B,d16 |

01 |

Завантажити в BC безпосередні дані d16 |

LXI H,d16 |

21 |

Завантажити в HL безпосередні дані d16 |

LXI SP,d16 |

31 |

Завантажити в SP безпосередні дані d16 |

MOV A,B |

78 |

Переслати з A в B (B<-(A) ) |

MOV A,C |

79 |

Переслати з A в C |

MOV A,D |

7A |

Переслати з A в D |

MOV A,E |

7B |

Переслати з A в E |

MOV A,H |

7C |

Переслати з A в H |

MOV A,L |

7D |

Переслати з A в L |

MOV A,M |

7E |

Переслати з A в Loc(HL) |

MOV B,A |

47 |

Переслати з B в A |

MOV B,C |

41 |

Переслати з B в C |

MOV B,D |

42 |

Переслати з B в D |

MOV B,E |

43 |

Переслати з B в E |

MOV B,H |

44 |

Переслати з B в H |

MOV B,L |

45 |

Переслати з B в L |

MOV B,M |

46 |

Переслати з B в Loc(HL) |

MOV C,A |

4F |

Переслати з C в A |

MOV C,B |

48 |

Переслати з C в B |

MOV C,D |

4A |

Переслати з C в D |

MOV C,E |

4B |

Переслати з C в E |

MOV C,H |

4C |

Переслати з C в H |

25

Продовження табл. 1

1 |

2 |

3 |

MOV C,L |

4D |

Переслати з C в L |

MOV C,M |

4E |

Переслати з C в Loc(HL) |

MOV D,A |

57 |

Переслати з D в A |

MOV D,B |

50 |

Переслати з D в B |

MOV D,C |

51 |

Переслати з D в C |

MOV D,E |

53 |

Переслати з D в E |

MOV D,H |

54 |

Переслати з D в H |

MOV D,L |

55 |

Переслати з D в L |

MOV D,M |

56 |

Переслати з D в Loc(HL) |

MOV E,A |

5F |

Переслати з E в A |

MOV E,B |

58 |

Переслати з E в B |

MOV E,C |

59 |

Переслати з E в C |

MOV E,D |

5A |

Переслати з E в D |

MOV E,H |

5C |

Переслати з E в H |

MOV E,L |

5D |

Переслати з E в L |

MOV E,M |

5E |

Переслати з E в Loc(HL) |

MOV H,A |

67 |

Переслати з H в A |

MOV H,B |

60 |

Переслати з H в B |

MOV H,C |

61 |

Переслати з H в C |

MOV H,D |

62 |

Переслати з H в D |

MOV H,E |

63 |

Переслати з H в E |

MOV H,L |

65 |

Переслати з H в L |

MOV H,M |

66 |

Переслати з H в Loc(HL) |

MOV L,A |

6F |

Переслати з L в A |

MOV L,B |

68 |

Переслати з L в B |

MOV L,C |

69 |

Переслати з L в C |

MOV L,D |

6A |

Переслати з L в D |

MOV L,E |

6B |

Переслати з L в E |

MOV L,H |

6C |

Переслати з L в H |

MOV L,M |

6E |

Переслати з L в Loc(HL) |

MOV M,A |

77 |

Переслати з M в A |

MOV M,B |

70 |

Переслати з M в B |

MOV M,C |

71 |

Переслати з M в C |

MOV M,D |

72 |

Переслати з M в D |

MOV M,E |

73 |

Переслати з M в E |

MOV M,H |

74 |

Переслати з M в H |

MOV M,L |

75 |

Переслати з M в L |

MVI A,d8 |

3E |

Переслати d8 в A |

MVI B,d8 |

06 |

Переслати d8 в B |

MVI C,d8 |

0E |

Переслати d8 в C |

26

Продовження табл. 1

1 |

2 |

3 |

MVI D,d8 |

16 |

Переслати d8 в D |

MVI E,d8 |

1E |

Переслати d8 в E |

MVI H,d8 |

26 |

Переслати d8 в H |

MVI L,d8 |

2E |

Переслати d8 в L |

MVI M,d8 |

36 |

Переслати d8 в Loc(HL) |

NOP |

00 |

|

ORA A |

B7 |

Перевірити A і скинути перенос |

ORA B |

B0 |

Логічна операція B АБО A |

ORA C |

B1 |

Логічна операція C АБО A |

ORA D |

B2 |

Логічна операція D АБО A |

ORA E |

B3 |

Логічна операція E АБО A |

ORA H |

B4 |

Логічна операція H АБО A |

ORA L |

B5 |

Логічна операція L АБО A |

ORA M |

B6 |

Логічна операція M АБО A |

ORI d8 |

F6 |

Логічна операція d8 АБО A |

OUT pp |

D3 |

Записати A в порт pp |

PCHL |

E9 |

Передати управління по адресу в HL |

POP B |

C1 |

Вилучити слово зі стеку в BC |

POP D |

D1 |

Вилучити слово зі стеку в DE |

POP H |

E1 |

Вилучити слово зі стеку в HL |

POP PSW |

F1 |

Вилучити слово зі стеку в PSW |

PUSH B |

C5 |

Занести до стеку вміст BC |

PUSH D |

D5 |

Занести до стеку вміст DE |

PUSH H |

E5 |

Занести до стеку вміст HL |

PUSH PSW |

F5 |

Занести до стеку вміст PSW |

RAL |

17 |

Циклічний зсув CY + A вліво |

RAR |

1F |

Циклічний зсув CY + A вправо |

RLG |

07 |

Зсув A вліво на один розряд з переносом |

RRG |

0F |

Зсув A вправо на один розряд з переносом |

RIM |

20 |

Зчитати маску переривання (в 8085) |

RET |

C9 |

Повернення з підпрограми |

RZ |

C8 |

Повернення з підпрограми, якщо FZ = 0 |

RNZ |

C0 |

Повернення з підпрограми, якщо FZ = 1 |

RP |

F0 |

Повернення з підпрограми, якщо FP = 1 |

RM |

F8 |

Повернення з підпрограми, якщо FP = 0 |

RC |

D8 |

Повернення з підпрограми, якщо FC = 1 |

RNC |

D0 |

Повернення з підпрограми, якщо FC = 0 |

RPO |

E0 |

Повернення з підпрограми, якщо паритет непарний |

RST 0 |

C7 |

Запуск програми з адреси 0 |

RST 1 |

CF |

Запуск програми з адреси 8h |

27

Продовження табл. 1

1 |

2 |

3 |

RST 2 |

D7 |

Запуск програми з адреси 10h |

RST 3 |

DF |

Запуск програми з адреси 18h |

RST 4 |

E7 |

Запуск програми з адреси 20h |

RST 5 |

EF |

Запуск програми з адреси 28h |

RST 6 |

F7 |

Запуск програми з адреси 30h |

RST 7 |

FF |

Запуск програми з адреси 38h |

SIM |

30 |

Встановити маску переривання (тільки в 8085) |

SPHL |

F9 |

Завантажити SP із HL |

SHLD a16 |

22 |

Записати HL по адресу a16 |

STA a16 |

32 |

Записати A по адресу a16 |

STAX B |

02 |

Записати A по адресу Loc(BC) |

STAX D |

12 |

Записати A по адресу Loc(DE) |

STC |

37 |

Встановити ознаку переносу (CF = 1) |

SUB A |

9F |

Відняти А з А (очистити А) |

SUB B |

98 |

Відняти B з А |

SUB C |

99 |

Відняти C з А |

SUB D |

9A |

Відняти D з А |

SUB E |

9B |

Відняти E з А |

SUB H |

9C |

Відняти H з А |

SUB L |

9D |

Відняти L з А |

SUB M |

9E |

Відняти M з А |

SUI d8 |

DE |

Відняти d8 з А |

SBB A |

9F |

Відняти А з А (очистити А) |

SBB B |

98 |

Відняти з переносом B з А |

SBB C |

99 |

Відняти з переносом C з А |

SBB D |

9A |

Відняти з переносом D з А |

SBB E |

9B |

Відняти з переносом E з А |

SBB H |

9C |

Відняти з переносом H з А |

SBB L |

9D |

Відняти з переносом L з А |

SBB M |

9E |

Відняти з переносом M з А |

SBI d8 |

DE |

Відняти з переносом d8 з А |

XCHG |

EB |

Обмін вмісту DE і HL |

XTHL |

E3 |

Обмін вмісту вершини стеку з вмістом HL |

XRA A |

AF |

Виключаюче АБО A з A (очистка A) |

XRA B |

A8 |

Виключаюче АБО B з A |

XRA C |

A9 |

Виключаюче АБО C з A |

XRA D |

AA |

Виключаюче АБО D з A |

XRA E |

AB |

Виключаюче АБО E з A |

XRA H |

AC |

Виключаюче АБО H з A |

XRA L |

AD |

Виключаюче АБО L з A |

28

Продовження табл. 1

1 |

2 |

3 |

XRA M |

AE |

Виключаюче АБО Loc(HL) з A |

XRI d8 |

EE |

Виключаюче АБО d8 з A |

Умовні позначення в командах

A, B, ..., L – назва 8-розрядних регістрів.

BC, DE, HL – назва регістрових пар, що утворюють 16-розряднi регістри.

SP – 16-розрядний покажчик стеку.

PSW – слово стану програми, містить регістр ознак. a16 – двобайтова адреса.

d8 – байт безпосередніх даних.

d16 – два байти безпосередніх даних. pp – номер порту введення-виведення.

Порядок виконання роботи

1.Ознайомитись із системою команд 8-розрядного процесора.

2.Завантажити програмну оболонку емулятора 8-розрядного процесора.

3.Ввести по порядку команди різного призначення і ознайомитись з результатами їхньої дії, стану регістрів, ознак тощо.

4.Завершити роботу емулятора.

Зміст звіту

1.Тему, мету, обладнання і матеріали лабораторної роботи.

2.Систему команд 8-розрядного процесора.

3.Перелік команд, які виконувались емулятором, результати їх виконання (значення регістрів, пам’яті, регістра ознак, портів, тощо).

4.Висновки.

Завдання для самоконтролю

1.Як групуються команди процесора ?

2.Охарактеризуйте виконання команд процесора.

3.Що таке цикл виконання команди ?

29

4.Що таке такт виконання команди ?

5.Поясніть принцип роботи наведених часових діаграм виконання команд процесора.

6.Поясніть функціональне призначення шин процесора.

Бібліографічний список

1. Бучма І.М. Мікропроцесорні пристрої: Навчальний посібник. – Львів:

Видавництво Національного університету “Львівська політехніка, 2005. –

306 с.

2.Джордейн Р. Справочник программиста персональных компьютеров типа IBM PC, XT, AT: Пер. с англ./Предисл. Н. В. Гайского. –М.: Финансы и статистика, 1992. – 544 c.: ил.

3.Преснухин и др. Расчет элементов цифровых устройств: Учеб.

Пособие/ Л.Н. Преснухин, Н.В. Воробьев, А.А. Шишкевич; Под ред. Л. Н.

Преснухина. – 2-е изд., перераб. и доп. – М.: Высш. шк., 1991. – 526 с.: ил.

4. Зубчик В. И. и др. Справочник по цифровой схемотехники / В. И.

Зубчик, В. П. Сигорский, А. Н. Шкуро. – К.: Техника, 1990. – 448 с.

5. Лю Ю-Чжен, Гибсон Г. Микропроцессоры семейства 8086/8088. –

М.:Радио и связь, 1987. 512 с.

6. Гивоке Д., Россер Р. Микропроцессоры и микрокомпьютеры – М.:

Мир, 1983.– 464с.

7. Бойко В.И., Гуржий А. Н., Жуйков В.Я. и др. Схемотехника электронных систем. Микропроцессоры и микроконтроллеры. СПб.: БХВ-

Петербург, 2004. –464 с.

30