МК

.pdf4.Натиснути на клавішу П і ввести код 0000 (перша адреса ПЗП). На дисплеї з'явиться код 26. Послідовно натискаючи на клавішу П, переглянути вміст декількох осередків ПЗП.

5.Пересвідчитися, що вміст пам'яті можна переглянути за допомогою послідовного натиснення на клавішу |_|. Таким чином використання цього режиму дозволяє перевірити вміст усіх елементів пам'яті мікро-ЕОМ.

Завдання 3. Записати числа в пам'ять мікро-ЕОМ.

Порядок виконання завдання

1. Увімкнути тумблер "МЕРЕЖА" (якщо мікро-ЕОМ вимкнена,

натиснути на клавішу СБ).

2.Натиснути на клавішу |_| і після цього набрати адресу 0800. На дисплеї після введення адреси з'явиться її вміст 00.

3.Натиснути на клавішу 1. Мікро-ЕОМ вводить значення цифри натиснутої клавіші в молодший розряд даних, при цьому в цьому розряді дисплея з'являється десятерична точка. Вона свідчить про те, що мікро-ЕОМ перебуває в режимі введення даних і число, представлене на дисплеї даних, не

єістинним вмістом адреси пам'яті, показаної на адресному дисплеї.

4.Натиснути на клавішу 2. Пересвідчитися при цьому, що цифра 1

молодшого розряду перемістилася на старший розряд дисплея даних, а цифра 2

– на її місце (десятерична точка залишилася в молодшому розряді). Перевірити,

що подальші натиснення на цифрові клавіші призводять до введення цифри натиснутої клавіші в молодший розряд дисплея даних і зміщення в старший розряд попередньої натиснутої клавіші.

5. Записати натисненням на клавішу ВП число, представлене на дисплеї за адресою 0800. При цьому на дисплеї з'являться адреса 0801 та її вміст (00), а

десятерична точка згасне, показуючи, що дані введені і мікро-ЕОМ вийшла з режиму введення даних.

6. Записати будь-яке число на дисплей даних за наявності на дисплеї

11

адреси 0801.

7. Натиснути на клавішу П і на адресному дисплеї набрати адресу 0800.

Пересвідчитися при цьому, що число записане за цією адресою. Відсутність десятеричної точки в молодшому розряді дисплея свідчить про те, що це число мікро-ЕОМ витягла з пам'яті.

8. Натиснути на клавішу |_| і перевірити вміст адреси 0801.

Пересвідчитися при цьому, що число, записане на дисплеї даних, не було записане в пам'ять після натиснення на клавішу ВП.

9. Здійснити виведення на дисплей вмісту адреси 0000 (ПЗП). На дисплеї буде число 26. Записати за цією адресою на дисплеї будь-яке інше число.

Пересвідчитися, що після натиснення на клавішу |_| запис даних у ПЗП неможливий і при цьому мікро-ЕОМ визначає цю дію як помилку, формує звуковий сигнал, не збільшує адресу і виводить на дисплей істинне число,

записане в ПЗП.

Примітка. Для виконання цього завдання показана методика введення і перевірки правильності введення програм в мікро-ЕОМ за допомогою клавіш П, |_|, ВП.

Завдання 4. Записати числа в програмно-доступні регістри МП.

Порядок виконання завдання

1. Увімкнути мікро-ЕОМ. Після виведення на дисплей повідомлення натиснути на клавішу РГ. На дисплей буде виведено вміст акумулятора (А)

МП. Багато разів натискаючи на клавішу |_|, перевірити послідовність виведення вмісту внутрішніх регістрів МП на дисплей.

2.Змінити число, записане в регістрі за наявності на дисплеї інформації про його зміст, за допомогою цифрових клавіш клавіатури. Натиснути на клавішу |_|.

3.Натиснути на клавішу ВП і пересвідчитися при цьому в правильності запису числа в регістр.

12

Завдання 5. Здійснити пуск програми.

Порядок виконання завдання

1. Для здійснення пуску програми з будь-якої адреси пам'яті вивести цю адресу на дисплей. Пуск програми здійснюється натисненням на клавішу ВП

(пуск), при цьому в програмний лічильник МП записується адреса, вказана на дисплеї, і виконання програми починається з неї. Записати на дисплей адресу

05ВО, що є початком музичної програми, записаної в ПЗП.

2. Натиснути на клавішу ВП, при цьому мікро-ЕОМ виконає мелодію за нотами, записаними в ПЗП.

3. Пересвідчитися, що виконання програми можна зупинити натисненням на клавішу СТ. Для цього повторити пуск музичної програми спочатку і під час її виконаня натиснути на клавішу СТ. Після зупинки програми на дисплей виводиметься адреса, записана в програмному лічильнику, і його вміст на момент зупинки. Після зупинки програми перевірити можливість здійснення режиму виведення на дисплей вмісту регістрів МП на момент зупинки, для чого потрібно натиснути на клавішу РГ,

при цьому на дисплеї з'явиться вміст акумулятора МП. Послідовним натисненням на клавішу |_| перевірити виведення на дисплей вмісту регістра МП.

4. Натисненням на клавішу ПР вивести на дисплей адресу пам'яті, на якій перерване виконання програми. Натиснути на клавішу ВП (пуск) і продовжити виконання програми.

Зміст звіту

1.Схема структури навчальної мікро-ЕОМ.

2.Карта пам'яті.

3.Інформація про вміст внутрішніх програмно-доступних регістрів МП після програми початкової установки мікро-ЕОМ.

4.Висновки

13

Завдання для самоконтролю

1.Зобразіть структуру навчальної мікро-ЕОМ.

2.Вкажіть функціональні частини на принциповій схемі мікро-ЕОМ.

3.Для якої мети в мікро-ЕОМ використовується робота МП в режимі очікування?

4.Що таке карта пам'яті мікро-ЕОМ?

5.Які адреси пам'яті мікро-ЕОМ належать до ОЗП і ПЗП?

6.Розкажіть про можливі режими роботи мікро-ЕОМ,

7.Як записати числа в програмно-доступні регістри МП або пам'ять мікро-ЕОМ?

8.Що відбувається в мікро-ЕОМ під час спроби запису даних у ПЗП?

9.Які вузли перевіряються в мікро-ЕОМ у процесі виконання тестів після її увімкнення або натиснення на клавішу СБ?

10.Вкажіть можливі зміни режимів роботи мікро-ЕОМ, виконує програші за командами.

11.Опишіть функції кожної клавіші управління на клавіатурі.

12.Вкажіть, які значення записуються в регістри МП ВІС і ОЗП в процесі виконання програми початкової установки мікро-ЕОМ.

Бібліографічний список

1.Горбунов В.Л., Панфилов Д.И., Преснухин Д.Л. Микропроцессоры. Основы построения микро-ЭВМ.– М.: Высшая школа, 1984.

2.Панфилов Д.И., Красавин В.Н., Романенко О.А. Учебная микро-ЭВМ на базе микропроцессорного комплекта серии К580 //Электронная промышленность. – 1983. – № 9.–С.20-24

14

ЛАБОРАТОРНА РОБОТА №2

ВИВЧЕННЯ СИСТЕМИ КОМАНД 8-РОЗРЯДНОГО ПРОЦЕСОРА

Мета роботи: ознайомлення із системою команд 8-розрядного процесора типу К580ВМ80, особливістю виконання команд, оволодіння роботою емулятора процесора.

Обладнання, прилади та інструменти: ПЕОМ, система команд процесора К580ВМ80, програма-емулятор роботи процесора, інструкція

користувача.

Загальні відомості

Як відомо, процесор є основним обчислювальним блоком комп'ютера,

найбільшою мірою визначаючим його потужність. Це пристрій, який виконує програму – послідовність команд (інструкцій), задуману програмістом й оформлену у вигляді модуля програмного коду. Щоб зрозуміти, що робить процесор, розглянемо його в оточенні системних компонентів IBM PC-

сумісного комп'ютера. Цією комп'ютерною архітектурою, природно, не обмежується сфера застосування процесорів. Усім відомий IBM PC-сумісний комп'ютер є реалізацією так званої фон-нейманівської архітектури обчислювальних машин. Ця архітектура представлена Джоном фон Нейманом ще в 1945 році і має наступні основні ознаки. Машина складається з блоку управління, арифметико-логічного пристрою (АЛП), пам'яті і пристроїв введення-виведення. У ній реалізується концепція збереженої програми:

програми і дані зберігаються в одній і тій самій пам'яті. Виконувані дії визначаються блоком управління і АЛП, які разом є основою центрального процесора. Центральний процесор вибирає і виконує команди з пам'яті послідовно, адреса чергової команди задається "лічильником адреси" в блоці управління. Цей принцип виконання називається послідовною передачею управління. Дані, з якими працює програма, можуть містити змінні – іменовані області пам'яті, в яких зберігаються значення з метою подальшого використовування в програмі. Фон-нейманівська архітектура – не єдиний

15

варіант побудови ЕОМ, є й інші, які не відповідають зазначеним принципам

(наприклад, потокові машини). Проте переважна більшість сучасних комп'ютерів заснована саме на цих принципах, включаючи і складні багатопроцесорні комплекси, які можна розглядати як об'єднання фон-

нейманівських машин. Звичайно ж, за більш ніж півстолітню історію ЕОМ класична архітектура пройшла довгий шлях розвитку. Загалом під архітектурою процесора розуміється його програмна модель, тобто програмно-

видимі властивості. Під мікроархітектурою розуміється внутрішня реалізація цієї програмної моделі. Для однієї й тієї самої архітектури різними фірмами і в різних поколіннях застосовуються істотно різні мікроархітектурні реалізації,

при цьому, природно, прагнуть до максимального підвищення продуктивності

(швидкості виконання програм). Зараз існує безліч архітектури процесорів, які поділяють на дві глобальні категорії – RISC і CISC. RISC – Reduced (Restricted) Instruction Set Computer – процесори (комп'ютери) зі скороченою системою команд. Ці процесори мають набір однорідних регістрів універсального призначення. Система команд вирізняється відносною простотою коди інструкцій мають чітку структуру, як правило, з фіксованою довжиною. Певні переваги дає й уніфікація регістрів. CISC – Complete Instruction Set Computer –

процесори (комп'ютери) з повним набором інструкцій, до яких належить і сімейство х86. Склад і призначення їх регістрів істотно неоднорідний, широкий набір команд ускладнює декодування інструкцій, на що витрачаються апаратні ресурси. Зростає кількість тактів, необхідна для виконання інструкцій.

Процесори х86 мають найскладнішу у світі систему команд. Чи добре це,

питання спірне, але вантаж сумісності з програмним забезпеченням для IBM PC, що має вже 20-річну історію, не дозволяє розлучатися з цією "спадщиною важкого минулого". У процесорах сімейства х86, починаючи з 486,

застосовується комбінована архітектура – CISC-процесор має RISC-ядро.

Розрізняють наступні способи організації обчислювального процесу:

- один потік команд – один потік даних (Simple Instruction - Simple Data).

16

SISD – властивий традиційній фон-нейманівській архітектурі (іноді замість

Simple пишуть Single);

-один потік команд – множинний потік даних (Simple Instruction - Multiple Data) – технологія ММХ;

-множинний потік команд – один потік даних (Multiple Instruction - Simple Data, MISD);

-множинний потік команд – множинний потік даних (Multiple Instruction

-Multiple Data, MIMD).

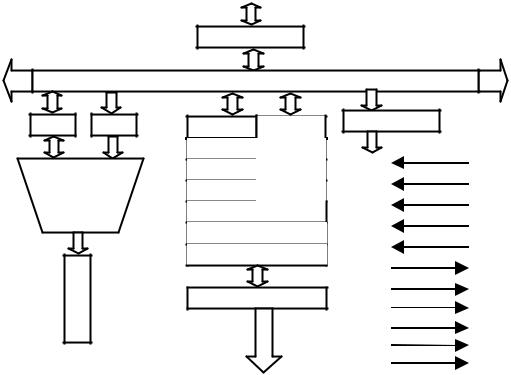

На рис. 2 показана спрощена внутрішня структура МП і8080, яка складається з 8-розрядного АЛП з буферним регістром і схемою десяткової корекції, блоку РОН, регістрів покажчика стека SP і лічильника команд PC,

первинного управляючого автомата УА, буферних схем шин адреси, даних і схеми управління системою.

Зовнішній інтерфейс представлений 8-розрядною двонаправленою шиною даних D[7:0], 16-розрядною шиною адреси А[15:0] і групою ліній управління. Призначення вхідних і вихідних ліній МП:

D[7:0] - двонаправлена шина даних слугує для прийому і видачі даних,

прийому команди, прийому вектора переривання, видачі додаткової управляючої інформації (слово PSW);

Командний цикл мікропроцесора

Мікропроцесор працює у складі МПС, обмінюючись інформацією з пам'яттю і ЗПр. В основі роботи МП лежить командний цикл – дії щодо вибору з пам'яті і виконання однієї команди. Залежно від типу і формату команди,

способів адресації і кількості операндів командний цикл може охоплювати різне кількість звернень до пам'яті і ЗПр, а отже мати різну тривалість. Будь-

який командний цикл (КЦ) починається з витягання з пам'яті першого байта команди за адресою, що зберігається в PC. Команди і80 мають довжину 1, 2 або

3 байти.

17

8-розрядний мікропроцесор i8080

|

|

DB[7:0] |

|

|

|

Буфер даних |

|

|

|

Внутрішня шина 8 біт |

|

А |

W2 |

W2 |

W3 |

|

|

B |

C |

|

|

D |

E |

|

АЛП |

H |

L |

|

|

||

|

|

SP |

|

PC

|

Іnc/Деc |

Flags |

Буфер адреса |

|

|

|

16 |

|

А[15:0] |

Pr. команд

|

F1, F2 |

|

|

|

RESET |

Управляючий автомат |

READY |

SYNC |

|

|

INT |

|

RD |

|

WR |

|

WAIT |

|

INTE |

|

HLDA |

|

|

Рис. 2. Внутрішня структура МП і8080

А[15:0] – однонаправлена шина адреси слугує для видачі адреси пам'яті і пристроїв уведення-виведення;

F1, F2 – сигнали тактового генератора частотою 1...2,5 Мгц;

RESET – скидання (початкова установка і запуск програми з адреси

0000);

READY – вхідний сигнал готовності пам'яті або ЗПр до обміну

(забезпечує асинхронний режим обміну);

INT – запит зовнішнього переривання;

HOLD – захоплення шини (прямого доступу до пам'яті з боку ЗПр);

WR – запис – вихідний сигнал, що визначає напрям передачі інформації по шині даних від процесора до пам'яті або ЗПр;

RD – читання – вихідний сигнал, що визначає напрям передачі інформації по шині даних від пам'яті або ЗПр до процесора;

18

SYNC – вихідний сигнал, що ідентифікує наявність на шині даних додаткової управляючої інформації (PSW);

WAIT – вихідний сигнал, відзначає стан очікування або зупинки МП;

INTE – вихідний сигнал підтвердження зовнішніх переривань;

HLDA – вихідний сигнал підтвердження режиму прямого доступу до пам'яті (підтвердження захоплення).

У першому байті міститься інформація про довжину команди. У разі 2-

або 3-байтової команди реалізуються додаткові звернення до пам'яті за сусідніми (великими) адресами. Після прочитування команди починається її виконання, під час якого можливе одне або декілька звернень до пам'яті або ЗПр (читання операнда, запис результату).

Для реалізації команди 18080 можливі від 1 до 5 звернень до пам'яті (ЗП).

Хоча звернення до ЗП/ЗПр розташовуються в різних частинах КЦ, виконуються вони за єдиними правилами відповідного інтерфейсу МПС і реалізовані управляючим автоматом. Дії МПС з передачі ЗП/ЗПр МП одного байта даних/команди називаються машинним циклом.

Машинні цикли та їх ідентифікація

Командний цикл є послідовністю машинних циклів (МЦ), причому КЦ i80 може містити від 1 до 5 МЦ, які прийнято позначати M1, M2, M5.

Машинний цикл обов’язково передбачає дії з передачі байта інформації.

Крім того, в деяких МЦ додатково реалізуються дії з пересилки і/або перетворення інформації усередині МП. Тому тривалість МЦ може бути різною

– за рахунок різної кількості машинних тактів (T1, T2...).

Машинний такт (такт) утворює пара сигналів тактового генератора F1, F2.

Тому тривалість такту постійна - період тактового генератора (за винятком такту Tw - див. далі).

Таким чином, є очевидною ієрархія процедур в роботі мікропроцесора (не тільки i8080):

Командний цикл → Машинний цикл → Машинний такт.

19

Кожному такту відповідає певний стан управляючого автомата. Будь-

який МЦ i80 обов'язково містить такти Т1, Т2, Т3, призначені для передачі байта по інтерфейсу. Машинні цикли, в яких здійснюється передача і/або перетворен-

ня інформації в МП, містять додатково один або два такти Т4, T5; МП і80

виробляє кілька типів МЦ, основними з яких є цикли ПРИЙОМ і ВИДАЧА.

Машинний цикл МЦ мікропроцесора і80 передбачає можливість обміну як у синхронному, так і в асинхронному режимі (див. рис. 3). Якщо у складі МПС використані тільки „швидкі пристрої”, тобто такі, які можуть працювати з тактовою частотою МП, то передача інформації в МЦ здійснюється в синхронному режимі. У цьому разі на вхід READY МП подається константа „1”

і після такту Т2 починається такт Т3. У роботі з „повільними пристроями”,

швидкодія яких не дозволяє перемикатися з частотою тактового генератора МП, необхідно „розтягнути” в часі МЦ, реалізувавши асинхронний принцип обміну. Для цього на початку МЦ обміну з „повільними пристроями” на вході

READY формується рівень логічного нуля. У такті Т2 МП аналізує стан

READY, якщо READY = 0, то МП після Т2 переходить не до Т3, а до такту очікування Tw, який може тривати довільне число періодів тактового генератора. Перехід до Т3 здійснюється по фазі Ф1, якщо в попередній Ф2

READY встановився в „1“. За допомогою входу READY можна не тільки погоджувати роботу МП з пристроями різної швидкодії, й реалізовувати покроковий і потактовий режими роботи МП. Дефіцит зовнішніх висновків МП не дозволяє виводити в зовнішній інтерфейс достатній для ефективного функціонування обсяг управляючої інформації. Для видачі повнішої інформації про стан МП в поточному МЦ використовується мультиплексування шини даних. На початку кожного МЦ на лінії шини даних D[7:0] видається байт додаткової управляючої інформації (т.з. PSW), розряди якого мають наступне призначення: DO – підтвердження переривання; D1 – запис (в ЗПр) або висновок (на УВив); D2 – обіг в стек; D3 – підтвердження зупинки; D4 –

висновок (на УВив); D5 – Ml (прочитування з пам'яті першого байта команди);

20