- •Цифровые и микропроцессорные устройства

- •1 Тема № 1. Устройство умножения двоичных чисел

- •2 Тема № 2. Устройство суммирования двоичных чисел

- •3 Тема № 3. Устройство сдвига двоичных чисел

- •4 Содержание курсового проекта

- •Пример синтеза недвоичного счетчика на jk-триггерах

- •Примеры оформления заданий на курсовое проектирование к темам № 1…3

- •Основные требования к оформлению курсового проекта

- •Пример оформления титульного листа к курсовому проекту для студентов дневной или заочной форм обучения

- •Устройство суммирования двоичных чисел

- •Приложение а

- •Перечень элементов

- •Содержание

- •Цифровые и микропроцессорные устройства

1 Тема № 1. Устройство умножения двоичных чисел

1.1 Описание принципа работы заданной структурной электрической схемы устройства умножения двоичных чисел

Структурная электрическая схема устройства умножения четырехразрядных двоичных чисел представлена на рисунке 1.

Рисунок 1 – Устройство умножения двоичных чисел. Схема электрическая структурная

Рассмотрим назначение узлов, входящих в структурную схему устройства.

Умножитель

Y3

предназначен для умножения четырехразрядных

двоичных чисел A

и B,

представленных разрядами

![]() ,

,![]() ,

,![]() ,

,![]() и

и![]() ,

,![]() ,

,![]() ,

,![]() .

На выходе умножителя формируется

восьмиразрядное произведениеQ,

представленное разрядами

.

На выходе умножителя формируется

восьмиразрядное произведениеQ,

представленное разрядами

![]() ,

,![]() ,…,

,…,![]() .

.

Регистр Y1 предназначен для параллельного ввода четырехразрядного множимого A в двоичной системе счисления (СС). Значение множимого A может меняться в пределах от 0 до 15 в десятичной СС.

Счетчик Y2 предназначен для параллельного ввода четырехразрядного множителя B в двоичной СС. Значение множителя B также может меняться от 0 до15 в десятичной СС.

Регистр Y4 предназначен для параллельного вывода результата умножения, который представляет собой восьмиразрядное кодовое слово.

Загрузка

сомножителей и запись результата

умножения синхронизируется тактовыми

импульсами

![]() .

Причем ввод сомножителей осуществляется

по отрицательным фронтам тактовых

импульсов, а вывод результата умножения

– по положительным.

.

Причем ввод сомножителей осуществляется

по отрицательным фронтам тактовых

импульсов, а вывод результата умножения

– по положительным.

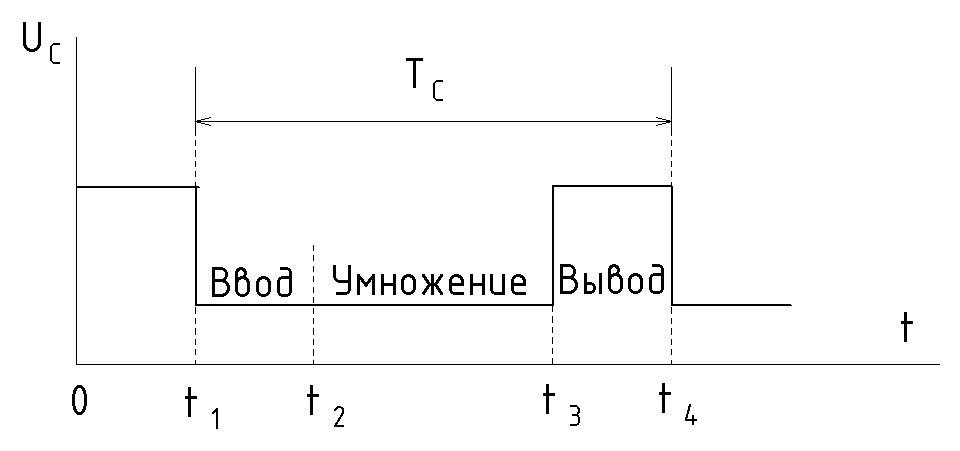

Процесс функционирования устройства поясняется временной диаграммой, которая представлена на рисунке 2.

Рисунок 2 – Временная диаграмма, поясняющая процесс функционирования устройства

В

момент времени

![]() по

отрицательному фронту тактового импульса

начинается ввод сомножителей в регистр

Y1

и счетчик Y2

(рисунок 1). К моменту времени

по

отрицательному фронту тактового импульса

начинается ввод сомножителей в регистр

Y1

и счетчик Y2

(рисунок 1). К моменту времени

![]() ввод заканчивается и начинается процесс

умножения в умножителе У3. Этот процесс

в худшем случае завершается к моменту

времени

ввод заканчивается и начинается процесс

умножения в умножителе У3. Этот процесс

в худшем случае завершается к моменту

времени![]() .

Затем по положительному фронту тактового

импульса результат умножения записывается

в регистрY4

и т.д. При подаче нужного уровня напряжения

на вход

.

Затем по положительному фронту тактового

импульса результат умножения записывается

в регистрY4

и т.д. При подаче нужного уровня напряжения

на вход

![]() (рисунок 1) устройство сбрасывается в

исходное нулевое состояние.

(рисунок 1) устройство сбрасывается в

исходное нулевое состояние.

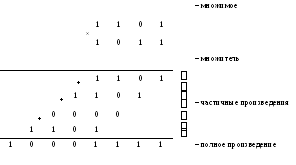

Рассмотрим

процесс умножения двоичных чисел на

примере умножения заданных чисел1),

например,

![]() и

и

![]() .

Умножение выполним, начиная с младшего

разряда множителя:

.

Умножение выполним, начиная с младшего

разряда множителя:

Таким образом, при умножении двоичных чисел формируются частичные произведения, сдвигаются и суммируются. Сравним результаты умножения чисел A и B в двоичной и десятичной СС. Для этого преобразуем результат умножения в десятичную систему счисления:

![]()

Они

совпадают и равны

![]() .

.

1.2 Задание на проектирование к теме № 1

Описать

принцип построения и разработать

логическую схему матричного умножителя

четырехразрядных двоичных чисел.

Разработать логическую схему суммирующего

четырехразрядного недвоичного счетчика

на JK-триггерах

с коэффициентом пересчета

![]() заданным в таблице 2. В принципиальной

электрической схеме устройства

использовать двоичный счетчик. Разработать

в основном базисе логическую схему

четырехразрядного двоичного сумматора

с параллельным переносом. Разработать

принципиальную электрическую схему

устройства умножения по заданной

структурной схеме (рисунок 1) на микросхемах

схемотехники КМОП, серии которых указаны

в таблице 2.

заданным в таблице 2. В принципиальной

электрической схеме устройства

использовать двоичный счетчик. Разработать

в основном базисе логическую схему

четырехразрядного двоичного сумматора

с параллельным переносом. Разработать

принципиальную электрическую схему

устройства умножения по заданной

структурной схеме (рисунок 1) на микросхемах

схемотехники КМОП, серии которых указаны

в таблице 2.

Таблица 2 – Исходные данные для проектирования устройства умножения двоичных чисел

|

Номер варианта |

Значение числа A (P=10) |

Значение числа B (P=10) |

Серия микросхем |

|

|

1.1 |

14 |

6 |

1594, 5564 |

9 |

|

1.2 |

13 |

5 |

1554, 1564 |

11 |

|

1.3 |

11 |

7 |

1594, 5564 |

12 |

|

1.4 |

10 |

13 |

1554, 1564 |

13 |

|

1.5 |

9 |

12 |

1594, 5564 |

14 |

|

1.6 |

7 |

11 |

1554, 1564 |

15 |

|

1.7 |

3 |

10 |

1594, 5564 |

9 |

|

1.8 |

13 |

3 |

1554, 1564 |

11 |

|

1.9 |

5 |

12 |

1594, 5564 |

12 |

|

1.10 |

14 |

7 |

1554, 1564 |

13 |

Описать

работу принципиальной электрической

схемы устройства в течение одного

периода сигнала синхронизации

![]() при умножении заданных в таблице 2 чиселA

и B.

Пример оформления задания к теме № 1

приведен в приложении Б.

при умножении заданных в таблице 2 чиселA

и B.

Пример оформления задания к теме № 1

приведен в приложении Б.

1.3 Назначение и принцип построения матричных умножителей двоичных чисел

Умножителем называется комбинационное цифровое устройство, формирующее на выходе число Q, равное произведению входных двоичных чисел A и B [9, 10].

Условное графическое обозначение умножителя представлено на рисунке 3.

Рисунок 3 – Условное графическое обозначение умножителя

Предполагается,

что числа A,

B

и Q

представлены в двоичной позиционной

системе счисления. При этом, если число

A

имеет n

двоичных разрядов (![]() ,

, ![]() ,…,

,…, ![]() ),

числоB

имеет m

двоичных разрядов (

),

числоB

имеет m

двоичных разрядов (![]() ,

, ![]() ,…,

,…, ![]() ),

то для представления максимального

значения произведения

),

то для представления максимального

значения произведения![]() требуетсяn+m

двоичных разрядов числа Q

(

требуетсяn+m

двоичных разрядов числа Q

(![]() ,

, ![]() ,…,

,…, ![]() ).

Каждый разряд произведения является

логической (переключательной) функцией

аргументов

).

Каждый разряд произведения является

логической (переключательной) функцией

аргументов![]() ,

, ![]() ,…,

,…, ![]() и

и![]() ,

, ![]() ,…,

,…, ![]() ,

значения которого можно найти из таблиц

умножения либо путем выполнения умножения

для заданных значений аргументов. Однако

прямой логический синтез схемы умножителя,

основанный на представлении функции

выражениями в булевой алгебре, ввиду

громоздкости неэффективен. Исключения

составляют простейшие случаи перемножения

одноразрядных или двухразрядных двоичных

чисел. Поэтому на практике используют

методы синтеза, основанные на разложении

операции умножения на последовательность

простейших арифметических действий с

одноразрядными числами. Полагая, что в

двоичном представлении значения чисел

A иB

определяются выражениями

,

значения которого можно найти из таблиц

умножения либо путем выполнения умножения

для заданных значений аргументов. Однако

прямой логический синтез схемы умножителя,

основанный на представлении функции

выражениями в булевой алгебре, ввиду

громоздкости неэффективен. Исключения

составляют простейшие случаи перемножения

одноразрядных или двухразрядных двоичных

чисел. Поэтому на практике используют

методы синтеза, основанные на разложении

операции умножения на последовательность

простейших арифметических действий с

одноразрядными числами. Полагая, что в

двоичном представлении значения чисел

A иB

определяются выражениями

![]() и

и ![]() (1)

(1)

произведение

![]() можно записать в форме двойной суммы

можно записать в форме двойной суммы

![]() (2)

(2)

Группируя

члены с одинаковыми весовыми коэффициентами

![]() ,

преобразуем (2)

к виду

,

преобразуем (2)

к виду

![]() (3)

(3)

Из

полученной формулы (3) видно, что для

вычисления значения k-го

разряда произведения необходимо

выполнить совокупность произведений

одноразрядных чисел (![]() ,

,![]() ),

для которых сумма индексовi + j = k.

Затем надо последовательно складывать

эти произведения. При добавлении к сумме

новых слагаемых возможно появление

переноса в следующий k + 1-й

разряд. Поэтому при нахождении k-го

разряда произведения нужно к сумме

членов (

),

для которых сумма индексовi + j = k.

Затем надо последовательно складывать

эти произведения. При добавлении к сумме

новых слагаемых возможно появление

переноса в следующий k + 1-й

разряд. Поэтому при нахождении k-го

разряда произведения нужно к сумме

членов (![]() ,

,![]() )

добавить все переносы, получаемые при

сложении аналогичных членов для

предыдущегоk – 1

разряда.

)

добавить все переносы, получаемые при

сложении аналогичных членов для

предыдущегоk – 1

разряда.

Порядок,

в котором производится сложение

произведений (![]()

![]() )

и переносов из предыдущего разряда

значения не имеет.

)

и переносов из предыдущего разряда

значения не имеет.

Указанные

действия мы выполняем, производя

перемножение двоичных чисел на бумаге.

Так, вычисляя произведение десятичных

чисел

![]() 1)

делаем следующую запись:

1)

делаем следующую запись:

Штриховой

линией обведены произведения (![]()

![]() ),

для которых сумма индексовI + j = 4.

В результате сложения этих произведений

получаем значение 1. Однако после

прибавления переноса из предыдущего

третьего разряда

),

для которых сумма индексовI + j = 4.

В результате сложения этих произведений

получаем значение 1. Однако после

прибавления переноса из предыдущего

третьего разряда

![]() четвертый разряд результата

четвертый разряд результата![]() принимает значение 0 и формируется

перенос в следующий пятый разряд

принимает значение 0 и формируется

перенос в следующий пятый разряд![]() .

.

Арифметическое

перемножение одноразрядных чисел (![]()

![]() )

реализуется конъюнктором, поскольку

логическое умножение совпадает с

арифметическим.

)

реализуется конъюнктором, поскольку

логическое умножение совпадает с

арифметическим.

В качестве элементарной ячейки умножителя используют устройство, показанное на рисунке 4, а.

Рисунок 4 – Элементарная ячейка умножителя. Логическая схема (а) и символическое обозначение (б)

Операция, реализуемая такой ячейкой, задается выражением ab+c+d, где a, b, c и d – одноразрядные двоичные числа. Результат, получаемый на выходе ячейки, представляется одноразрядной частичной суммой S и переносом P.

Из

выражения (2) видно, что для нахождения

произведения

![]() требуется получитьmn

одноразрядных произведений (aibj),

по одному для каждой возможной комбинации

индексов i,

j.

Именно столько элементарных ячеек

требуется для построения умножителя.

Для наглядности представления структуры

умножителя элементарные ячейки на

структурной схеме целесообразно

изображать в символической форме, как

показано на рисунке 4, б. Поскольку

такое обозначение содержит в явной

форме сомножители ai,

bj,

участвующие в операции, реализуемой

ячейкой, то связи, предназначенные для

подведения к ячейкам этих сомножителей,

можно на структурной схеме умножителя

не обозначать.

требуется получитьmn

одноразрядных произведений (aibj),

по одному для каждой возможной комбинации

индексов i,

j.

Именно столько элементарных ячеек

требуется для построения умножителя.

Для наглядности представления структуры

умножителя элементарные ячейки на

структурной схеме целесообразно

изображать в символической форме, как

показано на рисунке 4, б. Поскольку

такое обозначение содержит в явной

форме сомножители ai,

bj,

участвующие в операции, реализуемой

ячейкой, то связи, предназначенные для

подведения к ячейкам этих сомножителей,

можно на структурной схеме умножителя

не обозначать.

Один из вариантов структурной схемы умножителя для m=n=4 показан на рисунке 5.

Рисунок 5 – Умножитель четырехразрядных двоичных чисел. Схема электрическая структурная

Каждый горизонтальный ряд элементарных ячеек выполняет умножение числа A на один из разрядов множителя B и суммирует полученное произведение с результатом аналогичной операции, реализуемой предыдущим (верхним) рядом. При этом частичная сумма с выходов элементарных ячеек верхнего ряда поступает на входы d элементарных ячеек следующего за ним ряда. Входы c использованы для приема переноса, возникающего при сложении произведений (aibj).

В результате сдвига вправо элементов каждого следующего горизонтального ряда по отношению к предыдущему на одну позицию в каждом столбце элементов сумма индексов сомножителей ai, bj, совпадает с номером к столбца и индексом разряда qk произведения, формируемого в этом столбце.

На суммирующие входы d самого верхнего горизонтального ряда элементов и на входы переноса c крайних левых элементов в каждом ряду подают нули. При этом на выходах элементов верхнего ряда формируется (n+1) – разрядная частичная сумма S0=Ab0. Младший разряд частичной суммы S0 является младшим разрядом q0 произведения AB, поскольку других произведений кроме a0b0, сумма индексов которых равна 0, нет. Более старшие разряды частичной суммы S0 складываются во втором ряду элементарных ячеек с произведением Ab1, формируя на выходах следующую частичную сумму S1, младший разряд которой является вторым по старшинству разрядом произведения q1. Аналогично формируются частичные суммы S2, S3, причем значение частичной суммы S3 определяет старшие разряды произведения (q3,…,q7).

Умножитель, построенный по схеме на рисунке 5, можно использовать как секцию умножителя с более высокой разрядностью.

Для определения быстродействия умножителя следует вычислить суммарное время выполнения операции умножения, которое определяется длиной критического пути прохождения сигнала со входа на выход. Для простоты длина критического пути оценивается максимальным числом элементарных ячеек, которые сигнал должен пройти от входного нулевого разряда сомножителя до старшего разряда результата. Для схемы, показанной на рисунке 5, длина критического пути в общем случае составляет n+2(m-1) и, следовательно, равна 10.

Таким образом, для определения суммарной задержки распространения сигнала в умножителе, необходимо определить задержку распространения сигнала в элементарной ячейке и умножить на длину критического пути. Задержка распространения сигнала в элементарной ячейке умножителя определяется суммой среднего времени задержки распространения сигнала в конъюнкторе и одноразрядном сумматоре.

Исходя из вышесказанного, суммарное среднее время задержки распространения сигнала в умножителе можно определить по формуле

![]() (4)

(4)

где

![]() – среднее время задержки распространения

сигнала одного конъюнктора, нс;

– среднее время задержки распространения

сигнала одного конъюнктора, нс;

![]() – среднее время задержки распространения

сигнала одноразрядного сумматора, нс.

– среднее время задержки распространения

сигнала одноразрядного сумматора, нс.

1.4 Методические указания по разработке разделов проекта к теме № 1

Синтез заданного счетчика выполните по методике, приведенной в приложении А.

Логическую схему четырехразрядного двоичного сумматора разработайте в основном базисе. Для этого на основании логических функций (5) и (8) запишите логические функции для выходов суммы S0…S3 и переноса C1…C4. Логическую схему вычертите в формате А3 и выполните указания раздела 4.

Как отмечалось выше, прямой логический синтез умножителя на практике не используется. Поэтому на основании структурной схемы умножителя (рисунок 5) разработайте логическую схему секции умножителя при n=4, m=2 (рисунок 6).

Рисунок 6 – Логическая схема секции умножителя при n=4, m=2

В логической схеме используйте четырехразрядные двоичные сумматоры. Для передачи переноса от одной элементарной ячейки к другой в каждом ряду структурной схемы умножителя (рисунок 5) в сумматорах имеются внутренние связи. На рисунке 6 указаны обозначения входных и выходных сигналов в соответствии со структурной схемой умножителя (рисунок 5).

На основании рисунков 5 и 6 разработайте логическую схему секции умножителя при n=4, m=4. Логическую схему вычертите в формате А4. На логической схеме обозначьте входные и выходные сигналы в соответствии с рисунками 5 и 6. Все надписи и обозначения сигналов выполните чертежным шрифтом 5.

Принципиальную электрическую схему устройства умножения разработайте на выбранных микросхемах на основе заданной структурной схемы (рисунок 1) и разработанной логической схемы умножителя. Принципиальную схему вычертите в формате А2 и выполните указания раздела 4 данных методических указаний.