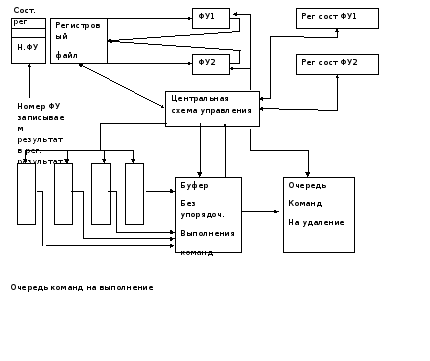

Идеология организации без упорядоченного выполнения

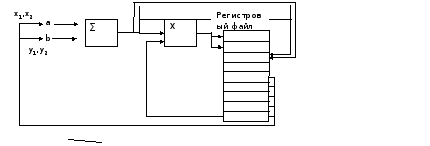

В свое время узел формирования адреса был вынесен из операционного блока, с той целью, чтобы освободить основной сумматор от вычисления адресов операнда и перенести в блок выборки команд, в котором в совокупности с КЭШ памятью команд организован законченный цикл подготовки операндов к выполнению операций над ними в операционном блоке. Таким образом сформировать 2х ступенчатый конвейер в процессоре.

Идеология без упорядоченного выполнения основана на предварительном анализе команд по возникновению конфликтов при их выполнении, задержки их выпуска по конвейер и пропуска внеочередных команд, которые могут быть беспрепятственно выполнены. Конфликты эти относятся в первую очередь к группе конфликтов по данным. Конфликты эти классифицируются по типу RAW и WAR, WAW.

Первоначально анализ возможного возникновения этих конфликтов проводился на стадии декодирования и вычисления операндов, в дальнейшем для реализации без упорядоченного выполнения формирование адресов операндов выделили в отдельную стадию конвейера с той целью, чтобы дать возможность пропускать на конвейер внеочередные команды, не вызывающие конфликты WAW и RAW, и не блокировать конвейер на первой стадии . Таким образом, стадия декодирования была разбита на два такта:

Такт выдачи

Такт чтения операндов

Такт выдачи стал контролировать ситуацию использования регистра результата в команде, предыдущими командами в качестве регистра результата (WAW – запись после записи) с целью избежать искажения при предыдущих команд. Если такая ситуация могла иметь место, то команда не выпускала на конвейер.

На этапе чтения операндов анализировать стали возможность возникновения RAW при выпуске команды на конвейер, т.е. операнды источники проходят проверку не являются ли они регистрами результата предыдущих команд, находящихся в стадии выполнения или в данный момент не происходит ли запись из функционального устройства по адресу источника в команде.

В связи с без упорядоченным выполнением, завершающую стадию конвейера, связанную с записью результата в регистровый файл, пришлось разделить на 2 части.

Это первая предварительная - стадия завершение.

Вторая – запись результата.

На этапе запись результата блок управления конвейером отслеживает возможность возникновения конфликтов типа WAR для того, чтобы исключить искажение значений в регистрах, используемых в качестве источников предыдущими командами, находящимися на стадии выполнения.

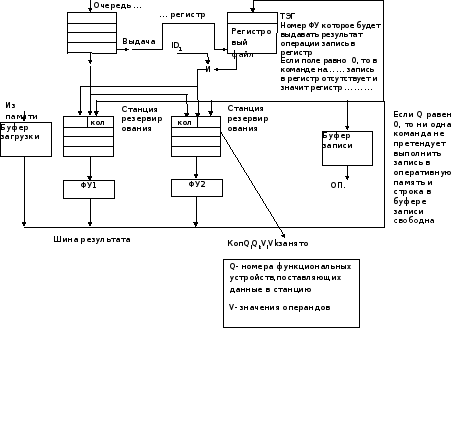

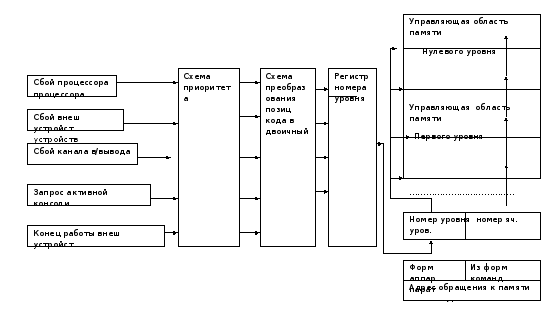

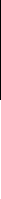

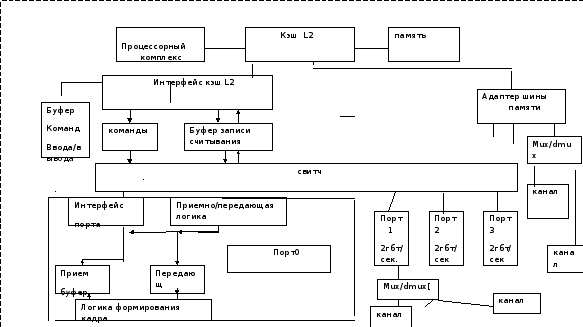

Как следует из представленной блок–схемы, централизованная схема управления осуществляет контроль за приемом команд во входную очередь, загружая их в буфер без упорядоченного выполнения. При готовности операндов и наличии свободных функциональных устройств централизованная схема управления передает команды им на выполнение и по завершении передает их в очередь команд на удаление ,соблюдая последовательность программного кода.

Алгоритм Томасуло

С одной стороны выделение чтения операндов в отдельную стадию конвейера наводит на мысль о возможности размещения узла формирования адресов операндов в глубину конвейера с целью его параллельной работы с другими функциональными блоками операционного устройства. В этом случае отпадает необходимость в начале конвейера держать буфер для команд ,ожидающих выполнения только при одном условии, если будут отсутствовать в системе конфликты RAW, которые контролирует эта стадия.

Одним из способов устранения конфликтов типа RAW-это наличие обходных цепей, когда результат сумматора передается на один из его входов в случае использования его в качестве источника в следующей команде. В этом случае в регистровом файле просто будут отсутствовать источники, которые могут быть прочитаны раньше чем попадет в них конечный результат, потому что все результаты ,которые будут использованы в следующей команде в качестве источника просто не будут записываться в регистровый файл. Следовательно, при использовании технологии без упорядоченного выполнения можно воспользоваться методом обходных цепей.

И так целесообразность перемещения узла чтения операндов в глубь конвейера будет только в том случае, если операционное устройство, имея блочную структуру, будет иметь для каждого функционального узла буфер команд, ожидающих выполнения; уже с готовыми операндами,, а блок чтения операндов имея свой буфер с адресами для операндов будет поставщиком операндов в эти функционального устройства.

Это во-первых, а во-вторых и основное промежуточные результат вычислений не будет передаваться в регистровый файл, а будет перемещаться из одного функционального устройства в другое или же в свое во входную очередь подобно архитектуре обходных цепей в сумматоре, а запись результата выполнения операции будет производиться только при завершении всех предыдущих команд при отсутствии конфликтов WAR, подобно как это делается при централизованном управлении при заключительной стадии конвейера «Запись результата».

Конфликты WAW, отслеживаемые при централизованном управлении просто будут отсутствовать, так как будет исключена ситуация циклов ранней преждевременной записи в регистровый файл в силу логики работы распределенных схем контроля за конфликтами.

Конфликты RAW при распределенной схеме управления конвейером не будут возникать же из-за того, что все циклы чтения промежуточных результатов из регистрового файла просто отсутствует, так как эти результаты будут подаваться непосредственно на исполнительное устройство из других функциональных блоков. .

Без обходных цепей в сумматоре … … С обходными цепями в сумматоре

ADD R1R2R3 ID EX WB ID EX

S

UB

R4R1R3

ID EX WB

ID EX WB

UB

R4R1R3

ID EX WB

ID EX WB

Невозможна одновременная запись и чтение в R1

конфликт просто не возникает т.к. результат ADD поступает на вход сумматоре для вычитания.

… ….

Вышеописанная технология реализует алгоритм Томасуло, основные принципы которого мы и отметим.

Но прежде чем сформулировать эти принципы рассмотрим еще способ устранения конфликтов типа WAR на конвейере. Таким является способ переименования регистров.

1

.R5=R1+R2

ID

EX

W

структурный конфликт:

регистр. файл занят;

.R5=R1+R2

ID

EX

W

структурный конфликт:

регистр. файл занят;

2

.R6=R0*R5

ID

EX

W

запись 2-ой команды

.R6=R0*R5

ID

EX

W

запись 2-ой команды

3

.R5=R3+R4

.R5=R3+R4

регистр R5 ЗАНЯТ 2ой командой запись не возможна

4

.R7=R0*R5

.R7=R0*R5

ID

EX

EX

W

RAW

конфликт поR5

между 1и 2 командами

ID

EX

EX

W

RAW

R5

занят 3ей

командой

ID

EX

EX

W

RAW

R5

занят 3ей

командой

5.R5=R1+R2

5.R5=R1+R2

6

.R6=R0*R5

IDEX

W

как видно из примера

переименование регистров

.R6=R0*R5

IDEX

W

как видно из примера

переименование регистров

7 .S1=R3+R4

ID

EX

W

увеличивает производительность

работы конвейера

.S1=R3+R4

ID

EX

W

увеличивает производительность

работы конвейера

8

.R7=R0*S1

.R7=R0*S1

ID

EX EX W

ID

EX EX W

ID

EX

EX

W

ID

EX

EX

W

Метод переименования регистров (пример)

Предположим, что необходимо вычисление (¬x + ¬y)c

¬x = ix1 + jy2; ¬x + ¬y=i(x1+x2) + j(y1+y2)

¬y=ix2 + jy2; c(¬x + ¬y)=ic(x1+x2) + c(y1+y2)j

Т.е. значение координаты нового вектора: c(x1+x2), c(y1+y2) которые будут помещены в регистровый файл.

Данные вычисления будут производиться на суперскалярном процессоре имеющего 2 конвейера: конвейер с фиксированной точкой (операции сложения) и конвейер умножения (множительное устройство)

Программа для выполнения:

ADD R5=R1+R2

MUL R6=R0*R5

ADD R5=R3+R4

MUL R7=R0*R5

Общая схема:

Анализ работы суперскалярного процессора с использованием переименования регистров показывает, что возможно окончание выполнения команд не в том порядке, как они расположены в программном коде т.е. на лицо внеочередное выполнение команд.

Для организации выдачи результатов в порядке определяющем программным кодом необходимо сохранять содержимое временных регистров до того времени, когда вся предыдущая команда закончит выполнение и будут удалены из конвейера. В течении времени пока временный регистр содержит данные он используется последующими командами как источник. Т.е. отсюда вывод: при суперскалярной архитектуре использование временных регистров необходим блок выходной очереди команд, который будет контролировать окончание выполнения команд в двух фазах:

Завершение

Запись результата

Удаляя с конвейера те команды, которые будут иметь статус второй фазы.

КОНВЕЙЕР очередь

завершенных команд Очередь

команд на удаление с конвейра

Р.Ф.

Входной поток

команд

…

памяти

КОНВЕЙЕР

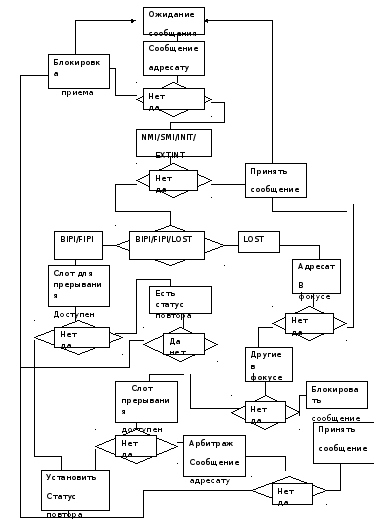

Одной из проблем без упорядоченного выполнения является ситуация возникающая при обработке прерываний, когда необходимо восстановить состояние процессора до начала выполнения команды, вызвавшей прерывание.

При последовательном выполнении команды этой ситуации не возникает, а так при без упорядоченном выполнении возможно окончание последующих, ранее предыдущих, а при выполнении предыдущих могут возникнуть прерывания, а исходные данные последующих может быть уже нельзя восстановить, вот тогда и возникает ситуация выход из которой можно найти

А) сохранение исходных данных команд, находящихся в буферах исполнительных устройств и всех команд в буфере очередности, контролирующего последовательность выполнения программного кода, имеющих статус “‘ завершение”.

Если возникнет прерывание, то состояние машины можно будет восстановить до точки предшествующей всем командам выполненным вне очереди

Б) сохранение всех результатов в буфере, который хранит новые значения всех команд, находящихся в состоянии “завершение”

В) выдавать команды на этап запись результата” ,если известно что все предыдущие команды выполнены без прерываний или, что ни одна из предыдущих команд не будет завершена пока не будет обработано прерывание.

Г) Хранить все адреса команд и сами команды, находящиеся на не выполнении в конвейере.

Предпосылки для внедрения технологии предсказания переходов

Безупорядоченное выполнение и механизм обработки прерываний в процессоре в этом случае, который восстанавливает состояние процессора после не одной, а возможно нескольких выполненных команд, наводит на мысль об использовании технологии предсказания переходов. Направлять поток выполненных команд на основе предсказаний, а в случае ошибки восстанавливать состояние процессора и начинать выполнение программы по адресу, сохраненному в процессоре, в случае ложного предсказания. Точно также как это осуществлялось при обработке прерывания, только вместо адреса перехода по прерыванию, используется адрес, по которому должно переходить выполнение программы в случае ложного предсказания. Но реализация идеи выполнения команд по предположению, так же как и без упорядоченное выполнение, требует внедрения дополнительных аппаратных средств в архитектуру, процессора и это в первую очередь будет буфер переупорядочивания,, который представляет дополнительные виртуальные ресурсы как и станция резервирования в алгоритме Томасуло. Буфер хранит промежуточные результаты от момента завершения операции до ее стадии “запись результата”.

Буфер является источником операндов для команд, точно так же как станция резервирования, обеспечивающая промежуточное хранение и передачу операндов в алгоритме Томасуло. После того как команда в алгоритме Томасуло записала результат в регистровый файл, он становится доступным для других команд. В случае выполнения команд с использованием механизма предсказания адреса перехода, запись в регистровый файл, производится только после получения результата условия, по которому должен быть произведен переход в программе. Только после этого все команды, следующие за командой перехода получают статус”запись результата” . Вот поэтому каждая команда имеет позицию в буфере переупорядочивания до тех пор пока она не получит статус “запись результата”., Результат помечается номером строки в буфере, а не номером станции резервирования. Вот почему станции резервирования ,получая данные из буфера, обязаны отслеживать номер строки, чтобы отправить результат операции в строку буфера из которого были получены исходные данные.

Заключение:

Блок операций в ЭВМ первых поколений, представляющий собой многофункциональное устройство все виды арифметических операций выполнял, используя операцию сложения и сдвиговые операции. С внедрением интегральных микросхем в элементную базу стали применять табличные методы, используя для этого специальные микросхемы ППЗУ, что значительно позволило сократить время выполнения операций умножения и деления в операционном блоке. С внедрением конвейерной обработки команд операционный блок стал представлять собой набор функциональных блоков, каждый из которых выполнял только ограниченный набор арифметических операций. Такая архитектура давала возможность в процессоре выполнение нескольких операций одновременно. Конвейерная обработка команд позволила значительно повысить производительность системы, но при этом перед разработчиками ЭВМ возникли новые проблемы, связанные с появлением конфликтов при обработке команд, которые стали причиной задержек в работе конвейера. Для того чтобы их устранить или уменьшить их влияние на функционирование конвейера, пришлось вводить дополнительные аппаратные средства в архитектуру процессора.

Один вид конфликтов (WAR) когда адрес регистра результата в команде используется как адрес источника в предыдущей был разрешен с помощью метода переименования регистров, суть которого заключалась в том , что при обнаружении вышеупомянутой ситуации запись результата в команде стали производить в альтернативный регистр, выполняющего функцию клона программного регистра, указанного в команде, чтобы не дожидаться выполнения предыдущей команды и не исказить ее результат. При удалении команды с конвейера данные из регистра-клона записывались в программный регистр, указанный в команде. Эта технология дала возможность увеличить производительность работы конвейера реализующего безупорядочное выполнение команд в процессоре. Без этого метода на конвейер выпускались вне очереди только те команды, которые не конфликтовали с предыдущими ни по адресам как источников в них так и по адресам записи результатов.

Другой тип конфликта(RAW) на конвейере стал возникать, когда очередная команда, поступающая на конвейер, должна дожидаться результата в предыдущей, потому что один из ее адресов источников имел то же значение что адрес регистра результата в предыдущей команде. Конфликт этот устранить нельзя, но время потерь сократить можно, подавая значение результата в операционное устройство, не записывая предварительно его в регистр результата.

Конфликт(WAW), появился в следствии безупорядочного выполнения команд на конвейере, когда результат последующей команды формируется раньше предыдущей. При использовании метода переименования регистров значение в регистре-клоне используется в промежуточных вычислениях, пока команда не удалена с конвейера. Команда может быть удалена с конвейера только в том случае, если все предыдущие выполнены и удалены с конвейера при этом предварительно производиться запись из регистра-клона в в программный регистр. Аппаратные издержки от этого конфликта заключаются в том ,что приходиться иметь буфер для команд, ожидающих выполнения всех предыдущих и дополнительные схемы контроля за состоянием фаз выполняемых на конвейере команд.

Для устранения конфликтов по управлению используются аппаратные средства блока предсказания переходов. Если при последовательном выполнении команд адрес очередного блока команд, загружаемого из памяти кэш команд или из памяти высшего уровня формируется с опережением то есть увеличением значения текущего адреса команды на величину длины блока команд, уже находящихся в буферных регистрах блока выборки команд, то при конвейерной обработке, чтобы сократить время простоя конвейера из-за конфликтов по управлению, связанных с выполнением команд переходов, адрес очередного блока команд, загружаемого из вышестоящего уровня памяти целесообразней формировать по значению адреса, указанного в команде перехода или следующего за ней на основании информации, собранной о переходах в предыдущих выполненных уже командах управления.

,

Алгоритм Томасуло

Основной идеей алгоритма Томасуло являлся отказ от централизованного управления функциональными устройствами с точки зрения связи с регистровым файлом на промежуточном этапе выполнения. Отказ от записи промежуточных результатов в регистровый файл т.е. тех, которые будут использованы в следующих командах, следовательно исключить конфликты типа RAW, и WAR, используя для этого во-первых, переименование регистров, во-вторых, станции резервирования.

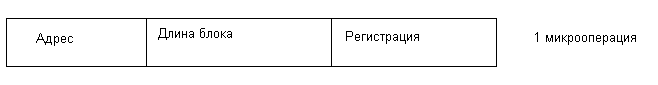

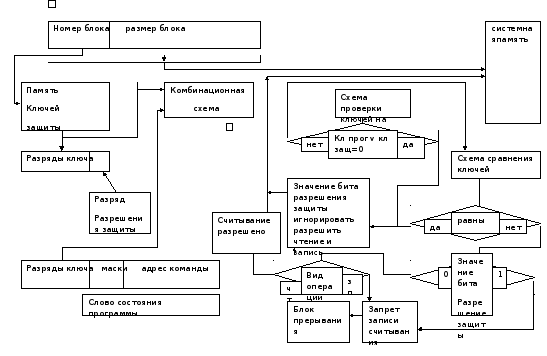

Станции резервирования представляют ячейки буферной памяти типа FIFO. Для каждого функционального устройства структура каждой станции состоит из информационной части и теговой.

Информационная часть содержит операнды, поступающие на обработку из:

А) регистрового файла

Б)из функционального устройства как и промежуточный результат

В) Из оперативной памяти

Теговая часть каждой строки в буфере памяти содержит 6 полей:

Поле операции

Поля, указывающие станции резервирования, которые будут вырабатывать соответствующие операнды источники, нулевые значения этих полей указывают, что операнды уже находятся в полях значения операндов.

Поле операнда

Номер станции резервирования

Номер станции резервирования

Значение 1го операнда

Значение второго операнда

Занято

Откуда должны подавать первый операнд

Откуда должен поступать второй операнд

2 поля операндов источника

Поле занято, указывает, что данная станция резервирования и соответствующее ей устройство заняты.

Регистровый файл и буфер записи имеют поле в котором указано функциональное устройство, которое будет вырабатывать значения для записи в регистр или память. Буфер записи имеют поле для записи значения операнда в память.

Аппаратура, реализующая алгоритм Томасуло, может быть расширена для обеспечения поддержки выполнения по предположению. С этой целью необходимо, как было отмечено выше, ввести фазу фиксации результата и фазу записи результата. Добавление к последовательности выполнения команды фазы фиксации требует сохранение всех команд закончивших выполнение и их результатов до момента пока не сформируется признак, по которому должен быть произведен переход. Вот почему без упорядоченное выполнение команд и механизм предсказания требуют одних и тех же аппаратных средств- дополнительного набора аппаратных буферов, которые хранят результаты команд, закончивших выполнение но еще не записавших результат в память или в регистровый файл.

Каждая теговая строка в буфере содержит 4 поля

Поле типа команды

Поле места назначения, по которому будет отправлен результат выполнения команды

Поле значения

Поле состояния команды(микрооперации)

Поле типа команды определяет является ли команда перехода, командой записи в память, или регистровый файл.

Поскольку каждая команда имеет позицию в буфере, до тех пор, пока она не будет зафиксирована и результат не будет отправлен в регистровый файл, результат выполнения команды хранится в строке с той же позицией. Все это время позиция строки, то есть ее адрес ,будет являться ссылкой для всех команд , использующих ее результат в свих операциях.

При выполнении по предположению запись в регистровый файл не производится до тех пор пока команда не не получит статус “запись результата”

Большое преимущество схемы Томасуло заключается в распределении логики обнаружения конфликтов и устранение приостановок ,связанных с конфликтами WAW и WAR. Это преимущество возникает из-за наличия станций резервирования, которые хранят промежуточные результаты вычислений и общей магистральной шины результата ,которая дает возможность одновременной загрузки результата в несколько станций в случае необходимости , таким образом давая возможность поступления нескольких команд, ожидающих этот результат, на выполнение из входной очереди в функциональные устройства в одном такте конвейера при условии ,что каждая станция резервирования имеет свою магистраль , связанную с входной очередью. Одновременное начало выполнения команд, ожидающих данные с магистрали результата, в функциональных устройствах возможно и при наличии одной магистрали загрузки команд из входной очереди ,если эти команды уже находятся в станциях резервирования функциональных устройств.

Впервые данная схема была предложена Томасуло при проектировании устройства с плавающей точкой. В дальнейшем его идея бала использована во многих архитектурах процессоров и стала базовой при проектировании в них блоков операций. Достаточно для этого привести пример архитектуры процессоров линейки Pentium на основе базовой модели P6. Именно в этой модели были использованы функциональные устройства с использованием станций резервирования, технологии безупорядочного выполнения микроинструкций, переименования регистров и предсказания переходов.

ЛекцияN8

Архитектура современных процессоров.

Анализ архитектуры современных суперскалярных процессоров показывает, что независимо от их аппаратной реализации базируются на общих архитектурных решениях.

1.Современный суперскалярный процессор имеет модифицированную гарвардскую архитектуру с конвейерной организацией выполнения команд.

2. Для устранения конфликтов, возникающих при выполнении команд на конвейере , используются общепринятые меры по их устранению:

- для устранения конфликтов по управлению, связанными с выполнением команд условных переходов в архитектуру процессора введен блок предсказания переходов. Который совместно с другими источниками в процессоре, формирующими адреса инструкций для выборки из кэш инструкций участвует в формировании окончательного значения адреса на приоритетной основе запросов, поступающих в устройство формирования следующего адреса для выборки очередного блока инструкций из кэш от всех источников, формирующих адреса инструкций.

- для устранения конфликтов в процессоре с без упорядочным выполнением используется технология переименования регистров на время выполнения команд в процессоре. Каждому программному регистру, являющимся регистром для записи результата в команде, в регистровом файле назначается группа альтернативных регистров, невидимых системе, в которые записываются промежуточные результаты и эти регистры являются источниками данных для команд, следующими за командами ,в которых была проведена операция переименования.

- все современные суперскалярные процессоры имеют распределенную схему управления, которая впервые была предложена и применена для выполнения операций с плавающей точкой в соответствии с алгоритмом Тумасулло. Данная архитектура дает возможность промежуточные результаты ,mполученные в одном операционном блоке направлять в случае необходимости в другой операционный блок без записи в регистровый файл или хранить в промежуточном буфере не завершенных команд и производить их запись только при условии выполнения предыдущих команд. Для этого пришлось поток команд на конвейере разбивать на группы и каждую команду сопровождать тегом, указывающим на принадлежность к группе.

-Операционные устройства в процессоре представлены набором независимых функциональных устройств, выполняющих определенный для них перечень операций. Эти устройства на входах имеют буферные памяти для приема команд из потока декодированных инструкций в соответствии с кодами операций для выполнения которых они предназначены, образуя таким образом входные очереди для выполнения.

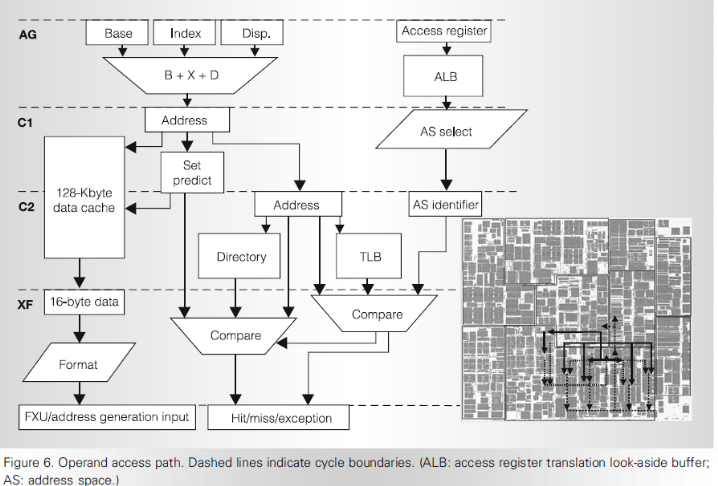

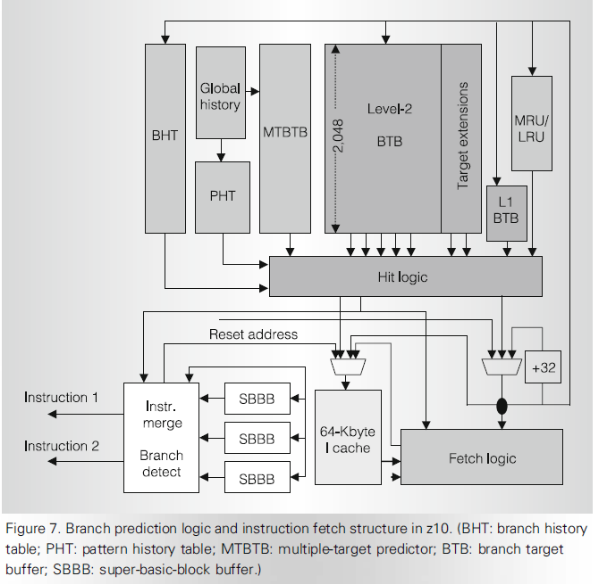

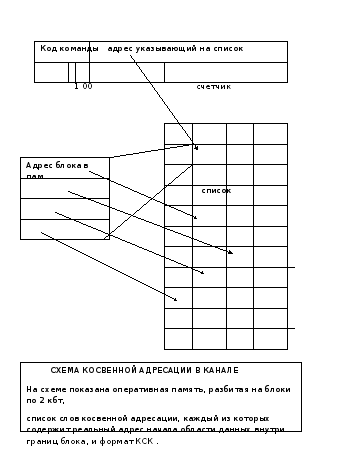

В качестве примеров рассмотрим архитектуры процессоров линейки PentiumфирмыINTEL, процессоровPower, процессоровZ990,Z10Zархитектуры фирмыIBM. Выбор обусловлен тем, что в них прослеживаются все этапы исторического развития архитектуры процессоров.

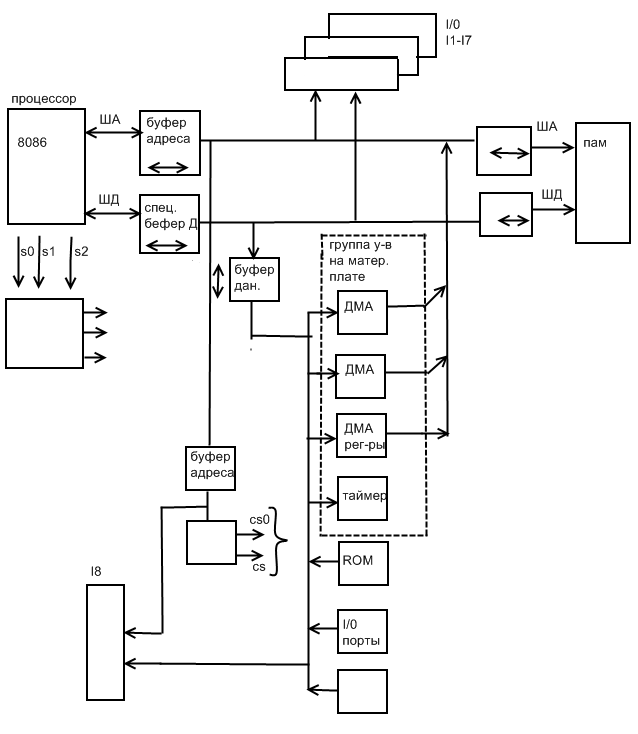

Появлению линейки процессоров предшествовала линейка процессоров х86,которая объединила процессоры первых четырех поколений и начала старт с процессора 8086, задавшего основу направлений архитектур последующих процессоров, архитектура которого используется в простейших микроконтроллеров в настоящее время. Линейка процессоров х86 разрабатывалась с учетом использования их в системах с шинной организацией, и первый процессор 8086 был 16- разрядный и имел 20ти-разрядную адресную шину. Выбор шинной организации связи процессора с другими компонентами системы был обусловлен назначением процессора в микро эвм и персональных компьютерах. Внедрение технологии сегментной адресации при обращении к оперативной памяти стало основой в дальнейшем для внедрения режима виртуальной памяти и механизма защиты, необходимого для поддержки многопрограммного режима в последующих модификациях не только этой линейки, но и линейки Pentium. Последней модификацией линейки х86,стал процессор 486,который по своим функциональным возможностям сопоставим с майнфреймами средней производительности. По своей архитектуре этот процессор был близок к модифицируемой гарвардской архитектуре, имел встроенную кэш память команд и данных, конвейер для обработки команд и отдельно встроенное устройство для обработки команд арифметических операций с плавающей точкой. Был разработан с учетом использования в многопроцессорных системах. Для реализации конвейерной обработки пришлось внедрить сложную систему декодирования инструкций, так как система команд, используемая в линейке процессоров, имелаCISCархитектуру, которая и потребовала введение дополнительных аппаратных средств для ее обработки.

Эстафету линейки процессоров х86 приняла линейка Pentium. Первым процессором в этой линейке стал процессорPentium,который был первым суперскалярным процессором, в составе было два конвейера, один из которых был универсальным, выполняющим любую инструкцию из системы команд ,а другой с ограниченными возможностями. Процессор имел блок предсказания переходов и операционный блок для выполнения инструкций классаSIMD. ПроцессорыPentium2,3 были спроектированы на базовой архитектуре процессораPentiumPro, в котором была реализована технология безупорядочного выполнения команд. Наличие операционных устройств с конвейерной организацией и буферных памятей для приема команд на исполнение, аппаратная реализация системы распределения команд в функциональные устройства в соответствии с кодами операций, наличие буферной памяти для хранения команд, ожидающих выполнения и диспетчеризации , а также буферной памяти для хранения команд выполненных ,но не имеющих признак завершения- все эти аппаратные средства обеспечивали технологию безупоряочного выполнения команд в процессоре. В этих процессорах была внедрена технология предсказания переходов и выполнение по- предложению ,то есть выполнение инструкций по направлению, выбранным блоком предсказания переходов не дожидаясь результата, полученного по окончанию выполнения команды перехода.

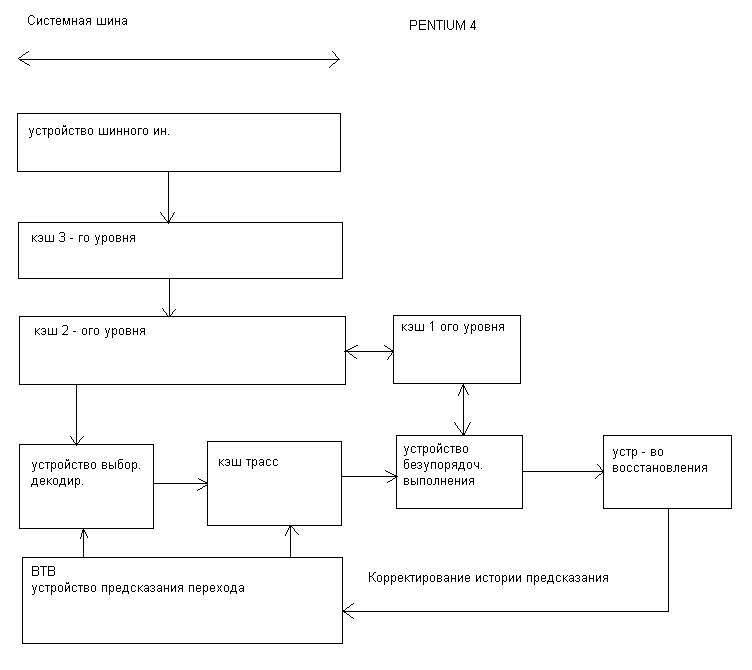

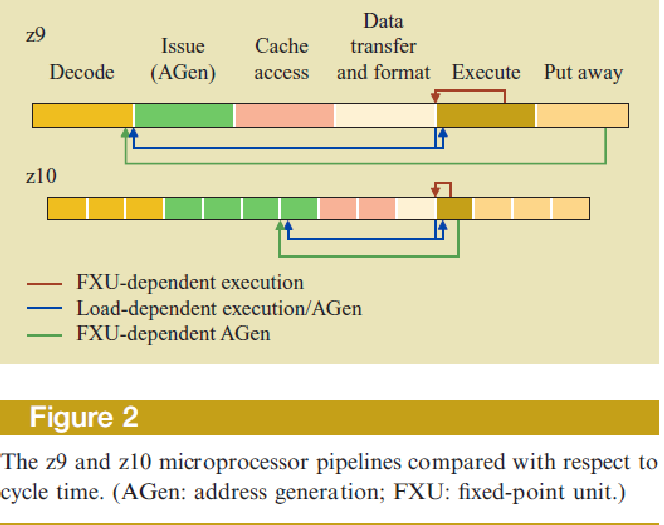

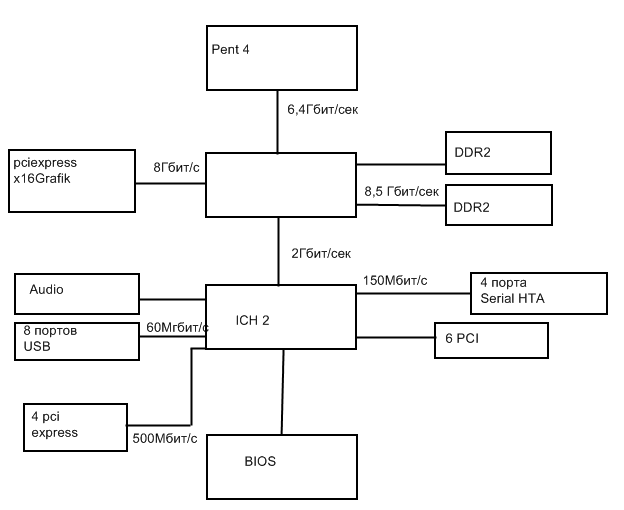

Особое внимание заслуживает архитектура Pentium4, в котором для выполнения команд используется кэш трасс, формируемая предварительно после загрузки инструкций в кэшL2 и с окончательной коррекцией во время выполнения в процессоре. Большинство процессоров этой линейки поддерживают мультипроцессорный режим работы.

Начало разработки линейки процессоров PowerфирмыIBMбыло положено в 1990 году. Процессоры этой серии относятся к классуRISCпроцессоров, предназначенных для конвейерной обработки команд. В предлагаемых к рассмотрению архитектурах процессоровPower4,5,6 реализованы все технологии конвейерной обработки команд, а в процессорахPower5 и 6 имеется аппаратная поддержка многопоточного режима и организации логических партиций на уровне операционной системы. Мы уже отмечали ,что во всех суперскалярных процессорах проводится на этапе декодирования инструкций формирование групп команд с целью контроля за выполнением команд на конвейере. Так вот архитектураPower6 интересна тем, что эта процедура вынесена за пределы конвейера и выполняется после загрузки команд в кэшL2 подобно тому, как вPentium4 формируется предварительно кэш трасс. Линейка процессоровPower(Power4,5,6) поддерживает организацию мультипроцессорного режима, используя для этого непосредственные связи между процессорами, технологию характерную для процессоров фирмыIBM, при организации узловSMP, а для объединения узлов в большие многопроцессорные системы используются как магистрали, так и технология непосредственных связей. ПроцессораZ990 иZ10 являются представителямиZархитектуры, которая стала дальнейшим развитием архитектуры майнфреймовIBM360 И 370. Процессора этого класса относятся кCISCпроцессорам, получившим в наследство систему команд от майнфреймовIBM360 и 370. Так процессораZ990 иZ10 по этой причине, чтобы не усложнять структуру конвейера не используют безупорядочное выполнение команд. В процессореZ10 используется конвейер с большим количеством ступеней, что дало возможность повысить частоту работы процессора до 4,4 ггц по сравнению с частотой процессораZ9,имеющего рабочую частоту 1,9ггц. Еще одной особенностью этой линейки процессоров является наличие совершенной системы контроля ,восстановления и диагностики на микроархитектурном уровне. ПроцессораZархитектуры используют технологию непосредственных связей с другими объектами системы, а для контроля за состоянием системы и сбора информации о состоянии процессора и выполнения процедур диагностики разработана система управления, реализуемая в сервисном процессоре, который имеет доступ ко всем основным узлам не только в процессоре ,но и ко всем другим объектам в компьютере, используя для этого внутреннюю сеть.

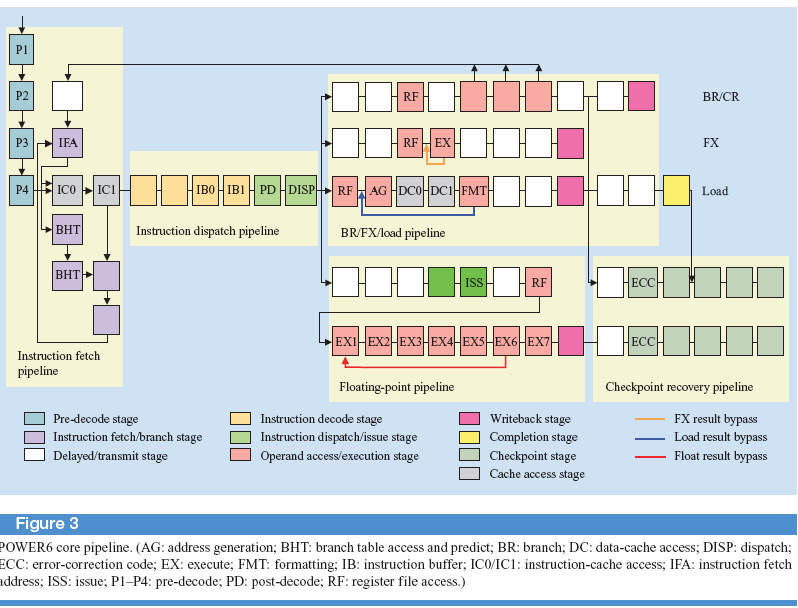

Архитектура процессора Pentium Pro

(PentiumPro) ставший в свое время базовой для процессоровPentium2 и 3. Микроархитектура этого процессора содержит аппаратные средства, обеспечивающие конвейерную обработку команд и всех ситуаций, возникающих при этом, ранее нами рассмотренных аппаратными средствами.

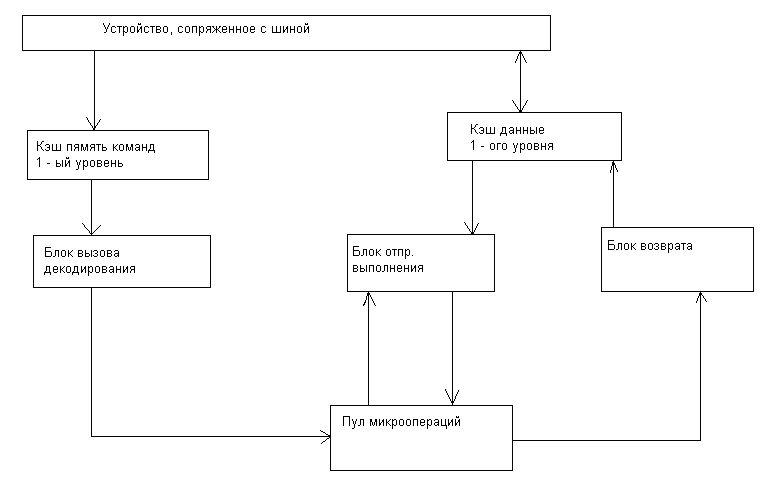

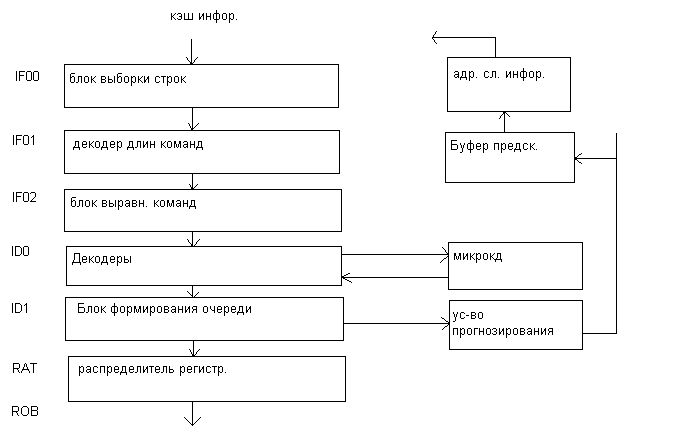

Как видно из блок схемы процессор содержит 3 отдельных независимых функциональных блока, обеспечивающих 3х фазную обработку команд.

А) выборка

Б) выполнение

В) завершение

Эта классическая структура применялась и ранее в предыдущих поколениях различных микроархитектур, с той лишь разницей, что для CISCмоделей эти функциональные блоки были связаны воедино во время выполнения отдельной команды. Наличие кэш команд и данных 1 ого уровня является признаком модифицированной Гарвардской архитектуры, обеспечивающей совмещение выполнения выборки очередной командыcвыполнением предыдущей. Эта технология была использована и ранее, к примеру, в наших отечественных моделях (ЕС 1045 и др.).

Микроархитектура блока декодирования имеет классические элементы, присущие любой системе, будь то жесткая логика или микропрограммное управление и предназначены для дешифрации команд и задания алгоритма обработки команд в процессоре. Но с другой стороны каждый блок имеет свои особенности, связанные со структурой и форматами команд, поступающих на обработку. Так в рассматриваемой архитектуре . команды имеют сложную структуру, которые разрабатывались без учета конвейерной обработки еще в предыдущих моделях (CISC).

Поэтому для сохранения преемственности программного обеспечения пришлось разрабатывать сложные декодеры, преобразующие СISCкоманды в набор микроопераций, представляющих по сутиRISCкоманды. Для решения этой задачи пришлось разрабатывать достаточно сложные декодеры и организовывать многостадийный конвейер в рамках блока. Как мы уже говорили ранее, что формат команд, используемых в микропроцессорах класса х86 и в последующих разработках на базовой моделиP6,

кроме поля кода операции имеет поле байта-модификатора в которых содержится вся информация о структуре команды, ее длине и способах адресации операндов, которая и служит исходной информацией для разработки аппаратных средств декодеров..

По сути, о чем мы сейчас говорили это классическая функция блока декодирования по преобразованию команды в набор микроопераций. Тогда же в чем же особенность?

А особенность заключается в том, что в CISCархитектурах микрооперации, выполняющиеся последовательно одна за другой функционально связаны, как и команды в программном коде, адрес текущей определяет адрес последующей. В данном же решении микрооперации выходящие из декодера сохраняются в промежуточном буфере, становясь доступными группе исполняющих устройств, для которых они предназначены независимо от принадлежности команд в программном коде.

Возникает вопрос? А как же строгая последовательность программного кода. А для этого декодер на этапе декодирования связывает в цепочку микрооперации, принадлежащие одной команде, для того чтобы в процессе выполнение команды считать выполненной, когда все микрооперации в цепочке устанавливают флаг статуса «выполненных». А так как в случае беспорядочного выполнения возможно и внеочередное выполнение команды, команда удаляется из процессора только в том случае, если предыдущие команды выполнены.

Именно чтобы обеспечить эту функцию аппаратными средствами используется буфер микроопераций, в котором микрооперации записываются и удаляются в строгой последовательности согласно программному коду.

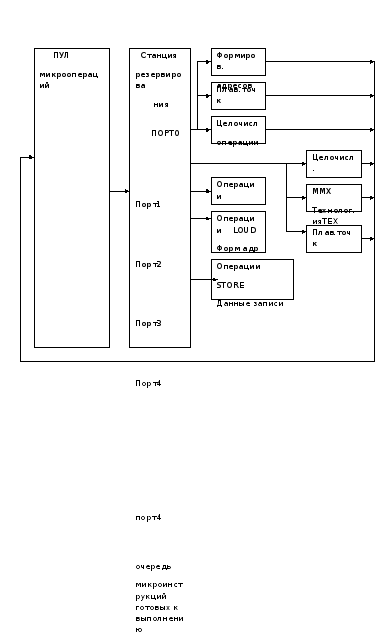

Как видно из блок схемы буфер микроопераций (пул микроопераций) является связывающим звеном между тремя основными блоками в процессоре. Он представляет адресуемую память, состоящую из 40 регистров. Он содержит микрооперации ожидающие выполнения, а также те, Которые уже выполнены, но не получили статус удаления из буфера «фиксация». Устройство диспетчера может выбирать для выполнения, как уже упомянуто выше, любую микрооперацию при готовности операндов и наличии свободного функционального устройства для их обработки Максимально 2 физических регистра со статусом завершения (удаления) могут быть прочитаны в каждом цикле. А теперь кратко о стадиях конвейера блока выборки декодирования. Наличие 3х стадий IF0,IF1,IF2 на этапе выборки объясняется следующими причинами.

выборка из кэш (32 байта кода программ.)

определение начала команд, их длина в области 32 байта (дешифрация кода команды и байта модификатора)

этап выравнивания. Т.к. декодеры работают с жестко распределенными полями в формате команды.

Команда, поступающая из декодирования должна быть выровнена на начало границы ввиду того, что в границах 32х байта считанных их кэш может начинаться не обязательно с 0 – ого байта.

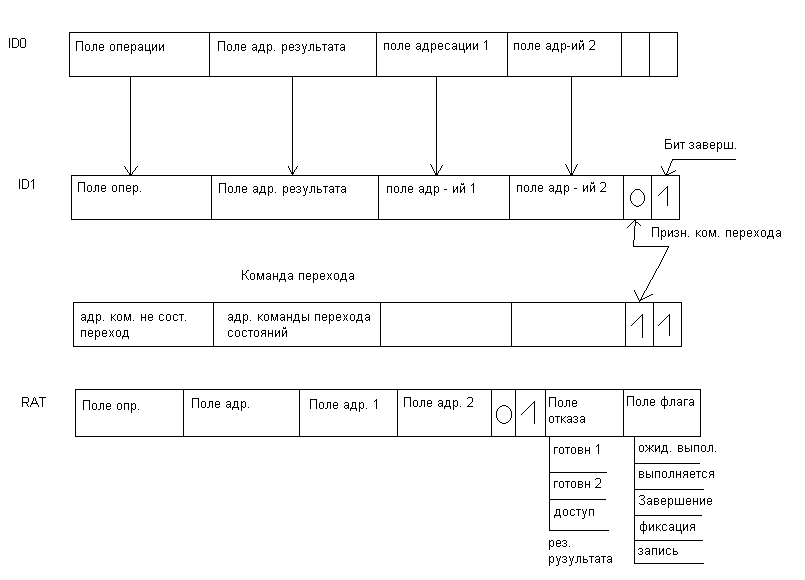

Этап декодирования включает 2 стадии: ID0,ID1.

Первая собственно предназначена для формирования форматов микроопераций.

Вторая для выстраивания очереди микроопераций.

Блок формирования очереди работает следующим образом:

Получив микрооперацию от декодера, он контролирует прием бита «завершения» из декодера в каждой следующей микрооперации и при получении его устанавливать признак конца цепочки, таким образом, связывая все микрооперации относящиеся к одной команде.

На этой же стадии конвейера получая от декодера признак команды, в случае обнаружения команды перехода формируется адрес следующей команды

с учетом, что переход назад более вероятен, чем вперед, на случай если блок предсказания не имеет другой информации о направлении перехода.

Блок декодирования имеет в своем составе 3 декодера, 2 предназначены для декодирования «простых» команд и один «сложный», декодирующий как простые, так и сложные команды. При работе декодеров имеется своя специфика. Если «сложный» декодер захватывает сложную команду, за которой следует «простые» две команды, то работают все декодера. Если же идет простых 3 команды, то 3 декодера работают одновременно и выдают в одном такте 3 микрооперации.

4 – 1 – 1 (6 микроопераций)

1 – 4 – 1 (2 микрооперации)

1 – 1 – 1 (3 микрооперации)

Этап RAT.

На этой стадии конвейера поддерживается переименование регистров (логических) программных в физические для исключения конфликтов WARиWAW. Реальные программные регистры могут быть заменены в микрооперации любым из 40 внутренних, находящиеся в буфере.

Кроме того, на этой стадии к коду микрооперации добавляется поле статуса и поле «флагов», после чего микрооперации поступают в пул микрооперации, поле микрооперации дополняется разрядами для хранения значений самих операндов.

С

сост

Устройство выборки (декодирования)

Пул инструкций.

Пул инструкций принимает поток микроопераций, определяемый программным кодом. Он представляет адресуемую память, состоящую из 40 регистров. Он содержит микрооперацию ожидающую выполнения, а также те, которые уже выполнены, но не получили статус «фиксации». Устройство диспетчеризации может выбирать для выполнения любую микрооперацию при готовности операндов. Максимально 2 физических регистра со статусом завершения могут быть прочитаны в каждом цикле.

Устройство диспетчеризации / выполнения.

Устройство диспетчеризации / выполнения является устройством безпорядоченного выполнения, которое диспетчеризирует и выполняет согласно зависимости данных и доступности ресурсов. Выбор и диспетчеризация микроопераций из пула инструкций управляется станцией резервирования. Она постоянно сканирует пул инструкций с целью поиска микроопераций готовых для выполнения. Т.е. все источники – операнды доступны и диспетчеризация их к доступным устройствам.

Результат выполнения микрооперации возвращается в пул и хранится совместно и микрооперациями до тех пор, пока не обработаются устройством восстановления.

Процесс выполнения и диспетчеризации является классическим процессом безупорядоченного выполнения, где микрооперации обрабатываются в соответствии с готовностью данных и наличия ресурсов без учета порядка следования в программе.

Когда 2 или более микрооперации одного типа претендуют в одно и тоже время на один ресурс, они выполняются в порядке FIFOпоступления в пул.

Исполнение микрооперации осуществляется двумя целочисленными устройствами, двумя устройствами с плавающей точкой и одним устройством обращения к памяти, позволяя диспетчеризовать до 5 микроопераций за такт. Устройство формирования адресов для команд перехода промахи перехода и сигнализирует BTBпроизвести перезагрузку конвейера. Устройство связи с памятью управляет микрооперациями «Загрузка» и «Запись». Для чтения из памяти достаточно одного адреса, поэтому эта операция декодирует в одну микроперацию. Запись декодируется в 2 микрооперации (адрес/данные).

Блок обработки с изменением последовательности.

Основная задача этого блока осуществлять контроль за состоянием микрооперацией находящейся в пуле инструкций и по мере их готовности к выполнению в других устройствах помещать их для выполнения. Попав в пул, микрооперация становится доступной

Для выполнения в функциональных устройствах, о чем свидетельствует бит «готовности» в поле типов микрооперации. Длина очереди 20 элементов.

Диспетчер распределяет микрооперации по портам, которые связаны с функциональным устройством. При этом каждый порт имеет свои собственные очереди, в виде FIFO.

Некоторые функциональные устройства разделяют один порт, который является мультиплексным. Может случиться так, что в такте будет несколько микроопераций, претендующих на обработку. В этом случае вступает механизм приоритета, учитывающий «важность микрооперации» и ее момент поступления в ROB(пул инструкций). Так, например микрооперация перехода считается важнее, нежели микрооперация обработки целых чисел.

Микрооперация, попав в порт после обработки в функциональном блоке «возвращается» в пул инструкций, получая статус «выполнена». Функциональный блок должен «знать» адрес регистра в ПУЛе, значение которого должно сопровождаться инструкцией.

Т.е. являться тегом ее в процессе всей обработки. Исходя из стадий конвейера, который реализует работу блока, а их 3. Можно предположить, что:

1) ROBявляется полностью ассоциативной памятью.

2) для выдачи микроопераций в станцию резервирования в ROBучаствуют только регистры с меткой «очередь» (стадия резервации).

3) Поиск осуществляется по коду операции или нескольких их возможных значений.

4) Каждый порт для организации связи с ячейкой ROBимеет магистраль, на которую выходит регистрыROBа. Только в этом случае поиск может быть осуществлен за один такт и эти же регистры могут выдать информацию в порт в следующем такте. Для возвращения результата вROBфункциональные блоки ы также должны иметь собственные магистрали для записи результатов вROB.

Основное назначение блока восстановления.

Основное назначение блока восстановления - отправлять результаты спекулятивного выполненных микроопераций в машинные регистры, адресуемые в программном коде или в ячейки оперативной памяти. Т.е. следить за выполнением микрооперации в пулtинструкций и записывать результаты их выполнения строго согласно программному коду.

Для этого подобно станции резервирования блок восстановления постоянно контролирует состояние микрооперации в пуле инструкций, просматривая, чтобы они были выполнены и не имели бы зависимости от других микроопераций в пуле, прежде чем фиксировать их окончательные результаты в процессоре, учитывая при этом наличие прерывания исключений и условие перехода.

Устройство восстановления способно восстанавливать до 3х микроопераций в такт, после того , как результаты микрооперации зафиксировали в машинных регистрах , они удаляются из пула. Подобно блоку отправки / выполнения конвейер блока восстановления имеет 3 стадии.

Анализ выполнения операции

Запись результатов в машинные регистры

Удаление выполненных микроопераций.

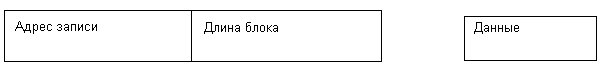

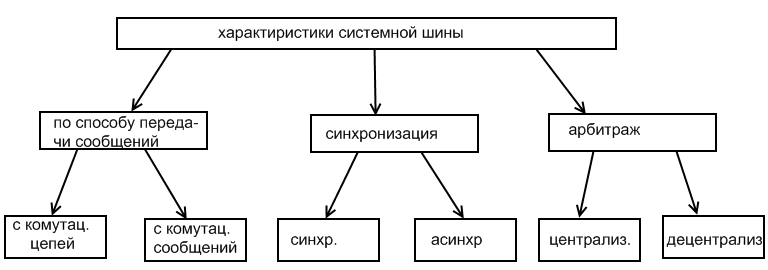

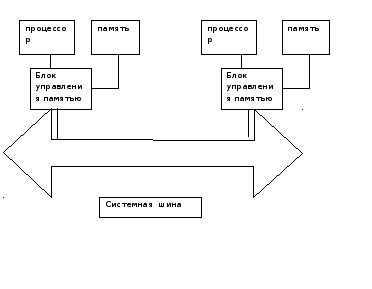

Устройство сопряжения с шиной предназначено для связи процессора с кэш памятью 1 ого и 2 ого уровня и системной памятью. Связь с кэш 1-ого уровня осуществляется для кэш данных и кэш команд, осуществляя реализацию модифицированной гарвардской архитектуры. Связь с памятью 2 ого уровня осуществляется по отдельной шине 64 бит. Системная шина представляет собой группы сигналов независимых. функционально друг от друга, тем самым, обеспечивая конвейерную организацию. Для обеспечения конвейерной организации устройство шинного интерфейса содержит буфер запросов к памяти, состоящей из очередей по записи и чтению. Данный буфер обеспечивает, например выполнение запросов чтения, давая возможность «обгонять» операциям чтения, операции записи, тем самым осуществлять спекулятивное чтение данных, то есть доставляя их заранее в процессор.Следует отметить запись осуществляются только строго в программной последовательности.

С учетом безупорядоченного выполнения и чтения как следствие данного режима устройство сопряжения с шиной или «записи/чтения» должно обеспечивать следующие условия:

1) Запись никогда не выполняется спекулятивно

2) Запись выполняется только в программном порядке

3) Операции записи диспетчеризуются только когда адрес и данные доступны и нет более старшей записи, ожидающей диспетчеризации

4) Запись может быть блокирована, чтобы дать возможность ее обходить операциям чтения.

5) Возможность «спекулятивного» выполнения чтения когда более младшая операция чтения обгоняет старшиеперации чтения .

Для реализации чтения необходимо:

Для записи

В связи с этим каждому входу очереди запросов на запись соответствует

Очередь SRQ– содержит адрес записи

Очередь SDQ– содержит данные записи

Для очереди на чтение соответствующей очереди LRQ

Вход SDQсодержит результат, который должен быть записан после того, как все предыдущие микрооперации в пуле будут в фазе завершения, как только будет разрешение их удаления данные должны быть записаны в память.

Архитектура процессора Pentium4

Если кратко характеризовать архитектуру Pentium4 можно отметить следующее.

Процессор Pentium4 также как и Р6 состоит из 3х основных функциональных блоков:

устройство предварительной обработки инструкций в порядке их следования в программном коде. Результатом работы этого блока является последовательность микроопераций, поставляемые в исполнительном блоке.

блок выполнения микроопераций реализующий алгоритм безупорядоченного выполнения.

блок завершения.

Основное отличие от Р6, это наличие кэш трасс, представляющие память декодированных инструкций т.е. микрооперации, которые читаются из кэш трасс в буферах исполнительного устройства.

Как и в Р6 микрооперации формируются по коду выполнения программы, с той или иной лишь разницей, что эту работу блок предварительной выборки производит заранее и накапливает их в памяти. При этом работает блок предсказания перехода, который выбирает направление выполнения программы и как бы «сшивая» единую последовательность микроопераций, устраивая не только безусловные переходы, но и условные на основании данных в блоке предсказания.

Если при декодировании встречается «сложная» инструкция то как и в Р6 используется постоянная память ROM, в которой уже находиться последовательность микроопераций данной инструкции. При этом эти микрооперации не вставляются в кэш трасс и ставятся на место инструкции «заплатка» - указатель /адрес на место нахождения последовательности микроопераций вROM.

В случае «промаха» в кэш трасс инструкции выбираются из более высокого уровня памяти. Декодируются таким образом поколения кэш трасс. Такая операция формирования сегмента кэш трасс занимает от 10,15 ти тактов до 30 ти т.е., «скрытый участок» конвейера достаточно сложная операция т.к. она проводится заранее и имеет большую «емкость» кэш трасс. Эти издержки вполне допустимы.

Сравним количество стадий конвейераустройства выборки/декодирования (без учета формирования очередной линейки кэш трасс) 8 по отношению к 7 стадиям в Р6. Кэш трасс представляет как бы память микропрограмм, формируемая динамически в процессе работы в процессоре и дает возможность многократно выполнять не только повторяющие инструкции но и целый сегмент программного кода.

Так на что же расходуются эти 8 стадий?

Первые 4 такта – извлечение последовательности из кэш трасс и предсказание перехода. Первый раз уже блок формирования адреса перехода выполняет свою функцию при формировании трассы но т.к. от этого момента до выполнения в процессоре проходит достаточно времени и блок предсказания переходов может иметь обновленные данные о ходе выполнения программы , то для «корреляции» в текущем моменте блок активизируется вторично. 1 такт уходит на буферизацию микроинструкции после чтения из кэш трасс и еще 1 такт чтобы выбрать «тройку» микроинструкций из очереди подготовить для нее ресурсы процессора. 2 такта уходит на замену логических регистров в микроинструкциях временными физическими из таблицы замены регистров.

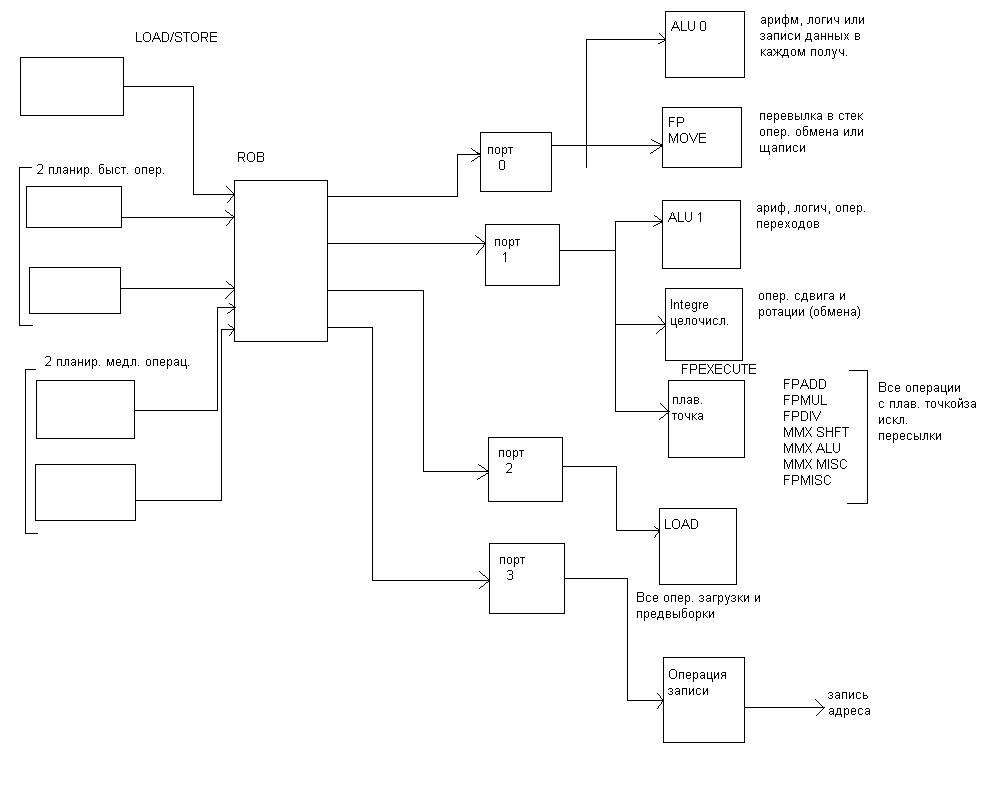

Функциональные исполнительные устройства в Pentium4

После того как инструкция поступила в пул инструкций, процессор начинает распределять их по соответствующим исполнительным устройствам.

Принцип такой же как и в Р6, но имеет свои особенности.

Во первых, если в Р6 выполнение всех микроинструкций на стадии резервирования управляется одним планировщиком, то в Pent4 таких планировщиков 5, которые «разбирают» микроинструкцию в пуле. Все микрооперации обращения к памяти формируются в отдельную очередь, которую контролирует отдельный планировщик (16 микроопераций).

Все другие формируются в другую очередь, которая управляется 2 мя «быстрыми» и 2 мя «медленными» планировщиками. Всеми простыми арифметически-логическими операциями управляют быстрые планировщики, которые распределяют по 2 микроинструкци за такт.

Вторая особенность - микроинструкции отправляются выполняться на исполнительное устройство к тому моменту времени, когда должны поступить операнды из кэш. Если в Р6 схема обработки выглядит так:

В Pentium4 работают 2 независимых планировщика со своими микрооперациями, согласовывая (синхронизируя) между собой свои действия.

Например. планировщик распределяя микроинструкцию LOADобращаясь за операндом в память, обязан сообщить всем остальным о постановке ее в очередь.. Планировщик, управляющий операцией сложения, в которой участвует этот операнд из памяти обязан поставить в очередь и отправить микрооперацию в исполнительное устройство с задержкой с таким расчетом, чтобы к появлению данных из кэш на шине микроинструкция была в исполнительном устройстве. Это теоретически. На самом деле чтобы избежать критической ситуации, когда данных не будет в кэш, конвейер исполнительного устройства имеет аппаратные средства повторить микроинструкцию, используя дублирующую копию микроинструкции, которая продвигалась параллельно по дублирующему псевдоконвейеру, не подвергаясь обработке в функциональном устройстве. Это делается‘ с той целью чтобы в случае промаха возвратить микроинструкцию на основной конвейер для повтора.

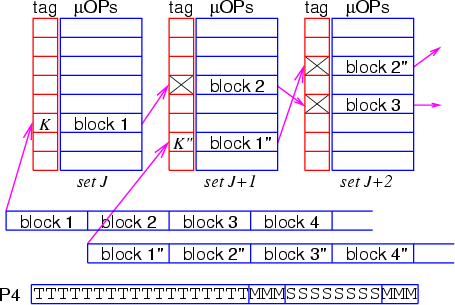

Архитектура кэш трасс

Кэш состоит из блоков размером в 6 "ячеек"

для размещения микроинструкций. Обычно

МОП занимает одну ячейку Т-кэша. Однако

в случаях, когда МОП соответствует

x86-инструкции, содержащей литеральную

константу либо непосредственный адрес

(смещение), и длина значимой части этой

константы превышает 16 разрядов, требуется

дополнительное место для размещения

недостающей информации. В ряде случаев

место может быть выделено в соседних

ячейках при условии, что поле литеральной

константы в этих ячейках не занято. При

отсутствии такой возможности выделяется

дополнительная ячейка. В этом случае

обе ячейки, составляющие МОП, должны

размещаться в одном блоке кэша. Кроме

того, если x86-инструкция состоит из

нескольких МОПов (до 4-х), то все эти МОПы

должны также размещаться в одном блоке.

Существуют и некоторые другие ограничения

на размещение МОПов.

![]() Темп

последовательного чтения из Т-кэша

составляет 1 блок за 2 такта, или 3 МОПа

за такт - что находится в соответствии

с темпом декодирования и отставки

микроинструкций, а также их обработки

на некоторых

Темп

последовательного чтения из Т-кэша

составляет 1 блок за 2 такта, или 3 МОПа

за такт - что находится в соответствии

с темпом декодирования и отставки

микроинструкций, а также их обработки

на некоторых![]() промежуточных

стадиях.

Объём Т-кэша составляет 12K

ячеек, или 2048 блоков, организованных в

256 наборов по 8 блоков. Для преобразования

программного адреса первой x86-инструкции

в каждой трассе (как правило, это

инструкция, на которую производится

переход) в положение первого блока

трассы (заголовка трассы) в кэше

используется комбинированный алгоритм,

сочетающий прямую адресацию по нескольким

разрядам программного адреса инструкции

с ассоциативным поиском. Разряды этого

адреса b10-3 указывают номер набора, а

нахождение требуемого блока в наборе

осуществляется сравнением остальных

разрядов адреса (ключа) с соответствующими

разрядами адреса (тэгами), хранящимися

для каждого блока в наборе. Для ускорения

поиска сначала происходит сравнение

нескольких разрядов ключа с соответствующими

разрядами тэга - мини-тэгом. Мини-тэг

включает в себя 6 разрядов - b13-11 и b2-0. При

нахождении блока с требуемым мини-тэгом

происходит выборка инструкций с

одновременной проверкой оставшейся

части тэга.

промежуточных

стадиях.

Объём Т-кэша составляет 12K

ячеек, или 2048 блоков, организованных в

256 наборов по 8 блоков. Для преобразования

программного адреса первой x86-инструкции

в каждой трассе (как правило, это

инструкция, на которую производится

переход) в положение первого блока

трассы (заголовка трассы) в кэше

используется комбинированный алгоритм,

сочетающий прямую адресацию по нескольким

разрядам программного адреса инструкции

с ассоциативным поиском. Разряды этого

адреса b10-3 указывают номер набора, а

нахождение требуемого блока в наборе

осуществляется сравнением остальных

разрядов адреса (ключа) с соответствующими

разрядами адреса (тэгами), хранящимися

для каждого блока в наборе. Для ускорения

поиска сначала происходит сравнение

нескольких разрядов ключа с соответствующими

разрядами тэга - мини-тэгом. Мини-тэг

включает в себя 6 разрядов - b13-11 и b2-0. При

нахождении блока с требуемым мини-тэгом

происходит выборка инструкций с

одновременной проверкой оставшейся

части тэга.![]() На

Рис. 4 приведён пример отображения

последовательных блоков инструкций на

наборы классического I-кэша, а на Рис. 5

показана организация хранения трасс в

Т-кэше. Также показана структура

программного адреса первой инструкции

в трассе при доступе к первому блоку

трассы в Т-кэше. Буквами S обозначены

разряды номера набора, буквами M - разряды

мини-тэга, и буквами T - разряды оставшейся

части тэга.

На

Рис. 4 приведён пример отображения

последовательных блоков инструкций на

наборы классического I-кэша, а на Рис. 5

показана организация хранения трасс в

Т-кэше. Также показана структура

программного адреса первой инструкции

в трассе при доступе к первому блоку

трассы в Т-кэше. Буквами S обозначены

разряды номера набора, буквами M - разряды

мини-тэга, и буквами T - разряды оставшейся

части тэга.![]()

![]()

![]() Рис.

Пример отображения последовательных

блоков инструкций на наборы

Рис.

Пример отображения последовательных

блоков инструкций на наборы

![]() классического

I-кэша (все блоки имеют одинаковые старшие

разряды адреса

классического

I-кэша (все блоки имеют одинаковые старшие

разряды адреса![]() и,

как следствие, соответствующие им наборы

кэша имеют одинаковые тэги)

и,

как следствие, соответствующие им наборы

кэша имеют одинаковые тэги)

![]()

![]()

![]() Рис.

Организация хранения трасс в Т-кэше

Рис.

Организация хранения трасс в Т-кэше

Краткая характеристика Power4.

Начало направления RISCархитектурыIBMбыло положено сRISCSystem6000 в 1990

Являющейся приемственником серии eServerpSeries.

Начальная модель процессора функционировала в области частот от 20Мгц до 30Мгц. В 1993 году pow2 был разработан, работающ. В области частот от 55Мгц до 71,5Мгц и выполняет до 6 инструкций за цикл (такт).

Параллельно был анонсирован в этом же году pow601, явившийся как результат совместной разработкиIBM,APLbMotorola,Texas.

Все вышеуказанные микропрограммы были 32х разр. Архитектуры. Начиная с RS64 анонсированного в 1997 году иpow3. В 1998 начинается эпоха 64х разрядных архитектур.

Микропроцессоры класса RS64,RS64=2,3,4 през. Запись для коммерческих приложений.

RS64 вначале работали на частоте 125Мгц. Более поздние разработкиRS64 - 4 функционирующий на частоте 750Мгц.

Power- 3 был презентован (оптимизирован) для технологических приложений, работающих изначально на частоте 200Мгц. В дальнейшем модифицирован до 450Мгц.

Power- 4 был разработан для использования как в коммерческих так и в технологических приложениях.Power– 4 был сконструирован в манереPowerPCархитектуры .Изначально заложили для работы на частоте 1,1Ггц и 1,3Ггц.

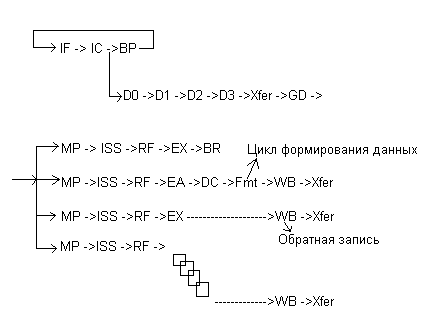

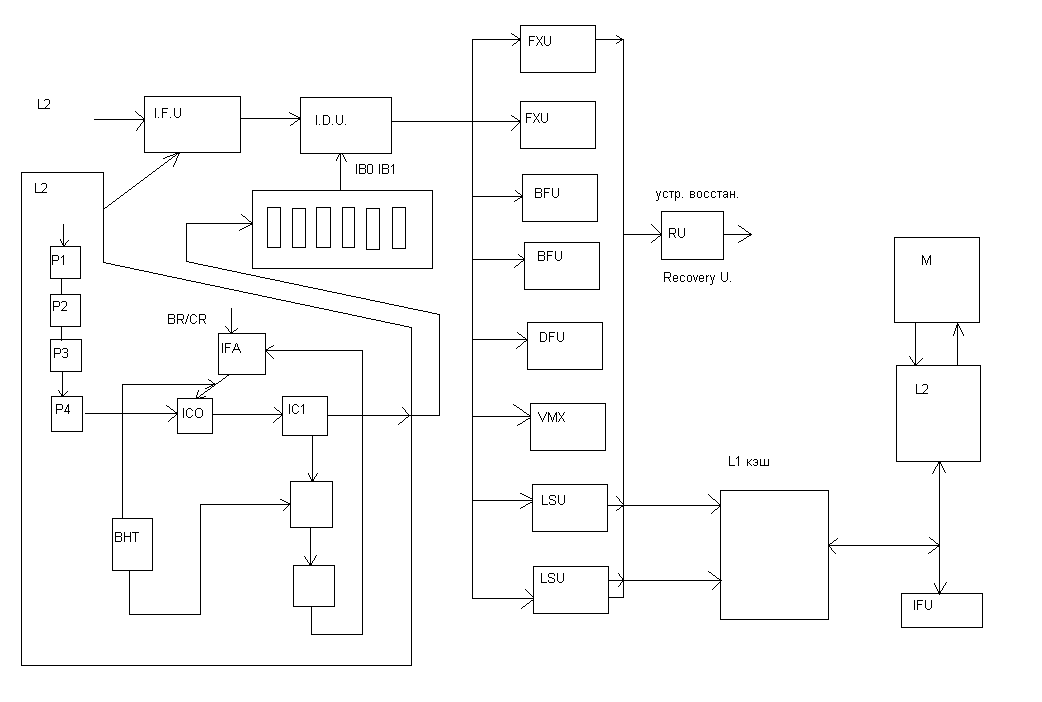

Стадии конвейера Power4.

IF, IC, BP – циклы предназначенные для выборки инструкций и анализа предсказания перехода.

БЛОК ВЫБОРКИ КОМАНД POWER4.

Прежде чем рассматривать архитектуру блока выборки команд POWER4 необходимо отметь следующее:

POWER4 является суперскалярным процессором с конвейерной организацией обработки команд. Как мы увидим далее, при рассмотрении технологии конвейерной обработки команд в процессоре возникают конфликты по управлению, связанные с выполнением команд переходов.

Для уменьшения времени простоя конвейера используется технология предсказания переходов то есть вероятностный метод продвижения команд по конвейеру .Не вдаваясь в подробности функционирования механизма логики предсказания переходов, который мы рассмотрим позже, отметим только то , что загрузка очередной порции команд в кэш инструкций из вышестоящего уровня иерархии памяти происходит по адресу, сформированному этой логикой (блоком предсказания переходов)

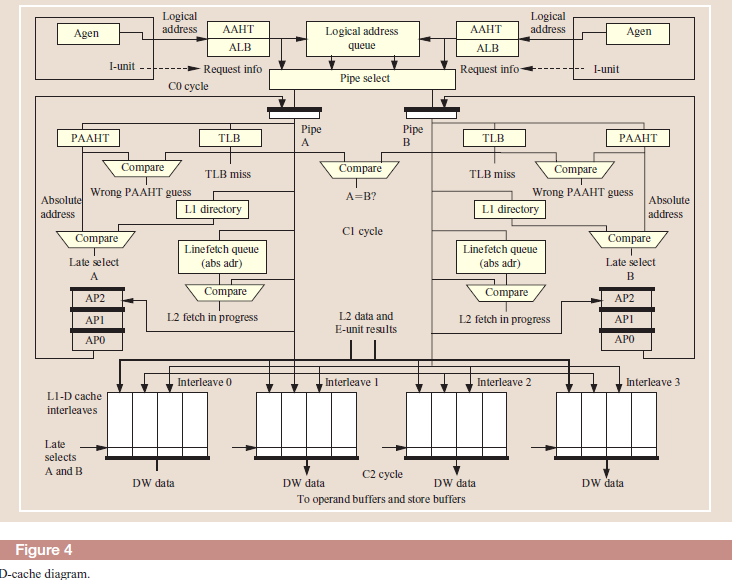

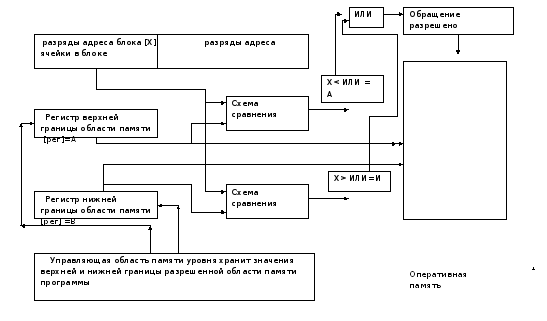

Так как адреса обращения за командами являются логическими при использовании виртуальной памяти и требуется их преобразование в физические, то для сокращения числа обращений к блоку преобразования адресов, используются буфера быстрой переадресации (TLB) , в которых хранятся значения адресов логических страниц и соответствующих им физические адреса , вычисленные ранее при первом обращении в память по выше упомянутым логическим адресам этих страниц.

Но в отличии от кэш данных механизм обнаружения команд в кэш инструкций и использование буферов быстрой переадресации намного сложнее и это в первую очередь связано с использованием вероятностного метода выбора инструкций из кэш.

Если при загрузке строки данных в кэш промах в дальнейшем при обращении к данным этой строки может возникнуть при изменении их самим процессором или другим агентом системы (многопроцессорные системы) , то при загрузке строки команд в кэш инструкций нет ни какой гарантии, что все команды в этой строке будут выполнены полностью, прежде чем будет загружена другая порция команд в кэш инструкций (из за команд переходов).

Уменьшить вероятность промаха можно уменьшением размера строки ,загружаемой в кэш инструкций, но при этом возрастает размер буфера переадресации.

Большой же размер строки приводит к увеличению числа команд переходов и усложняет логику предсказаний и снижает вероятность правильности предсказания ,поэтому был выбран компромиссный вариант –выбирать строку большого размера ,а анализ предсказания переходов осуществлять по секторам строки ,на которые она делиться. При чем РАЗМЕР СЕКТОРА выбрать равным буферу , в который читаются команды из кэш инструкций для выполнения в процессоре. Но для этого пришлось вводить не один буфер TLBа два, потому что первый хранит физические адреса строк находящихся в кэш в соответствии с логическими адресами обращения за командами .а второй буфер осуществляет контроль за продвижением команд внутри строки каждый раз при загрузке очередного сектора из кэш инструкций в буферные регистры путем сравнения физических адресов из обоих буферов

Инструкция выбирается из КЭШ инструкций по значению адреса IFAR- Instr.fetch address reg.

Обычно IFAR загружается согласно логике предсказания перехода.

В случае ошибочного предсказания ,необходимо будет произвести корректировку значения IFAR, чтобы продолжить выполнение потока инструкций в нужном направлении. Кроме этого изменение потока инструкций может быть вызвано прерыванием от внешних событий, в любом случае, как только в IFAR будет загружен адрес команды, то до восьми инструкций поступает на конвейер в каждом цикле.

Каждая строка в КЭШ инструкция составляет 128 байт, которая разделена на 4 эквивалентных сектора по 32 байта, которые определяют ширину данных записи/ считывания в цикле работы кэш памяти команд.

В архитектуре Powerвзят буфер Т LB( translate looksid buffer) и SLB – (Segment looksid buffer) для преобразования эффективного адреса в реальный. Power4 содержит 4 буфера трансляции (по два на каждый процессор в двух ядерной архитектуре то есть на каждый процессор приходится кэш команд и кэш данных).

Когда конвейер инструкций готов получать инструкцию, содержимое IFAR посылается в полностью ассоциативный буфер IDIR(Instr. Directory), который адресуется частью эффективного адреса, другая часть которого используется как тег . Кроме этого теговая строка содержит 42 бита реального адреса, содержащие два полных физических адреса строк, переписанных из кэшL2 в кэш инструкций и находящихся в ней на данный момент. Так как размер кэшL2 составляет 1,5 МГБ, то для фиксации адресов двух строк из кэшL2 в кэш инструкций нужны эти 42 разряда. В блоке выборки команд имеется еще таблица переадресации IERAT , которая имеет такую же архитектуру как и выше упомянутый буфер с той лишь разницей , что в теговой строке содержится физический адрес-результат преобразования логического адреса. Содержимое этих двух буферных таблиц и является исходной информацией для определения наличия команд в кэш инструкций.

И так содержимое регистра адреса выборки инструкций ,обновляется принимая значение адреса первой инструкции в следующем секторе, после того как он будет передан в кэш инструкций , выше упомянутые таблицы и в блок предсказания где сформируется адрес команды, по которому возможно пой дет выполнение программы, если по данному адресу логика обнаружения команд перехода зафиксирует таковую или по другим адресам в считанном секторе в случае его нахождения в кэш инструкций . Если в считанном секторе не будет обнаружен факт перехода и все команды в секторе будут выполняться последовательно, то в буфер инструкций будет загружен следующий сектор. А сейчас вернемся к началу цикла выборки инструкций из кэш и рассмотрим подробнее механизм обнаружения их в памяти .

И так по значению в IFARсчитывается значение реального адреса из “IDIR” эффективный и реальный адреса из таблицы IERAT.

IERAT (содержит эффективный и соответствующий ему реальные адреса) проверяется с тем чтобы проверить достоверность входа и чтобы реальный адрес сравнить со значением IDIR .Сравнение необходимо ввиду того, что с момента загрузки строки из кэшL2 в кэш инструкций к моменту выбора очередного сектора из нее в буферные регистры блока выборки, строка может перейти в состояниеINVALIDили на ее место будет к этому моменту загружена другая строка из системной памяти. Если в таблице IERAT установлен флаг INVALID, то

EA должен быть транслирован из TLB и SLB. Выбранная инструкция «пузырится». Если IERAT VALID, RAIPIR=RAIERустанавливая Icahehit i=1, разрешает продвижение конвейера и работу блока предсказаний и IFAR вновь устанавливается в соответствии с индикатором ВТВ. Активизируются декодеры, начинается формирование групп, логика разрешает выбранным инструкциям продвигаться по конвейеру.

ЕСЛИ обнаружен промах, возможны несколько сценариев:

1) буфер предвыборки проверяется есть ли в нем затребованная инструкция, и если да, логика продвигает эти инструкции к конвейеру: как если бы они были выбраны из КЭШа и записывает также критический сектор в КЭШ.

2) Если инструкции нет в буфере, формируются два последовательных запроса к КЭШ уровня L2. L2 обрабатываются, в результате чего будет произведена запись в кэш инструкций и в буфер предвыборки .

В случае присутствия затребованной инструкции в буфере предвыборки, организуется запрос в кэш L2 за очередной строкой.

В дополнение к механизму выборки инструкции по затребованным запросам БВК осуществляет выборку инструкций, которые в скором времени будет затребована для выполнения.

Блок-схема блока выборки команд Power4

D0, D1, D2, D3 Xfer, GD – циклы, в течении которых инструкция декодируется и формируется в группы.

MP – цикл, в течении которого выявляются все зависимости, ресурсы, и группа диспетчеризуется в соответствующую очередь.

ISS– данный цикл предназначен для постановки в очередь для выполнения в функциональном устройстве, чтения соответствующего адреса регистра для выбора данных из регистрового файла и формирования адреса для записи результата .

EX – цикл выполнения.

WB – цикл записи в регистр результатов. В этом цикле инструкция заканчивает выполнение, но не завершенной она не моет завершиться по крайней мере еще 2 цикла.

Xfer, CP – циклы предназначенные для завершения всех старших Групп или инструкций в той же группе.

Следует отметить, что инструкции, выбранные из кэш инструкций ждут D1 цикл, если они выбираются раньше, чем попадут в группу. Подобные инструкции могут ждатьMPцикла, если ресурсы недоступны илиISSцикла или СР цикла для завершения.

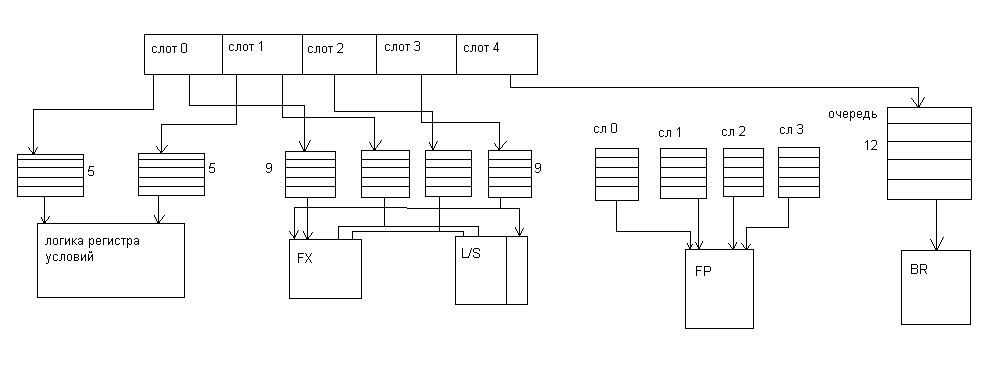

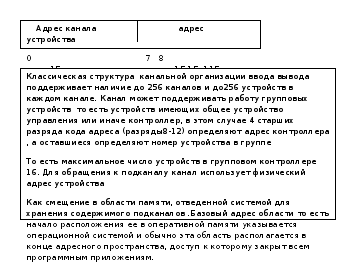

Особенностью архитектуры Power4 является объединение инструкций в группы по 5 инструкций в каждой, которые поступают после формирования на этап диспетчеризации для дальнейшего исполнения в соответствующих исполнительных устройствах. Это делается с целью упрощения механизма отслеживания за выполнением инструкций при безупорядочном выполнении в исполнительных устройствах. Если вINTELотслеживается каждая инструкция и удаляется с конвейера при завершении всех предыдущих, то вPower4 удаляется группа целиком, т.е. 5 инструкций при условии, что все инструкции в группе завершены, и все предыдущие группы удаляются с конвейера.

Power4 имеет так называемую Глобальную таблицу завершения групп. Для увеличения числа инструкций находящихся на исполнении в устройствахPower4 имеет Глобальную таблицу завершения инструкций на 20 входов. Т.е. одновременно отслеживаются 20 групп. Т.е. 20*5=100 инструкций, а при 2х ядерном до 200. Для каждой группы находящейся на этапе выполнения в таблице отводится строка, в которую заложен адрес

1 ой инструкции в группе. Таким образом, частью механизма завершения инструкций в программном порядке.

Индивидуальные группы следуют через систему то есть состояние процессора отслеживается на границе группы ,а не на границе инструкции внутри группы .Любая исключительная ситуация вызывает сохранение старшей группы, предшествующей возникновению причины прерывания.

Группа содержит до пяти внутренних инструкций. На стадии формирования группы инструкции в группе размещаются последовательно. Старшая инструкция в слот 0,следующая за ней в слот 1 и т.д. Слот 4 зарезервирован для инструкций перехода. Только одна группа инструкций распределяется за цикл и все инструкции в группе распределяются одновременно.

Индивидуальные инструкции из очередей в функциональных устройствах поступают на выполнение беcпорядочно. Результат фиксируется ,когда группа завершает выполнение условием которого является ситуация ,когда все старшие группы завершены и завершены все инструкции в группе.

Для осуществления корректного выполнения некоторым инструкциям запрещены спекулятивные операции то есть обгонять впереди идущие в программном коде. Примером таких инструкций являются инструкции чтения и записи в защищенные области памяти или такие как запись в регистры ,фиксирующие состояние процессора.

Для организации безупоряочного выполнения большинство логических (архитектурных) регистров подвергаются преобразованию, но не все . Инструкции, в которых запрещено переименование, размещаются в конце группы

Внутренние инструкции в группе в большинстве своем являются системными командами ,однако, иногда системные команды разбиваются на несколько внутренних при формировании группы. Если системная команда разбивается на две внутренние, то обе они должны быть в одной группе. Если обе инструкции не могут быть размещены в одной группе, то группа заканчивается и новая группа формируется .Инструкция следуемая за разбиваемой может быть размещена в группе при наличии в ней места.

Следует отметить, что при формировании групп учитываются возможности инструкций из слотов в исполнительном устройстве. Так например, в слоте 4 могут располагаться инструкции перехода, если к моменту формирования группы таковой не окажется, то их место 4 ый слота формир. Инструкц. Н.О.П.

Так устройство, обрабатывающее содержимое регистра условий может принимать инструкции только из слота 0 или 1.

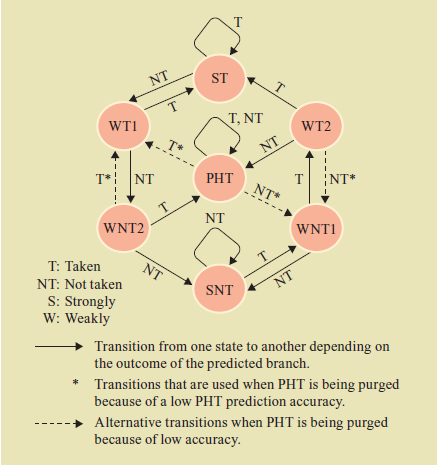

В Power4 до 8 инструкций выбираются в каждом цикле из кэш инструкций в буфер инструкций. Логика предсказания переходов сканирует выбранные инструкции, просматривая до 2х переходов в каждом цикле. В зависимости от типа найденного перехода, различные механизмы предсказания помогают предсказывать направление и адрес перехода. Безусловные переходы не предсказываются.Power4 использует для предсказания переходов 3 таблицы историй переходов. Первая таблица, называемая локальным предсказанием подобна традиционной таблице В.T.Т. Это 16.384 входов табл (2 в 14 ой степени) индексируемая адресом инструкций перехода с 1 бит предсказания.

Вторая таблица, называемая глобальным предсказанием. Предсказывает направление перехода в соответствии со значением перехода на действительную траекторию при выполнении каждой команды перехода. Траектория прохождения фиксируется в 11 бит регистре по одному биту на каждую группу инструкций , из одиннадцати предыдущих выбранных из кэш. Этот вектор называется вектором глобальной истории. Каждый бит в глобальной истории отражает была ли выбрана следующая группа из последовательного сектора кэш. Вектор глобальной истории собирает информацию о выполнении этих секторов.

В.Т.В. содержит 3 таблицы:

1) таблица локальных переходов.

2) глобальная таблица

3) Селекторная таблица, осуществляющая фиксацию предсказаний в каждой таблице и действительный результат по каждому предсказанию.

Локальная таблица Глобальная таблица Селекторная таблица

Power5

1)Организация многопоточного режима.

Для этого на стадии до – после выборки инструкций из кэш они распределяются по 2м потокам отдельные буфера по 24 инструкции каждая. Таким образом, комплектуются группы инструкций из одного потока.

2)Регистровый фаил разделяется между двумя потоками. Т.е. все регистры файла доступны каждому из потоков.

3) Для реализации многопоточности размер и структура очередей были модифицированы.

Таблица GCTдля каждого входа (группы) сигнала содержит дополнительный бит, фиксирующий принадлежность группы к потоку.

Помимо этого каждый логический регистр при замене на физический стал содержать бит

(индекс) принадлежности к потоку. А количество физических регистров было увеличено.

4) Модернизация подверглась очередь для инструкцииL/S. Дело в том, что области памяти для потоков разнесены в адресном пространстве. Поэтому очереди эти разделились поровну между потоками. А для того, чтобы исключить «пузыри» для этих инструкций организовали виртуальные очереди, в которых фиксируется инструкция при диспетчеризации, но без указания адресов памяти. Как только в реальной очереди освобождается место, инструкция переходит из виртуальной очереди в реальную, и для нее формируется адрес обращения к памяти.

Архитектурные особенности POWER6

Главной особенностью архитектуры Power6 от предыдущих Р4 и Р5 является вынос за пределы конвейера стадий формирования групп, поступающих на диспетчеризацию. Формирование групп вPower6 осуществляется при переходе инструкций из кэшL2 в

кэш инструкции. Таким образом, в кэш L1 поступают формированные группы. Кроме этого, если в Р4 и Р5 сохраняются зависимости внутри группы, то в Р6 инструкции в группе друг от друга независимы кроме инструкции с плавающей точкой.

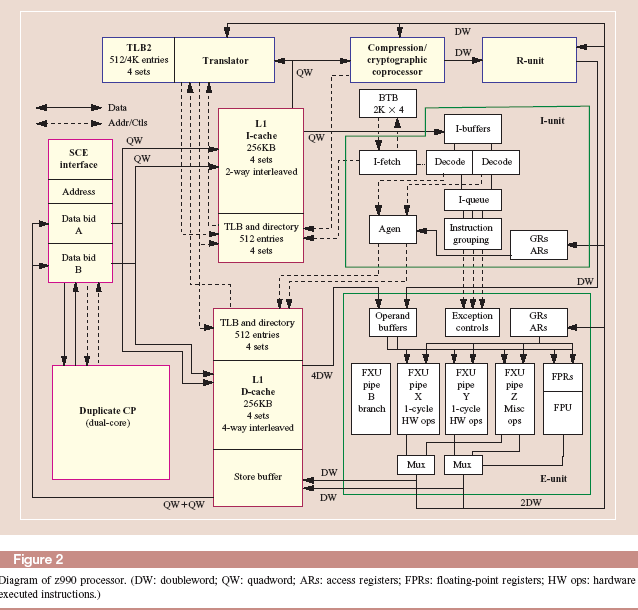

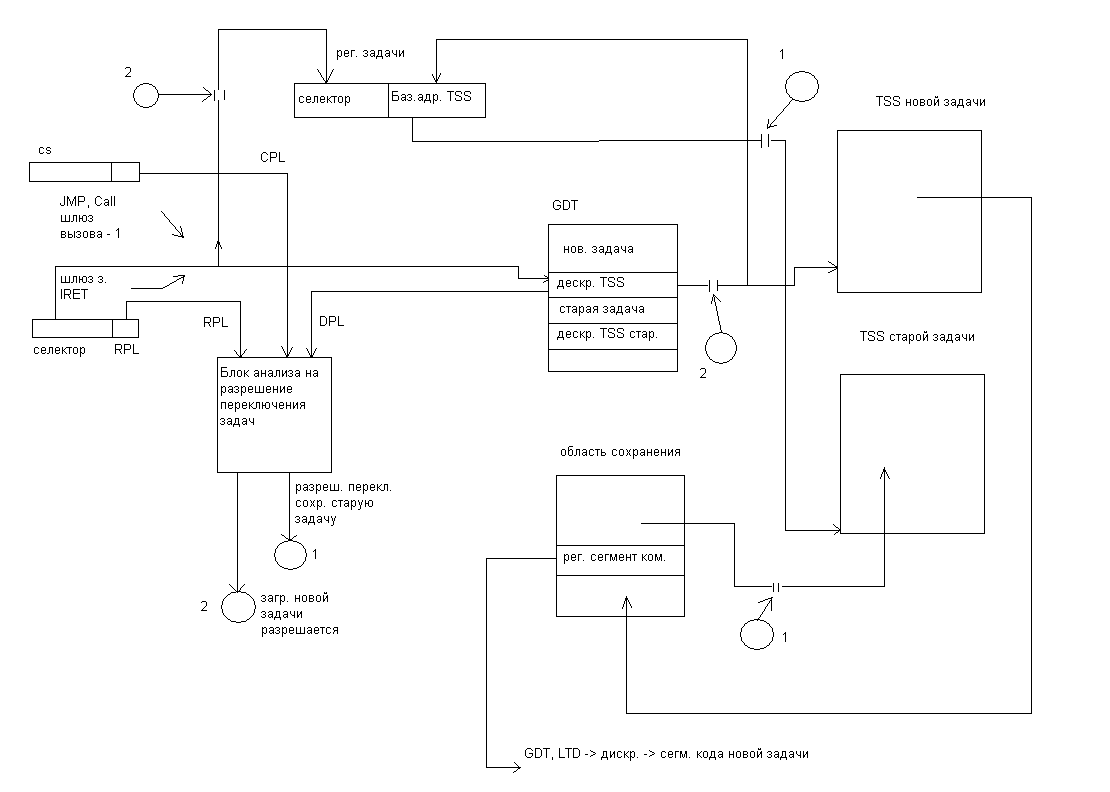

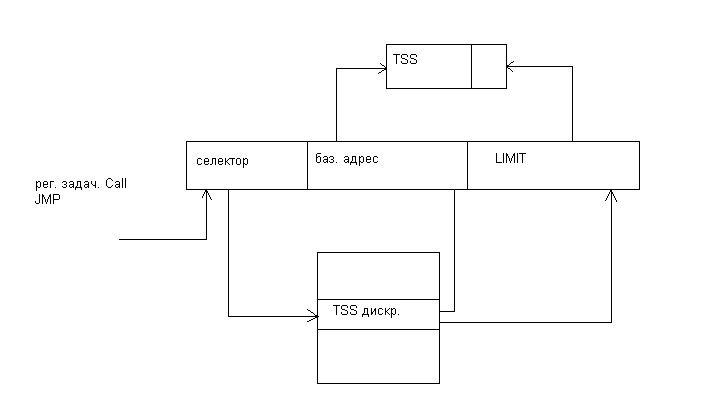

Архитектура микропроцессора Z990

Прежде чем рассматривать архитектуру микропроцессора Z990, необходимо отметить, что данная архитектура явилась результатом эволюции развития серверов предшествующих поколений, родоначальником которых была серия манфреймовIBM360. Особенностью этой серии былаCISCархитектура ,которая определяла структуру и форматы команд, реализуемых в процессорах этой серии . Кроме того эти процессора достаточно развитую аппаратную систему диагностики и восстановления работоспособности процессоров ,поддерживаемую на программном уровне специальными системными командами. Хотя эти процессора не были суперскалярными и выполняли только одну инструкцию за цикл, но имели достаточно высокие показатели и характеристики при выполнении сложныхCISCкоманд за счет наличия дополнительных аппаратных средств(акселераторы, блоки логических операций) и мощную систему памяти ,включающую буферные памяти команд и аппаратные средства поддержки преобразования логических адресов в физические.

Внедрение принципов RISCархитектуры при проектировании процессора сопровождалось разработкой и появлением новых языков программированияC,C++,Java, которые использовались для написания программных приложений для пользователей. Для того чтобы сохранить возможность выполнения уже ранее разработанных приложений и новых разработчики архитектуры процессора решили совместить как технологию суперскалярности, так и возможность выполнения сложных командCISCархитектуры.

При разработке архитектуры микропроцессора были учтены и использованы достижения и наработки в предшествующих моделях процессоров. Это в первую очередь использование милликодов и аппаратные средства восстановления работоспособности системы при возникновении сбоев.

Кроме того в микропроцессореZ990 подобно его предшественникам используется дублирование функционирования основных узлов процессора и содержится несколько механизмов для трансляции его состояния в резервный процессор в случае фатальной ошибки.

В микропроцессоре рассматриваемой архитектуры не используется технология безупорядочного выполнения команд, что является отличительной особенностью от других RISCпроцессоров. За счет этого была сокращена аппаратная часть микропроцессора поддержки этого режима и ее место заняли схемы дублирования основных узлов и восстановления при возникновении ошибок.

Одним из оригинальных решений при проектировании было решение сохранить использование милликода, который использовался еще в предшествующих моделях.

Для того, чтобы понять, что из себя представляет милликод и как он используется в процессоре, напомним, что существуют два основных метода реализации команд в процессоре. Это микропрограммное управление и жесткая логика.

Большинство команд в микропроцессореZ990 реализуется аппаратными средствами, т. е. использует жесткую логику и только сложные команды используют милликод.

Если рассматривать архитектуру микропроцессоров ,например, линейку микропроцессоров PENTIUMфирмыINTEL,то можно отметить, что при реализации сложных команд ,когда дешифратор не справляется с декодированием инструкции в микроинструкции там используется, так называемый, микрокод ,хранящийся в постоянной памяти микропроцессора , который можно интерпретировать как элемент микропрограммного управления.

С точки зрения методологии подхода к реализации сложных команд нет разницы ,,но отличие заключается в том, что INTELиспользовала микроинструкции ,имеющие свою специфичную структуру и формат, аIBMстандартные команды с вертикальным кодированием, таким образом милликод также как основной набор команд выполняется на тех же аппаратных средствах, это во первых. А во-вторых, функциональные возможности милликода намного шире ,чем системные команды, то есть при входе в режим выполнения милликода его рутинам доступны аппаратные средства, которые не доступны даже системным командам.

Размещается милликод ,точнее его рутины в системной памяти в определенной области ,в которую запрещен доступ системным командам и загружается в эту область во время инициализации системы по включению питания то есть эта область по сути выполняет функцию памяти микропрограмм.

И так, отказавшись от технологии микропрограммного управления, IBMсохранила ее метод управления вычислительным процессом за счет

1 Использования особого режима во время выполнения милликода.

2 Расширения функциональных возможностей, что позволило реализовать не только интерпретацию сложных команд, но и выполнять сервисные функции в процессоре, связанные с диагностическими операциями и реализацией механизмов прерывания.

Применение милликода в процессоре позволило разработчикам серверов перенести часть функций при реализации виртуального режима в них с системного уровня на аппаратный и именно этот факт стал при реализации технологии логических партиций LPARв серверах фирмыIBM, то есть многооперационных систем на одной аппаратной платформе.

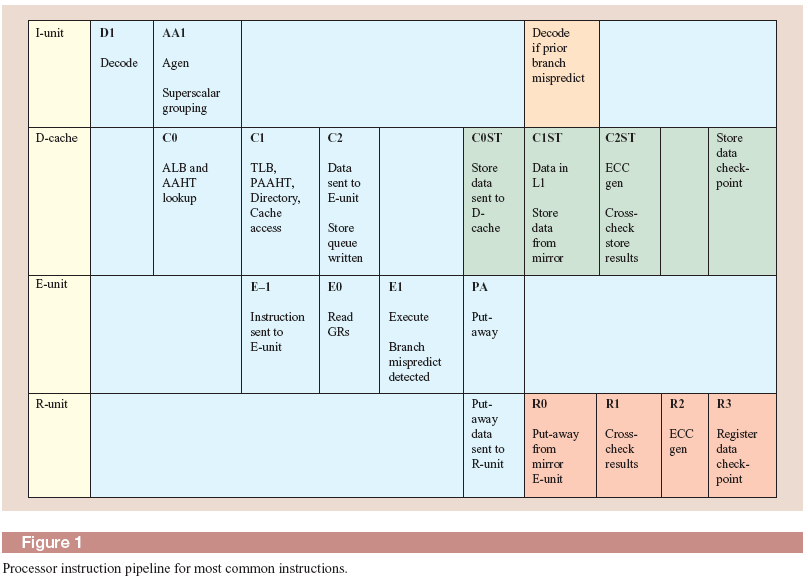

И так рассмотрим работу конвейера в процессоре более подробно.

Выборка инструкций и блок предсказания переходов.(циклы выборки из кэш)

Доступ к кэш памяти инструкций по времени занимает 3 цикла конвейера в течении которых формируется запрос в кэш инструкций со стороны устройства выборки инструкций и передача выбранных инструкций в буферные регистры. Обычно эти циклы скрыты и не влияют на производительность процессора так как выборка инструкций из кэш производится с опережением, и была еще использована в свое время в отечественных ЭВМ серии ЕС начиная с ряда2.

В тех случаях когда текст инструкции необходимо декодировать немедленно, то она ,минуя буфер, передается на декодер(случай перевыборки, связанный с командой перехода,.когда целевая инструкция отсутствует в буфере команд)

Устройство выборки имеет 16 буферных регистров, каждый с разрядностью в 4 слова.

Логика предсказания переходов содержит буфер целевых адресов, строки которых содержат, бит предсказания, целевой адрес и адрес самой команды перехода. В случае отсутствия информации в буфере для данной команды перехода принимается решение- нет перехода на целевой адрес.

Помимо этого буфер переходов целевого адреса содержит “историю” переходов, указывая, что на данный момент наиболее вероятен “сильный”,”слабый”или отсутствие перехода в зависимости от величины счетчика переходов.

Декодирование и формирование групп .(циклы D1,AA1)

Декодеры инструкций могут декодировать любой тип инструкций. Большинство инструкций декодируется в одном цикле. Однако, наиболее сложные требуют более одного цикла для декодирования, к таким, например, относятся двухадресные инструкции, указывающие на расположение операндов в памяти.

Большинство других инструкций декодируются вместе, объединяясь в группу с одним исключением: инструкция перехода должна быть старшей в группе .До трех инструкций может входить в группу.

Совместно с командой перехода, которая является старшей в группе, могут находиться простые, выполняемые за один такт, к которым относятся логические и арифметические операции.

Идея размещения команды перехода старшей в группе связана с тем, что на первый взгляд является парадоксальной, так как эти команды предназначены для анализа признаков результатов от предыдущих команд. Однако выбранная схема при отсутствии безупорядочного выполнения, то есть в порядке следования программному коду дает возможность получать результат перехода в одном цикле с проверяемой командой, так как она выполняется в предыдущей группе программного кода.

Во время формирования групп могут иметь место факторы ,которые ограничивают их эффективное выполнение в процессоре и препятствуют включению инструкций в группу. Так ,например ,одним из условий является , что генерация адреса обращения к памяти должна быть завершена до того или в том же цикле ,в котором группа с инструкцией ,использующей этот адрес, поступает в операционное устройство для исполнения. Кроме того ,если инструкция имеет зависимость при формировании адреса от инструкции уже распределенной в группу,(старшая инструкция производит операцию над базовым или индексным регистрами, являющихся составной частью адреса операнда) то она не включается в группу.