TOATS

.pdf

11

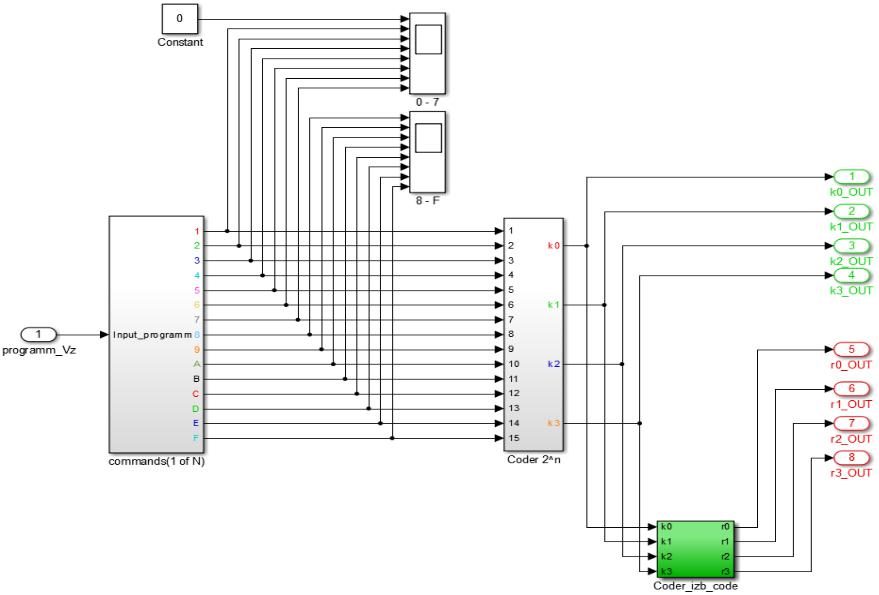

Рис. 2. Модель блока Peredacha.

12

Блок Peredacha представляет собой модель поста телеуправления.

Состав блока:

Commands (1 of N) – дешифратор команд. Входным сигналом дешифратора является десятичное число в диапазоне от 1 до 15.

Выходной сигнал элемента представлен в коде 1 из N, где N –

шестнадцатеричный номер команды. Дешифратор команд позволяет определить текущую команду, формируемую задатчиком, за счет того,

что он осуществляет перевод десятичного числа на входе в диапазоне от

0 до 15 в код «1 из N» (распределяет разные входные сигналы по различным выходам). Код «1 из N» означает, что только на одном выходе дешифратора, шестнадцатеричный эквивалент которого соответствует текущему значению входного сигнала, присутствует логическая единица, а на остальных выходах присутствует ноль. Таким образом, при подаче на вход дешифратора числа 1, логическая единица появится на выходе 1, при подаче на вход числа 15 – на F.

Coder 2^n – кодер обыкновенного двоичного кода. Преобразует код «1

из N» в код «2^n» (обыкновенный двоичный код). Данный кодер формирует информационную часть разделимого кода, которая, по сути,

представляет двоичный код номера передаваемой команды. Например,

если логическая единица подается на вход под номером 1, то выходной двоичный сигнал кодера будет иметь вид k3k2k1k0=0001, если логическая единица подается на вход 9, то – 1001 и т.д.

Coder_izb_code – кодер контрольной части разделимого кода. Кодер контрольной части доопределяет по заданному правилу значения контрольных разрядов, исходя из текущих значений информационных на выходе кодера обыкновенного двоичного кода.

Кроме управляющих элементов на схеме приведены индикаторы, для контроля правильности работы управляющих элементов. Индикаторы применять необязательно.

13

Работа модели происходит следующим образом. Сигнал из задатчика в виде десятичного числа поступает на вход Programm_Vz, а оттуда в дешифратор команд. Дешифратор команд формирует на одном из выходов логическую единицу, сохраняя на остальных значение логического нуля. При разных значениях сигнала на входе логическая единица будет формироваться на разных выходах. Всего выходов 15,

поэтому дешифратор команд может сформировать 15 различных команд. Выходные сигналы дешифратора команд поступают на входы кодера обыкновенного двоичного кода, который переводит номер своего входа с логической единицей в четырехразрядный двоичный эквивалент,

формируя, таким образом, информационную часть сообщения для передачи её по линии связи. Помимо линии связи выходные сигналы декодера обыкновенного кода поступают на соответствующие входы кодера избыточного кода с целью вычисления последним значений контрольных разрядов. Совокупность сформированных кодером обыкновенного кода информационных разрядов и кодером избыточного кода контрольных отправляется в линию связи в соответствии с форматом сообщения (позицией каждого контрольного и информационного разряда в сообщении).

Студент в данной модели должен разработать структуру блока

Coder_izb_code в соответствии с вариантом избыточного кода,

используемого для передачи сообщений, остальные элементы модели включены в шаблон. Прежде чем разрабатывать модель блока

Coder_izb_code следует изучить устройство остальных элементов модели.

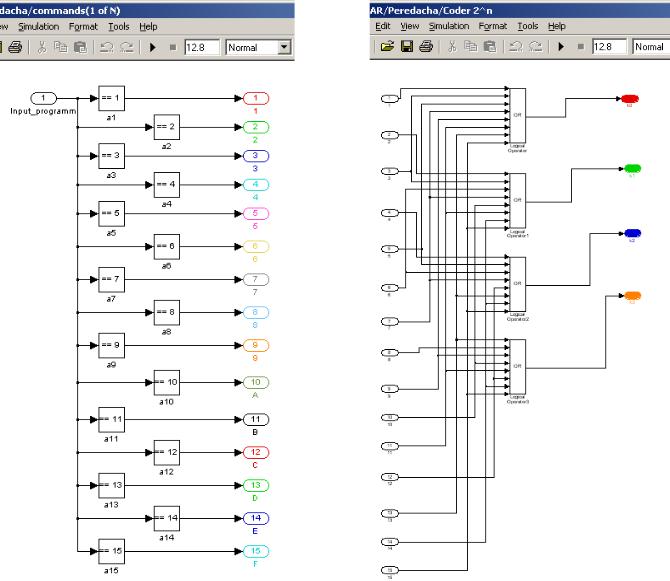

На рисунке 3 представлена модель дешифратора команд.

На рисунке 4 приведена реализация кодера обыкновенного кода 2^n

14

Рис. 3. Модель дешифратора команд (слева)

Рис. 4 Реализация кодера обыкновенного кода 2^n (справа)

Все используемые элементы представляют собой устройства сравнения с различными константами. Константы характеризуют значения уставок при которых на соответствующем выходе формируется логическая единица. Элемент сравнения формирует логическую единицу только при совпадении входного сигнала со значением записанной в него константы

15

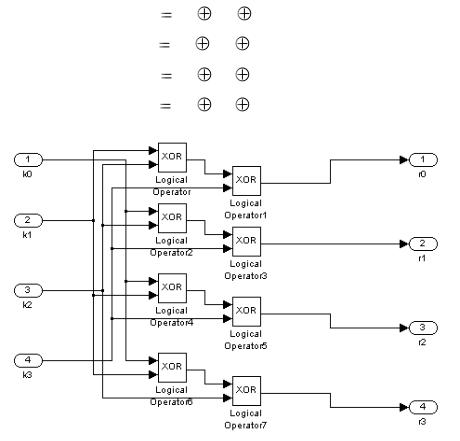

В соответствии с указанной формулой для 8-миразрядного инверсного кода запишем выражения для определения значения разрядов его контрольной части,

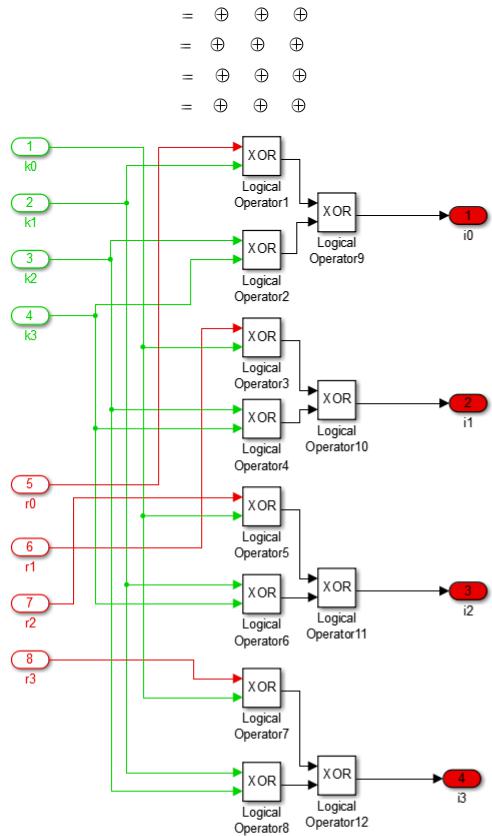

аналитические выражения для определения значений синдрома декодирующим устройством для данного кода имеют вид:

r0 |

k3 |

k2 |

k1 |

r1 |

k3 |

k2 |

k0 |

r2 |

k3 |

k1 |

k 0 |

r3 |

k2 |

k1 |

k0 |

Рис. 5 Модель кодера инверсного кода

В случае правильного приема кодовой комбинации значения разрядов синдрома должны иметь нулевые значения: i0=i1=i2=i3=0. Наличие единичных значений синдрома свидетельствует о наличии ошибок: единичное значение только в одном из синдромов - ошибка в соответствующем контрольном разряде,

который присутствует в уравнении разряда синдрома с единичным значением; три единичных значения - ошибка в соответствующим информационном разряде,

который не присутствует в уравнении разряда синдрома с нулевым значением; два или четыре единичных значений в синдроме - ошибка в двух и более разрядах.

16

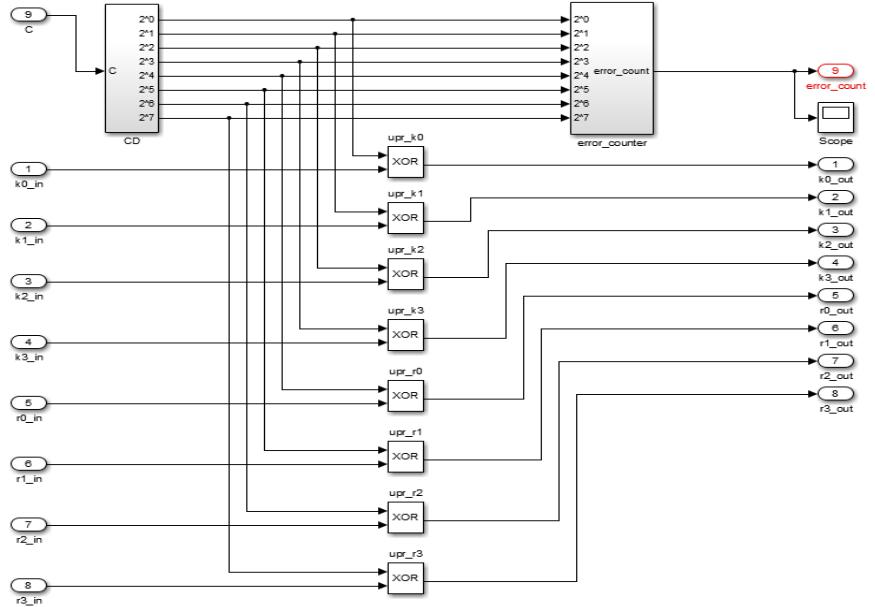

Рис. 6 Модель линии связи с искажениями

17

CD – двоичный восьмиразрядный счетчик для моделирования искажений различной кратности;

Элементы XOR – каждый элемент в зависимости от управляющего сигнала,

поступающего с соответствующего выхода счетчика инвертирует, либо повторяет входной сигнал на своем выходе. Таким образом, элементы XOR позволяют вносить различные искажения в передаваемые по линии связи сообщения. Кратность искажения определяется количеством логических единиц на выходах счетчика CD.

Error_counter – счетчик с выходным сигналом в виде десятичного числа,

показывающего кратность внесенной в передаваемое сообщение ошибки.

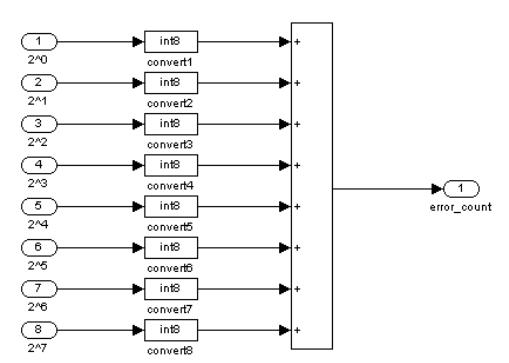

Рис. 7 Модель счетчика кратности ошибок Error_counter.

Int8 - элемент, преобразующий двоичные единицу и ноль в десятичные.

18

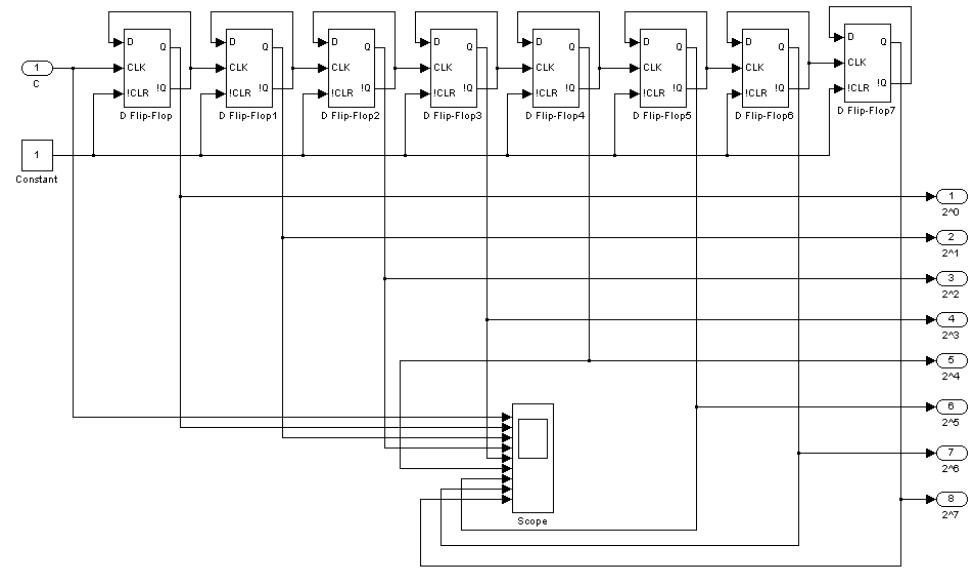

Рис. 8 Модель счетчика CD

19

D Flip-flop – D-триггеры. В счетчике D-триггеры включены по схеме счетных триггеров для подсчета в двоичном коде количества поступающих на вход счетчика импульсов от генератора ошибок С (рис.1)

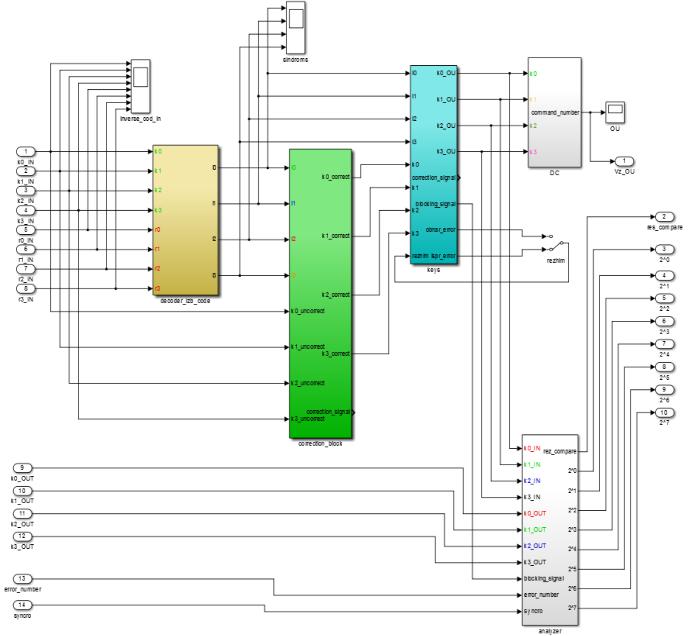

Рис. 9 Модель блока Priyem Decoder_izb_code – декодер избыточного кода

Ключ rezhim – переключатель режимов работы декодера обнаружение/исправление ошибок

Correction_block – схема коррекции информационных разрядов принятого сообщения в заданном помехозащитном коде

Keys – схема распознавания одиночных и двойных ошибок

20

Analyzer – автоматический двоичный счетчик ошибок заданной кратности

DCдешифратор принятых команд

i0 |

r0 |

k3 |

k2 |

k1 |

i1 |

r1 |

k3 |

k2 |

k0 |

i2 |

r2 |

k3 |

k1 |

k0 |

i3 |

r3 |

k2 |

k1 |

k0 |

Рис. 10 Модель блока Decoder_inverse_code