- •1. Основы микросхемотехники ИС

- •1.1. Основные термины и определения

- •1.2. Этапы и направления развития ИС

- •1.3. Классификация ИС

- •1.3.4. Классификация по степени интеграции

- •1.4. Последовательность разработки ИС

- •2. Основы цифровой техники

- •2.3. Основные логические операции

- •2.4. Формы представления логической функции

- •2.5. Структурное проектирование цифровых схем комбинационного типа

- •3. Основные параметры и характеристики ЦИС

- •3.1. Основные параметры ЦИС

- •3.2. Характеристики ЦИС

- •3.3. Определение измеряемых параметров по характеристикам

- •4.1. Формирование биполярных транзисторов

- •4.3. Эквивалентная модель интегрального n–p–n биполярного транзистора

- •4.4. Режимы работы биполярного транзистора

- •4.6. Статические ВАХ транзистора

- •5. Диоды в интегральных схемах

- •5.1. Модель идеального диода

- •5.2. Эквивалентная схема интегрального диода

- •5.3. Аппроксимации ВАХ диода

- •5.4. Варианты реализации интегральных диодов

- •6. Пассивные элементы ИС

- •6.1. Основные параметры резисторов

- •6.2. Реализация интегральных резисторов

- •6.4. Реализация интегральных конденсаторов

- •7. Элементная база статических ЦИС на биполярных транзисторах

- •7.1. Резисторно-транзисторная логика (РТЛ)

- •7.1.1. Характеристики РТЛ

- •7.2. Эмиттерно-связанная логика (ЭСЛ)

- •7.2.1. Принцип работы

- •7.2.2. Входная характеристика

- •7.2.3. Передаточная характеристика

- •7.2.4. Выходная характеристика

- •7.2.6. Многоярусные ЭСЛ (МяЭСЛ)

- •7.3. Диодно-транзисторная логика

- •7.3.1. Расчет передаточной и входной характеристик

- •7.3.2. Выходная характеристика

- •7.3.3. Влияние нагрузки на логические уровни

- •7.4. Транзисторно-транзисторная логика

- •7.4.1. ТТЛ-элемент с простым инвертором

- •7.4.2. Передаточная характеристика

- •7.4.3. Входная характеристика

- •7.4.4. Выходная характеристика

- •7.4.6. Основные параметры

- •7.4.7. Многоэмиттерный транзистор

- •7.4.8. ТТЛ-элемент со сложным выходным каскадом

- •7.4.9. Модификация логического элемента

- •7.5. Интегральная инжекционная логика

- •7.5.2. Реализация логических функций

- •8. Полевые транзисторы

- •8.1. Типы полевых транзисторов

- •8.2. Определение физических параметров

- •8.3. модель полевого транзистора

- •8.4. Режимы работы и уравнения ВАХ полевого транзистора

- •9. Элементная база на полевых транзисторах

- •9.2. Передаточная характеристика и параметры инвертора с линейной нагрузкой

- •9.3. Передаточная характеристика и параметры инвертора с нелинейной нагрузкой

- •9.4. Передаточная характеристика и параметры инвертора с квазилинейной нагрузкой

- •9.5. Передаточная характеристика и параметры инвертора с токостабилизирующей нагрузкой

- •9.6. Передаточная характеристика и параметры комплементарного инвертора

- •9.8. Логические элементы на МОП-транзисторах

- •9.9. Определение эквивалентной крутизны группы переключающих транзисторов

- •9.11. Влияние параметров транзисторов на характеристики логического элемента

- •9.12. Сопряжение ТТЛ- и КМОП-схем

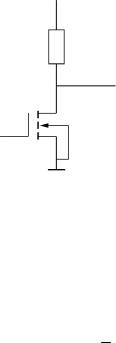

При использовании КМОП элементной базы р-канальные транзисторы включаются по правилу обратной логики (рис.9.28).

MBp |

UИП |

|

UИП |

MAp |

|

MAp |

|

|

|

A |

|

|

F |

|

MBp |

|

MAn |

|

|

A |

B |

|

|

|

|

|

|

|

|

|

F |

|

MBn |

MAn |

MBn |

B |

|

|

|

|

а |

|

б |

Рис.9.28. Логические элементы на КМОП: а - 2И-НЕ; б - 2ИЛИНЕ

Поскольку удельная крутизна p-канальных транзисторов меньше n-канальных, то для выравнивания фронта и среза необходимо увеличивать топологические размеры W p-МОП.

9.9. Определение эквивалентной крутизны группы переключающих транзисторов

Так как крутизна измеряется в [мА/В2], то ее можно определить как проводимость при единичном напряжении.

Для определения напряжения уровня логического нуля необходимо знать эквивалентную крутизну группы переключающих транзисторов (рис.9.29).

198

UИП

ZН

Выход

MЭКВ

Вход

Рис.9.29. Схема логического элемента с эквивалентнымтранзистором

При последовательном соединении переключающих транзисторов, имеющих крутизны k1, k2, …, kn, эквивалентная крутизна этой группы будет определяться как

|

1 |

= |

1 |

+ |

1 |

+ ... + |

1 |

; |

|||

k |

ЭКВ |

k |

k |

2 |

k |

n |

|||||

|

|

|

|

||||||||

|

|

1 |

|

|

|

|

|

||||

если k1 = k2 = …= kn = k, то получим kЭКВ = kn ,

где n - число последовательно включенных транзисторов в переключающей группе.

При параллельном соединении переключающих транзисторов, имеющих крутизны k1, k2, …, kn, эквивалентная крутизна этой группы будет определяться как

kЭКВ = k1 + k2 + ... + kn ;

если k1 = k2 = …= kn = k, то получим kЭКВ = k × n ,

где n - число параллельно включенных транзисторов в переключающей группе.

199

9.10. Расщепление передаточной характеристики. Определение наихудшего случая

для уровня логического нуля

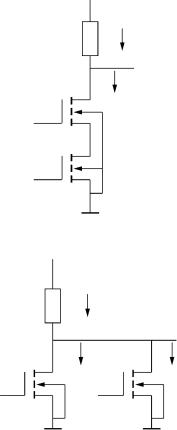

Рассмотрим логические элементы И-НЕ (рис.9.30), ИЛИ-НЕ (рис.9.31) и определим крутизну эквивалентного транзистора.

UИП

ZН IН

F

IA= IB

UA1 MА

UB1 MВ

Рис.9.30. Сквозной ток, протекающий в логическом элементе 2И-НЕ

|

UИП |

|

|

|

ZН |

IН |

|

|

|

|

F |

|

|

IA |

IB |

UA1 |

MА |

UB1 |

MB |

|

|

Рис.9.31. Сквозной ток, протекающий в логическом элементе 2ИЛИ-НЕ

200

В логическом элементе И-НЕ сквозной ток протекает через нагрузку и открытые транзисторы МА, МВ, имеющие одинаковую крутизну k только при UА,В = 1. Тогда IН = IА = IВ, и уровень логи-

|

kН |

, |

|

ческого нуля пропорционален kЭКВ |

|||

где |

|||

kЭКВ = k2 .

В логическом элементе ИЛИ-НЕ сквозной ток протекает через нагрузку и открытые транзисторы МА, МВ, имеющие одинаковую крутизну k, в трех случаях:

∙ |

при UА = 1 открыт МА, |

IН = IА, |

kЭКВ = k; |

||

∙ |

при UВ = 1 открыт МВ, |

IН = IВ, |

kЭКВ = k; |

||

∙ |

при UА,В = 1 |

открыты МА, МВ, |

IН = IА = IВ, |

||

|

kЭКВ = 2k. |

|

|

|

|

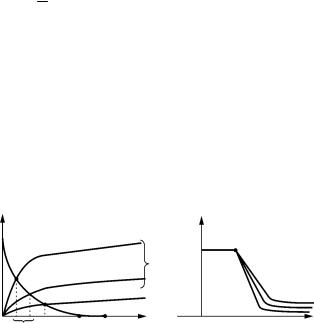

Рассмотрим совместную ВАХ и передаточную характеристики (рис.9.32).

IC0,IН |

|

|

UВЫХ |

IН |

2k |

2ИЛИ-НЕ |

UВЫХ1 |

|

|

||

|

k |

|

|

|

k/2 |

2И-НЕ |

U0 |

|

U 0 |

ВЫХ |

|

U 0 |

|

|

|

И_НЕ |

|

|

|

ИЛИ_НЕ |

|

|

|

2И-НЕ(k/2)

2ИЛИ-НЕ(k)

2ИЛИ-НЕ(2k)

UВХ

а |

б |

Рис.9.32. Расщепление уровня логического нуля U0: а - совместная ВАХ; б - передаточная характеристика

Более высокий уровень логического нуля соответствует наихудшему случаю.

201

Таким образом, наихудшим случаем для определения уровня логического нуля U0 в элементе ИЛИ-НЕ является условие kЭКВ = k.

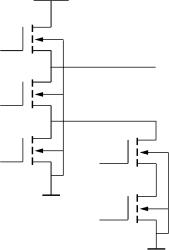

Пример. Определить максимальную и минимальную эквивалентную крутизну для переключающих транзисторов логического элемента (рис.9.33). Транзисторы все одинаковые и имеют крутизну k.

Составим таблицу истинности:

А |

В |

С |

D |

F |

kЭКВ |

0 |

0 |

0 |

0 |

1 |

|

0 |

0 |

0 |

1 |

1 |

|

0 |

0 |

1 |

0 |

1 |

|

0 |

0 |

1 |

1 |

1 |

|

0 |

1 |

0 |

0 |

1 |

|

0 |

1 |

0 |

1 |

1 |

|

0 |

1 |

1 |

0 |

1 |

|

0 |

1 |

1 |

1 |

1 |

|

1 |

0 |

0 |

0 |

1 |

|

1 |

0 |

0 |

1 |

1 |

|

1 |

0 |

1 |

0 |

1 |

|

1 |

0 |

1 |

1 |

0 |

kЭКВ1 = k/3 |

1 |

1 |

0 |

0 |

0 |

kЭКВ2 = k/2 |

1 |

1 |

0 |

1 |

0 |

|

1 |

1 |

1 |

0 |

0 |

|

1 |

1 |

1 |

1 |

0 |

* |

202

UИП

UЗ |

MН |

|

|

|

|

|

|

|

|

|

F |

A |

MА |

|

|

|

|

|

|

B |

MВ |

C |

MC |

|

|

||

|

|

D |

MD |

|

|

|

Рис.9.33. Электрическая схема логического элемента

Распишем более подробно расчет эквивалентной крутизны для случая, отмеченного (*):

kCD = k / 2;

kBCD = k + k / 2 = |

3k |

|

; |

|

|

|

|

|||||||

2 |

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|||

1 |

= |

|

1 |

= |

|

1 |

|

+ |

2 |

= |

5 |

; |

||

kЭКВ3 |

|

|

|

k |

3k |

3k |

||||||||

|

|

kABCD |

|

|

|

|

|

|||||||

kЭКВ3 |

= |

3k |

; |

|

|

|

|

|

|

|

|

|

||

5 |

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||

kЭКВ3 |

> kЭКВ2 > kЭКВ1 . |

|

|

|

||||||||||

Следовательно, в наихудшем случае наибольшее значение уровня логического нуля соответствует наименьшей эквивалентной крутизне, определяемой самой длинной последовательной цепочкой переключающих транзисторов kmin = k/3.

203