- •1. Основы микросхемотехники ИС

- •1.1. Основные термины и определения

- •1.2. Этапы и направления развития ИС

- •1.3. Классификация ИС

- •1.3.4. Классификация по степени интеграции

- •1.4. Последовательность разработки ИС

- •2. Основы цифровой техники

- •2.3. Основные логические операции

- •2.4. Формы представления логической функции

- •2.5. Структурное проектирование цифровых схем комбинационного типа

- •3. Основные параметры и характеристики ЦИС

- •3.1. Основные параметры ЦИС

- •3.2. Характеристики ЦИС

- •3.3. Определение измеряемых параметров по характеристикам

- •4.1. Формирование биполярных транзисторов

- •4.3. Эквивалентная модель интегрального n–p–n биполярного транзистора

- •4.4. Режимы работы биполярного транзистора

- •4.6. Статические ВАХ транзистора

- •5. Диоды в интегральных схемах

- •5.1. Модель идеального диода

- •5.2. Эквивалентная схема интегрального диода

- •5.3. Аппроксимации ВАХ диода

- •5.4. Варианты реализации интегральных диодов

- •6. Пассивные элементы ИС

- •6.1. Основные параметры резисторов

- •6.2. Реализация интегральных резисторов

- •6.4. Реализация интегральных конденсаторов

- •7. Элементная база статических ЦИС на биполярных транзисторах

- •7.1. Резисторно-транзисторная логика (РТЛ)

- •7.1.1. Характеристики РТЛ

- •7.2. Эмиттерно-связанная логика (ЭСЛ)

- •7.2.1. Принцип работы

- •7.2.2. Входная характеристика

- •7.2.3. Передаточная характеристика

- •7.2.4. Выходная характеристика

- •7.2.6. Многоярусные ЭСЛ (МяЭСЛ)

- •7.3. Диодно-транзисторная логика

- •7.3.1. Расчет передаточной и входной характеристик

- •7.3.2. Выходная характеристика

- •7.3.3. Влияние нагрузки на логические уровни

- •7.4. Транзисторно-транзисторная логика

- •7.4.1. ТТЛ-элемент с простым инвертором

- •7.4.2. Передаточная характеристика

- •7.4.3. Входная характеристика

- •7.4.4. Выходная характеристика

- •7.4.6. Основные параметры

- •7.4.7. Многоэмиттерный транзистор

- •7.4.8. ТТЛ-элемент со сложным выходным каскадом

- •7.4.9. Модификация логического элемента

- •7.5. Интегральная инжекционная логика

- •7.5.2. Реализация логических функций

- •8. Полевые транзисторы

- •8.1. Типы полевых транзисторов

- •8.2. Определение физических параметров

- •8.3. модель полевого транзистора

- •8.4. Режимы работы и уравнения ВАХ полевого транзистора

- •9. Элементная база на полевых транзисторах

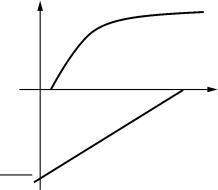

- •9.2. Передаточная характеристика и параметры инвертора с линейной нагрузкой

- •9.3. Передаточная характеристика и параметры инвертора с нелинейной нагрузкой

- •9.4. Передаточная характеристика и параметры инвертора с квазилинейной нагрузкой

- •9.5. Передаточная характеристика и параметры инвертора с токостабилизирующей нагрузкой

- •9.6. Передаточная характеристика и параметры комплементарного инвертора

- •9.8. Логические элементы на МОП-транзисторах

- •9.9. Определение эквивалентной крутизны группы переключающих транзисторов

- •9.11. Влияние параметров транзисторов на характеристики логического элемента

- •9.12. Сопряжение ТТЛ- и КМОП-схем

Граничное условие UВХГР3 |

определяется моментом |

перехода |

||||||

транзистора Т2 в РН |

U |

БКТ 2 |

= 0, |

UВЫХ = U |

БЭ |

. |

При этом |

|

|

|

|

т.е. |

|

Т 2Н |

|||

UВХГР3 = UБЭ 2Н + UД3Н + UБЭ1Н − UД1Н . |

||||||||

4. На участке DE при |

UВХГР3 |

< UВХ < UВХГР 4 |

ток протекает от |

|||||

UИП1 через R1, R2: одна часть тока течет через Д1, другая - через

T1, Д3, R3 и Т2, работающий в РН. UБКТ2 уменьшается:

UВЫХ = UИП2 − IК2R4 = |

|

= UИП2 − [αN IЭДТ2 + IКДТ2 (1 − αП )]R4 . (см. рис.7.27), |

|

IВХ = IR1 − IR3 − (1 − αN )IЭДТ2 − (1 − αI )IКДТ2 |

(см. |

рис.7.28). |

|

Граничное условие перехода на следующий участок работы схемы определяется моментом, когда закрывается входной диод Д1:

UВХГР5 = UБЭ 2Н + Ur Б 2 + UД3Н + UБЭ1Н − UД1ГР ≈ ≈ 3UБЭ 2Н − UДГР + Ur Б .

5. На участке EF при UВХГР5 < UВХ < UИП ток протекает только в

правой части схемы (от UИП1 через R1, R2, Т1, Д3, а также от источника питания UИП2 через R4 и транзистор Т2 (см. рис.7.27 и

7.28):

UВЫХ = UКЭНТ 2 ,

IВХ = −IД0 .

7.3.2.Выходная характеристика

Выходная характеристика является характеристикой инвертора Т2, R4, поэтому она подобна выходной характеристике РТЛэлемента (рис.7.29).

119

IВЫХ |

UВХ1 |

|

|

|

UИП2 |

UКЭН |

UВЫХ |

UВХ0

UИП2

R4

Рис.7.29. Выходная характеристика

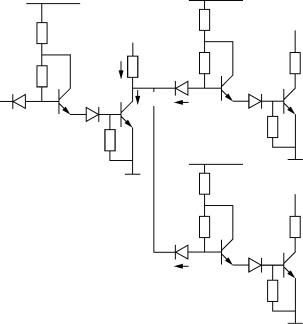

7.3.3. Влияние нагрузки на логические уровни

Рассмотрим, как изменяются логические уровни ДТЛ-элемента при подключении к выходу N нагрузочных подобных элементов

(рис.7.30).

120

|

UИП1 |

|

|

UИП1 |

|

|

R1 |

|

UИП2 |

R11 |

UИП2 |

|

|

|

|

||

|

R2 |

I |

R4 |

R21 |

R41 |

|

R 4 |

UВЫХ |

Д11 |

|

|

|

|

|

|

|

|

Д1 |

|

T1 Д2 |

IК2 |

T11 Д21 |

|

UВХ |

|

IН1 |

T21 |

||

|

|

T2 |

R31 |

||

|

|

R3 |

|

|

|

|

|

|

UИП1 |

1 |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

R1N |

UИП2 |

|

|

|

|

R2N |

R4N |

|

|

|

Д1N |

||

|

|

|

|

T1N |

Д2N |

|

|

|

|

IНN |

T2N |

|

|

|

|

|

|

|

|

|

|

|

N |

Рис.7.30. Электрическая схема ДТЛ-элемента с подключенной нагрузкой

Если на входе ДТЛ-элемента задано UВХ = U0, то на выходе получим UВЫХ = U1. При этом Д1 открыт, Д11…N закрыты. Тогда

IH′ = I′ 1 = IД 0 » 0;

UВЫХ1 N =UИП2 - IR4 R4 =UИП2 - N × I1Н =UИП2 - N × IД0 »UИ

Если на входе ДТЛ-элемента задано UВХ = U1, то на выходе полу-

чим UВЫХ = U0. При этом Д1 закрыт, Т2 в РН, Д11…N открыты. Тогда

121