- •1. Основы микросхемотехники ИС

- •1.1. Основные термины и определения

- •1.2. Этапы и направления развития ИС

- •1.3. Классификация ИС

- •1.3.4. Классификация по степени интеграции

- •1.4. Последовательность разработки ИС

- •2. Основы цифровой техники

- •2.3. Основные логические операции

- •2.4. Формы представления логической функции

- •2.5. Структурное проектирование цифровых схем комбинационного типа

- •3. Основные параметры и характеристики ЦИС

- •3.1. Основные параметры ЦИС

- •3.2. Характеристики ЦИС

- •3.3. Определение измеряемых параметров по характеристикам

- •4.1. Формирование биполярных транзисторов

- •4.3. Эквивалентная модель интегрального n–p–n биполярного транзистора

- •4.4. Режимы работы биполярного транзистора

- •4.6. Статические ВАХ транзистора

- •5. Диоды в интегральных схемах

- •5.1. Модель идеального диода

- •5.2. Эквивалентная схема интегрального диода

- •5.3. Аппроксимации ВАХ диода

- •5.4. Варианты реализации интегральных диодов

- •6. Пассивные элементы ИС

- •6.1. Основные параметры резисторов

- •6.2. Реализация интегральных резисторов

- •6.4. Реализация интегральных конденсаторов

- •7. Элементная база статических ЦИС на биполярных транзисторах

- •7.1. Резисторно-транзисторная логика (РТЛ)

- •7.1.1. Характеристики РТЛ

- •7.2. Эмиттерно-связанная логика (ЭСЛ)

- •7.2.1. Принцип работы

- •7.2.2. Входная характеристика

- •7.2.3. Передаточная характеристика

- •7.2.4. Выходная характеристика

- •7.2.6. Многоярусные ЭСЛ (МяЭСЛ)

- •7.3. Диодно-транзисторная логика

- •7.3.1. Расчет передаточной и входной характеристик

- •7.3.2. Выходная характеристика

- •7.3.3. Влияние нагрузки на логические уровни

- •7.4. Транзисторно-транзисторная логика

- •7.4.1. ТТЛ-элемент с простым инвертором

- •7.4.2. Передаточная характеристика

- •7.4.3. Входная характеристика

- •7.4.4. Выходная характеристика

- •7.4.6. Основные параметры

- •7.4.7. Многоэмиттерный транзистор

- •7.4.8. ТТЛ-элемент со сложным выходным каскадом

- •7.4.9. Модификация логического элемента

- •7.5. Интегральная инжекционная логика

- •7.5.2. Реализация логических функций

- •8. Полевые транзисторы

- •8.1. Типы полевых транзисторов

- •8.2. Определение физических параметров

- •8.3. модель полевого транзистора

- •8.4. Режимы работы и уравнения ВАХ полевого транзистора

- •9. Элементная база на полевых транзисторах

- •9.2. Передаточная характеристика и параметры инвертора с линейной нагрузкой

- •9.3. Передаточная характеристика и параметры инвертора с нелинейной нагрузкой

- •9.4. Передаточная характеристика и параметры инвертора с квазилинейной нагрузкой

- •9.5. Передаточная характеристика и параметры инвертора с токостабилизирующей нагрузкой

- •9.6. Передаточная характеристика и параметры комплементарного инвертора

- •9.8. Логические элементы на МОП-транзисторах

- •9.9. Определение эквивалентной крутизны группы переключающих транзисторов

- •9.11. Влияние параметров транзисторов на характеристики логического элемента

- •9.12. Сопряжение ТТЛ- и КМОП-схем

7.1.3.Основные параметры РТЛ-элемента

Врезультате проведенного расчета характеристик можно определить статические измеряемые параметры, характеризующие элемент:

U1 =U |

ИП |

- |

|

|

N × R2 |

(U |

ИП |

-U |

БЭН |

); |

||

|

R1+ r + N × R2 |

|||||||||||

1) |

|

|

|

|

|

|||||||

|

|

|

|

|

Б |

|

|

|

|

|

||

U 0 = U |

КЭН |

+ |

UИП -UКЭН |

r ; |

|

|

|

|||||

|

|

|

|

|||||||||

2) |

|

|

|

R2 + rК |

К |

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|||

3)UЛ UИП – (UКЭН + IК · rК);

4)UП = UБЭН;

5)UПЗ0 UИП − UБЭН ;

6)U1ПЗ UБЭН – (UКЭН + IК · rК).

Достоинством РТЛ-элемента является простая схемотехника, тогда как к недостаткам можно отнести:

1)несимметричность передаточной характеристики, так

как при используемом напряжении питания UИП входное напряжение переключения равно UБЭН и UБЭН

UИП ;

<<2

2)низкая помехозащищенность UПЗ, т.е. U1ПЗ << UПЗ0 .

7.2. Эмиттерно-связанная логика (ЭСЛ)

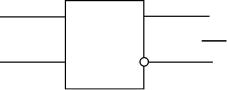

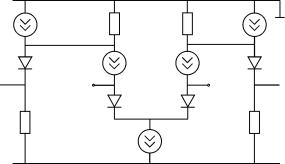

ЭСЛ-элемент имеет два входа и два выхода и реализует логические функции ИЛИ и ИЛИ-НЕ (рис.7.11).

B |

1 |

Y2=A+B |

|

|

|

A |

|

Y1=A+B |

Рис.7.11. Логические функции, выполняемые ЭСЛ-элементом

96

ЭСЛ элементная база широко используется в биполярных ЦИС, так как имеет ряд достоинств:

1)широкие функциональные возможности, поскольку схема имеет парафазные выходы;

2)высокое быстродействие, так как время задержки вентиля может быть порядка 0,1 - 0,2 нс (поскольку все транзисторы в схеме работают в НАР);

3)низкий уровень помех, создаваемых по цепям пита-

ния (IПОТР практически не зависит от состояния схемы: U0 или U1);

4)высокая статическая нагрузочная способность, поскольку схема имеет высокое входное и низкое выходное сопротивления;

5)высокая технологичность, т.е. хорошая воспроизводимость параметров. Параметры схемы зависят от отношения резисторов, а не от их номиналов. Разброс отношений резисторов меньше разброса номиналов:

dR = drS + d( |

|

L |

); |

||||||||||

|

|

|

|||||||||||

R1 |

|

|

|

L1 |

|

|

L2 |

W |

|||||

|

= |

|

: |

|

|

; |

|

|

|||||

|

|

W |

|

|

|

|

|||||||

R |

2 |

|

|

|

W |

2 |

|

|

|

|

|||

|

|

|

1 |

|

|

|

|

|

|

|

|||

d( |

|

R1 |

) = 2d( |

L |

) . |

||||||||

|

|

|

|||||||||||

|

|

R |

|

|

|

|

|

W |

|||||

|

|

2 |

|

|

|

|

|

|

|

|

|

|

|

Но чтобы иметь полное представление о ЭСЛ-элементе, отметим его недостатки:

1) большая потребляемая статическая мощность (PПОТР

= UИП×I0 =

=5 В×1 мА = 5 мВт);

2)низкий логический перепад DUЛ = (0,4 - 0,8) В;

3)низкая помехозащищенность;

4)относительно большая площадь элемента. Стандартные логические уровни напряжения для ЭСЛ-элемента

при UИП = -5 В определяются как

97

|

U 0 = -1,6 В; |

||

|

U1 = -0,8 В. |

||

UОП = |

U 0 |

+U1 |

= -1,2 В. |

|

2 |

||

Опорное напряжение |

|

|

|

7.2.1. Принцип работы

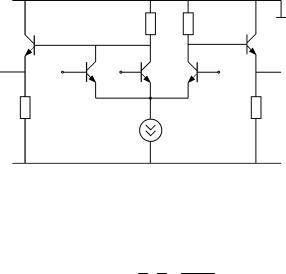

ЭСЛ-элемент состоит из переключателя тока (ПТ) и двух эмиттерных повторителей (ЭП). ПТ выполнен на транзисторах Т1, Т1', Т2 и резисторах R1 и R2. В ПТ I0 - идеальный источник тока. В электрическую схему элемента также включены эмиттерные повторители по каждому выходу - Т3, R3 и Т4, R4 (рис.7.12).

|

T3 |

R1 |

R2 |

T4 |

|

|

|

||

UF |

T1 |

T11 |

T2 |

UF |

1 |

UВХA |

UВХB |

|

2 |

|

UОП |

|

||

|

R3 |

|

|

R4 |

|

|

|

I0 |

|

−UИП

Рис.7.12. Электрическая схема ЭСЛ-элемента с двумя входами

На ПТ выполняются логические функции, указанные в табл.7.2. Из таблицы истинности получим:

F1 = A × B = A + B; F2 = A + B.

Эмиттерные повторители используются для понижения логических уровней, чтобы обеспечить НАР работы входным

98

транзисторам, и понижения выходного сопротивления, чтобы увеличить нагрузочную способность.

Таблица 7.2

Таблица истинности ЭСЛ-элемента с двумя входами

входами

A |

B |

F1 |

F2 |

|

Примечания |

|

0 |

0 |

1 |

0 |

Т1, Т11 |

- НАР (IЭ = 0), Т2 |

- НАР (IЭ = I0) |

0 |

1 |

0 |

1 |

Т1, Т2 - НАР (IЭ = 0), Т11 |

- НАР (IЭ = I0) |

|

1 |

0 |

0 |

1 |

Т11, Т2 |

- НАР (IЭ = 0), Т1 |

- НАР (IЭ = I0) |

1 |

1 |

0 |

1 |

Т1, Т11 |

- НАР (IЭ = I0/2), Т2 - НАР (IЭ = 0) |

|

Самым простым элементом, выполняющим роль источника тока, является резистор. Поэтому в схеме ЭСЛ-элемента резистор R5 является источником постоянного тока (рис.7.13).

|

T3 |

R1 |

R2 |

T4 |

|

|

|

||

UВЫХ1 |

T1 |

T11 |

T2 |

UВЫХ2 |

|

UВХ1 |

UВХ2 |

UОП |

|

|

R3 |

|

|

R4 |

|

|

R5 |

IR5 |

|

−UИП

Рис.7.13. ЭСЛ-элемент с резистором R5 в качестве источника тока

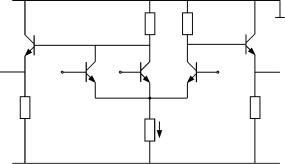

Рассмотрим работу одновходового ЭСЛ-элемента (рис.7.14).

99

|

T3 |

R1 |

R2 |

T4 |

|

|

|

|

|

||

UВЫХ1 |

|

T1 |

T2 |

|

UВЫХ2 |

|

|

UВХ |

UОП |

|

|

|

R3 |

|

|

|

R4 |

|

|

R5 |

IR5 |

|

|

−UИП

Рис.7.14. Схема одновходового ЭСЛ-элемента

Считаем, что схема абсолютно симметрична: параметры моделей пары транзисторов Т1, Т2 идентичны. Порогом срабатывания ПТ

является опорное напряжение UОП . |

|

|

|

|

|

|

||

ìU |

ВХ |

-U |

БЭТ1 |

= U |

Э |

, |

||

ï |

|

|

|

|

||||

í |

|

-U |

|

= U |

|

|

. |

|

ïU |

ОП |

БЭТ 2 |

Э |

|||||

î |

|

|

|

|

||||

Поэтому

|

|

|

|

|

UВХ = UОП -UБЭТ 2 +UБЭТ1 . |

|

|||||

1. При |

U |

ВХ |

< U |

ОП |

напряжение |

UБЭ |

Т2 |

>UБЭ |

Т1 |

, |

поэтому ток |

|

|

|

|

||||||||

I R5 = I00 протекает через транзистор Т2, работающий в НАР. Коллекторный ток, протекающий через R2, вызывает падение напряжения на нем. Таким образом, низкий уровень коллекторного

напряжения U 0 передается эмиттерным повторителем на выход

UВЫХ2 . При этом, поскольку через транзистор Т1 ток не протекает, то на резисторе R1 нет падения напряжения и высокий уровень

коллекторного напряжения U1 передается эмиттерным повтори-

телем на выход UВЫХ1 . Транзисторы Т1, Т2 работают в НАР с эмиттерными токами, равными

100

|

|

|

|

|

|

|

|

IЭТ1 |

= IЭ 0 ≈ 0; |

|

|

|

||

|

|

|

|

|

|

|

|

IЭТ 2 |

= I0. |

|

> UБЭ |

|

|

|

2. При |

U |

ВХ |

> U |

ОП |

напряжение |

UБЭ |

Т1 |

Т2 |

, поэтому ток |

|||||

|

|

|

|

|

|

|||||||||

I |

R5 |

= I1 |

протекает через транзистор Т1, |

работающий в НАР. |

||||||||||

|

|

0 |

||||||||||||

Коллекторный ток, протекающий через R1, вызывает падение напряжения на нем. Таким образом, низкий уровень коллекторного

напряжения U 0 передается эмиттерным повторителем на выход

UВЫХ1 . При этом, поскольку через транзистор Т2 ток не протекает, то на резисторе R2 нет падения напряжения и высокий уровень

коллекторного напряжения U1 передается эмиттерным повтори-

телем на выход U ВЫХ2 . Транзисторы Т1, Т2 работают в НАР с эмиттерными токами, равными

|

|

|

|

|

|

I |

ЭТ1 |

= I1; |

|

|

|

|

|

|

|

|

|

|

|

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

IЭТ 2 |

= IЭ 0 ≈ 0. |

|

|

|

|||

3. При |

U |

ВХ |

= U |

ОП |

напряжение |

UБЭ |

Т1 |

= UБЭ |

Т 2 |

, поэтому ток |

|||

|

|

|

|

|

|

||||||||

I R5 = I0 |

протекает через транзисторы Т1 |

и Т2, |

работающие в |

||||||||||

НАР, поровну. Протекающий через R1 и R2 ток вызывает падение |

|||||||||||||

напряжения. |

При этом U ВЫХ1 = U ВЫХ2 = U П , т.е. происходит |

||||||||||||

переключение логического элемента из одного состояния в другое.

Для ЭСЛ-элемента необходимо, чтобы транзисторы Т1, Т2 работали в НАР. Для этого минимальный потенциал коллектора должен быть равен максимальному потенциалу базы. Поэтому для понижения логических уровней используют эмиттерный повторитель, который понижает коллекторное напряжение ПТ на UБЭ.

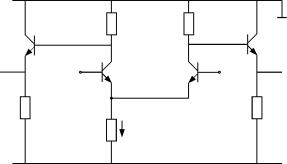

Рассмотрим работу ЭСЛ-элемента по эквивалентной схеме

(рис.7.15).

101

|

αNIЭ3 |

R1 |

R2 |

αNIЭ4 |

UВЫХ1 |

|

αNIЭ1 |

αNIЭ2 |

|

UВХ |

T1 |

T2 |

UВЫХ2 |

|

|

UОП |

|||

|

|

IЭ1 |

IЭ2 |

|

|

R3 |

|

|

R4 |

|

|

|

I0 = IR5 |

|

−UИП

Рис.7.15. Эквивалентная схема ЭСЛ-элемента

Во-первых,

UВХ = UОП -UБЭТ2 +UБЭТ1 .

Во-вторых, пренебрегая тепловыми токами, можно запи-

сать:

|

|

|

|

ìI |

ЭТ1 |

= I |

Э0 |

exp(U |

БЭТ1 |

/ j ), |

||||||

|

|

ï |

|

|

|

|

|

|

Т |

|||||||

|

|

|

|

íI |

ЭТ2 |

= IЭ0 exp(UБЭТ2 |

/ jТ ), |

|||||||||

|

|

ï |

|

|

|

+ I |

|

|

= I |

|

|

. |

|

|||

|

|

|

|

ïI |

ЭТ1 |

ЭТ2 |

|

R5 |

|

|||||||

|

|

î |

|

|

|

|

|

(7.1) |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

После решения системы получим (рис.7.16): |

||||||||||||||||

ì |

|

|

|

|

|

|

IR5 |

|

|

|

|

|

|

|

|

|

ïIЭТ1 |

= |

|

|

|

|

|

|

|

|

|

|

, |

|

|

||

|

|

|

UОП -U |

ВХ |

|

|

||||||||||

ï |

|

1 + exp |

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|||||||||

ï |

|

|

|

|

|

|

|

jТ |

|

|

|

|

|

|

||

í |

|

|

|

|

|

|

IR5 |

|

|

|

|

|

|

|

|

|

ïI |

ЭТ 2 |

= |

|

|

|

|

|

|

|

|

|

. |

|

|||

|

|

|

|

|

|

-U |

|

|

|

|||||||

ï |

|

1 + exp |

U |

ВХ |

|

ОП |

|

|

|

|

||||||

ï |

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

jТ |

|

|

|

|

|

|

|||||

î |

|

|

|

|

|

|

|

|

|

|

|

|

(7.2) |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

102