Лабораторная работа № 4

ИЗУЧЕНИЕ ДИОДНО-ТРАНЗИСТОРНЫХ (ДТЛ) И ТРАНЗИСТОРНО-ТРАНЗИСТОРНЫХ (ТТЛ) ЛОГИЧЕСКИХ СХЕМ

Цель работы: изучение принципов работы ДТЛ и ТТЛ схем, приобретение навыков аналитического расчета и экспериментального исследования их статических характеристик.

Теоретические сведения

Введение

Первые схемы диодно-транзисторной логики выпускались за несколько лет до изобретения интегральных схем. Затем с конца 50-х - начала 60-х годов их вместе с другими типами логики стали изготавливать в интегральном исполнении.

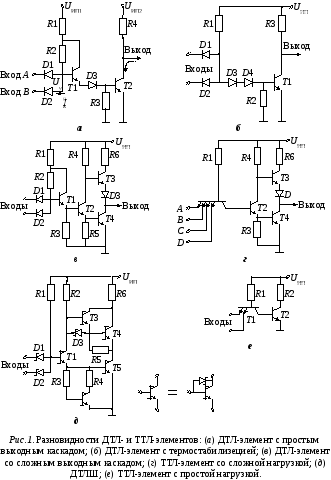

Диодно-транзисторные и транзисторно-транзисторные логические схемы являются функциональными и электрическими аналогами, которые различаются в основном конструкцией входного узла. В ДТЛ схеме входная функция “И” реализована с помощью диодов (рис.1а,б,в).

С учетом особенностей интегральной технологии в первой половине 60-х годов была предложена разновидность транзисторных схем, в которых на входе группу диодов заменил многоэмиттерный транзистор ТТЛ-схемы (рис.1,г,е). Это позволило существенно повысить быстродействие схемы. Использование одного источника питания (а в некоторых ДТЛ схемах применяются 3 источника), достаточно высокое быстродействие, высокая помехозащищенность, устойчивость к технологическому разбросу сделали ТТЛ ИС

самыми популярными и распространенными микроэлектронными изделиями 60-х -70-х годов.

К настоящему времени ТТЛ ИМС и их разновидности с диодами Шоттки (ТТЛШ) являются самыми массовыми сериями биполярных ИС малой и средней степени интеграции. В самых распространенных маломощных вентилях ТТЛШ входная логическая функция “И” реализуется на диодах Шоттки, поэтому их можно было бы именовать ДТЛШ (рис.1,д) [1,2].

Работа базовых элементов

Все

приведенные на рис.1 логические схемы

реализуют функцию И-НЕ, в частности, для

входов А

и В

на выходе имеем

![]() .

.

Рассмотрим

подробнее назначение и режимы работы

элементов ДТЛ- схемы (рис.1,а). Если на

оба входа А

и В

подано напряжение, соответствующее

логическому нулю, диоды D1

и D2

будут открыты. От источника питания

UИП1

через резисторы R1,

R2

и диоды D1,

D2

протекает ток. В состоянии логического

нуля на входе входной ток вытекает

из схемы, а потенциал общего узла анодов

диодов

![]() можно легко найти, зная

можно легко найти, зная![]() ,

,

![]() ,

,

где UD - падение напряжения на открытом диоде.

При

этом, если на входах потенциалы

различаются, то Uy

определяется более низким значением

Uвх.

Величина

![]() недостаточна

для отпирания последовательной цепочки

эмиттерный переход транзистора T1

- диод D3

- эмиттерный переход транзистора T2.

Поэтому выходной транзистор T2

закрыт, (точнее говоря, T2

работает в нормальном активном режиме

(НАР) с током эмиттера равном нулю).

Через резистор R4

ток не протекает, поэтому потенциал на

выходе Uвых

= UИП2.

Это

состояние соответствует логической

единице,

недостаточна

для отпирания последовательной цепочки

эмиттерный переход транзистора T1

- диод D3

- эмиттерный переход транзистора T2.

Поэтому выходной транзистор T2

закрыт, (точнее говоря, T2

работает в нормальном активном режиме

(НАР) с током эмиттера равном нулю).

Через резистор R4

ток не протекает, поэтому потенциал на

выходе Uвых

= UИП2.

Это

состояние соответствует логической

единице,

![]() .

(1)

.

(1)

Если

хотя бы на одном из входов (предположим,

на входе В)

повысить напряжение до величины

![]() ,

то диодD2

закроется, поскольку

,

то диодD2

закроется, поскольку

![]() .

.

Когда

на все входы одновременно подано

напряжение логической единицы

![]() ,

диодыD1

и D2

запираются, потому что теперь потенциал

Uy

ограничен сверху величиной, равной

суммарному падению напряжения на

прямо-смещенных эмиттерных переходах

транзисторов T1

и T2

и диоде D3.

Это значение

,

диодыD1

и D2

запираются, потому что теперь потенциал

Uy

ограничен сверху величиной, равной

суммарному падению напряжения на

прямо-смещенных эмиттерных переходах

транзисторов T1

и T2

и диоде D3.

Это значение

![]() .

ТранзисторT1

за счет включения резистора R2

(рис.1,а) работает в нормальном активном

режиме (НАР) и обеспечивает усиление

тока в базовой цепи транзистора T2,

благодаря чему последний входит в режим

насыщения. Напряжение на выходе

.

ТранзисторT1

за счет включения резистора R2

(рис.1,а) работает в нормальном активном

режиме (НАР) и обеспечивает усиление

тока в базовой цепи транзистора T2,

благодаря чему последний входит в режим

насыщения. Напряжение на выходе

![]() .

.

Это состояние соответствует логическому нулю

![]() .

(2)

.

(2)

Резистор

R4

ограничивает ток коллектора транзистора

T2,

предохраняя его от “сгорания”, и

позволяет повысить быстродействие

при

выключении T2.

Резистор R3

необходим для ускорения выключения

транзистора T2

при изменении напряжения на входе с

![]() .

.

Использование в данной схеме двух источников питания не обязательно. Однако, увеличение UИП1 и уменьшение UИП2 способствует повышению нагрузочной способности схемы. При этом минимальное допустимое значение UИП1 и UИП2 примерно равно падению напряжения на трех прямо смещенных р-n-переходах.

Сходный принцип работы характерен и для других схем данного класса (см. рис.1). Введение сложных выходных каскадов (рис.1в,г,д) позволяет существенно увеличить нагрузочную способность. Ряд других усовершенствований касается методов повышения быстродействия, снижения рассеиваемой мощности и т.д. Чтобы представить некоторые особенности, связанные с переходом от ДТЛ к ТТЛ-схемам, рассмотрим подробнее назначение и режимы работы элементов TТЛ-схемы со сложным выходным каскадом (рис.1,г).

Если

на все входы (эмиттеры транзистора T1)

одновременно или хотя бы на один из них

подано напряжение

![]() ,

тоT1

работает в режиме насыщения с током

коллектора, равным нулю (ток не может

втекать в базy

транзистора T2).

Потенциал коллектора T1

,

тоT1

работает в режиме насыщения с током

коллектора, равным нулю (ток не может

втекать в базy

транзистора T2).

Потенциал коллектора T1

![]() ,

,

который не превышает граничного напряжения UБЭгр2, и поэтому не дает возможности открыться транзистору T2. Следовательно, ток через T2 практически не протекает, и он работает в нормальном активном режиме с током эмиттера IЭ2 = 0. Поскольку падение напряжения на резисторе R3 также равно нулю, транзистор T4 закрыт, a через резистор R2 протекает только ток базы T3, создавая незначительное падение напряжения на R2, которым во многих случаях можно пренебречь. Транзистор T3 работает в НАР, диод D также открыт. Это состояние соответствует логической единице на выходе схемы:

![]() .

.

В том

случае, когда на входы одновременно

поданы потенциалы

![]() ,

эмиттерные

переходы транзистора T1

запираются, и он переходит в инверсный

активный режим (ИАР). Ток из коллектора

T1

втекает в базу транзистора T2,

включая последний и вводя его в насыщение.

Ток, протекающий через резистор R3,

повышает потенциал базы транзистора

T4,

отпирая его и вводя в режим насыщения.

С другой стороны, коллекторный ток

транзистора T2

создает большое падение напряжения на

R2.

За счет этого потенциал базы T3

понижается, и он закрывается. Для того,

чтобы надежно запереть транзистор

T3

при

,

эмиттерные

переходы транзистора T1

запираются, и он переходит в инверсный

активный режим (ИАР). Ток из коллектора

T1

втекает в базу транзистора T2,

включая последний и вводя его в насыщение.

Ток, протекающий через резистор R3,

повышает потенциал базы транзистора

T4,

отпирая его и вводя в режим насыщения.

С другой стороны, коллекторный ток

транзистора T2

создает большое падение напряжения на

R2.

За счет этого потенциал базы T3

понижается, и он закрывается. Для того,

чтобы надежно запереть транзистор

T3

при

![]() ,

последовательно с его эмиттерным

переходом включен диодD.

Это состояние эквивалентно логическому

нулю на выходе схемы

,

последовательно с его эмиттерным

переходом включен диодD.

Это состояние эквивалентно логическому

нулю на выходе схемы

![]() ,

,

где

![]() - напряжение коллектор-эмиттер насыщения

транзистора без учета падения

напряжения наrK;

rK

- сопротивление тела коллектора (в

указанном случае транзистора T4);

- напряжение коллектор-эмиттер насыщения

транзистора без учета падения

напряжения наrK;

rK

- сопротивление тела коллектора (в

указанном случае транзистора T4);

![]() - ток в цепи коллектораT4,

который втекает в него (рис.1,г). Резистор

R4

ограничивает ток в момент переходного

процесса, когда открыты оба транзистора

Т3

и Т4.

- ток в цепи коллектораT4,

который втекает в него (рис.1,г). Резистор

R4

ограничивает ток в момент переходного

процесса, когда открыты оба транзистора

Т3

и Т4.

Режимы работы элементов остальных логических схем приведены в таблице 1.

Расчет токов ДТЛ схемы

Рассмотрим

схему, изображенную на рис.1,а. Если на

какой-либо вход подано напряжение

![]() ,

соответствующий диод открыт, и входной

ток вытекает из схемы. В этом случае

транзисторT1

закрыт.

,

соответствующий диод открыт, и входной

ток вытекает из схемы. В этом случае

транзисторT1

закрыт.

Предположим, что диоды D1 и D2 одинаковы и открыты. Тогда по входам А и В протекают равные токи

![]() ,

,

а суммарный ток, протекающий через резисторы R1 и R2, равен

![]() .

(3)

.

(3)

Таблица 1