- •Аннотация

- •1.2. Программные модули

- •2.1. Способы описания проектов бис.

- •Техническое задание

- •2.2. Подготовка описания тестовых воздействий для моделирования работы бис.

- •2.3. Этапы отладки проекта плис

- •3.1. Графический ввод и редактирование схемы

- •3.2 Ввод и редактирование тестов

- •3.3. Программа моделирование

- •3.4 Программатор плис.

- •4. Проектирование плис в базисе примитивов.

- •4.1. Мультиплексор Мультиплексор представляют собой логическую схему,имеющуюnсигнальных входов,mвходов адреса и один выходQ.

- •4.2. Шифратор Шифратор представляют собой логическую схему, имеющую nвходов иmвыходов

- •4.3. Демультиплексор Демультиплексор представляют собой логическую схему, имеющую один информационный вход, mвходов адреса иnвыходов.

- •Обычно выполняется соотношение

- •4.5. Сумматоры

- •Выходами одноразрядного сумматора являются выход суммы текущего разряда (s) и выход переноса в следующий разряд (p).

- •4.6. Вычитатели

- •Выходами одноразрядного вычитателя являются выход разности текущего разряда (r) и выход заёма в старшем разряде (z).

- •4.7. Асинхронные счетчики.

- •4.8. Синхронные счетчики

- •4.9. Последовательные сумматоры и вычитатели.

- •4.10. Дешифратор Дешифратор представляют собой логическую схему, имеющую nвходов иmвыходов

- •5. Проектирование плис с использованием lpm модулей

- •5.1 Lpm модуль счетчика

- •5.2 Lpm модуль сдвигового регистра.

- •5.3 Lpm модуль пзу.

- •6. Описание работы схем на поведенческом языке ahdl.

- •6.1. Введение в язык ahdl

- •В языке ahdl допускается числа следующих типов.

- •Выражения

- •6.2. Структура текстового описания бис на языке ahdl

- •6.3. Основные элементы языка.

- •6.3.1 Булевы уравнения, группы.

- •In0, in21, in3 : input;

- •In_f, in_s, in_t : input;

- •If in_f then

- •In[2..0] : input;

- •6.3.3 Проектирование на языке ahdl с помощью таблиц истинности.

- •In[2..0] : input;

- •6.3.4 Операторы If Generate, For Generate

- •Else generate

- •Variable

- •6.3.5. Проектирование на языке ahdl с использованием примитивов.

- •Оператор непосредственного обращения к примитиву имеет следующий вид:

- •Variable

- •7.5. Сумматоры

- •Subdesign suma

- •Variable

- •7.6. Вычитатели

- •Variable

- •7.7. Шинные формирователи

- •Subdesign shina

- •Variable

- •7.8. Счетчики

- •Variable

- •7.9. Дешифраторы

- •7.10. Компараторы

7.5. Сумматоры

Рассмотрим схему четырехразрядного сумматора, описанную на языке AHDL. Разрядность сумматора задаётся параметром NB. Сумматор имеет входные группа сигналов шины A[NB..1] и B[NB..1], выходную группу сигнала суммы S[NB..1] и сигнал выхода переноса cout из старшего разряда. Представленный сумматор реализован по стандартной схеме на базе одноразрядных сумматоров. Булевы уравнения, заданные в векторном виде, имеют стандартный вид и выглядят следующим:

Si= AiBiPi-1

Pi+1=AiBi+ AiPi-1+BiPi-1

Описание сумматора имеет следующий вид.

CONSTANT NB=4;

Subdesign suma

( A[NB..1]:INPUT;

B[NB..1]:INPUT;

S[NB..1],cout:OUTPUT;

)

Variable

Per[NB..1] :NODE;

BEGIN

S1=A1$B1;

Per1=A1&B1;

S[NB..2]=A[NB..2]$B[NB..2]$Per[(NB-1)..1];

Per[NB..2]=A[NB..2]&B[NB..2] # Per[(NB-1)..1]&(A[NB..2]#B[NB..2]);

cout = Per[NB];

END;

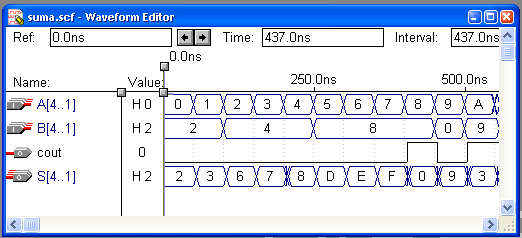

Н иже,

на рис 7.5 приведена временная диаграмма

работы сумматора.

иже,

на рис 7.5 приведена временная диаграмма

работы сумматора.

Рис. 7.5. Временная диаграмма работы сумматора.

7.6. Вычитатели

Рассмотрим схему четырехразрядного вычитателя, описанную на языке AHDL. Разрядность вычитателя задаётся параметром NB. Сумматор имеет входные группа сигналов шины A[NB..1] - (уменьшаемое) и B[NB..1] - (вычитаемое), выходную группу сигнала разности S[NB..1] и сигнал выхода заёма cout из старшего разряда. Представленный вычитатель реализован по стандартной схеме на базе одноразрядных вычитателей. Булевы уравнения, заданные в векторном виде, имеют стандартный вид и выглядят следующим:

Si=

AiBiPi-1

Si=

AiBiPi-1

___

_

_

_______

Pi+1=AiBi+

AiPi-1+BiPi-1

Описание вычитателя имеет следующий вид.

CONSTANT NB=4;

SUBDESIGN RAZ

( A[NB..1]:INPUT;

B[NB..1]:INPUT;

S[NB..1],cout:OUTPUT;)

Variable

Per[NB..1] :NODE;

BEGIN

S1=A1$B1;

Per1=!A1&B1;

S[NB..2]=A[NB..2]$B[NB..2]$Per[(NB-1)..1];

Per[NB..2]=!A[NB..2]&B[NB..2] # Per[(NB-1)..1]&(!A[NB..2]#B[NB..2]);

cout = Per[NB];

END;

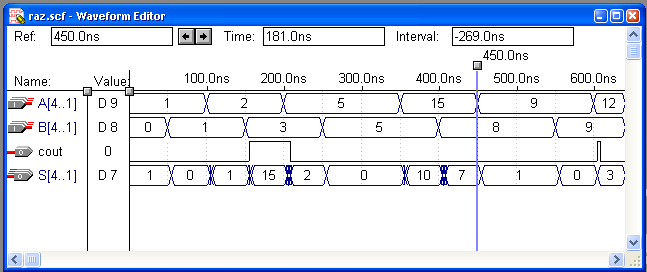

Ниже, на рис 7.6 приведена временная диаграмма работы вычитателя.

Рис. 7.6. Временная диаграмма работы вычитателя.

7.7. Шинные формирователи

Шинные приёмо-передатчики позволяют организовать передачу и приём информации между несколькими источниками и приёмниками по общей шине данных. В каждый момент времени на общей шине данных может быть активен только один источник сигнала. Управлением работой шинных формирователей осуществляет специальное логическое устройство, называемое арбитром.

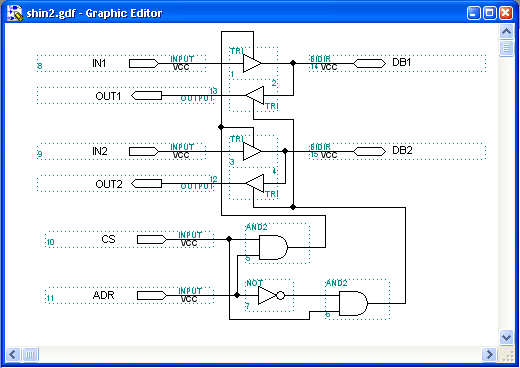

Рассмотрим схему типичного шинного приёмо-передатчика, представленную на рис 7.7.1.

Рис 7.7.1. Схема типичного шинного приёмо-передатчика.

Представленная схема шинного приёмо-передатчика имеет двунаправленную шину данных DB1, DB2. При различных комбинациях сигналов управления CS и ADR возможны следующие режимы передачи данных:

сигнал IN передается на шину DB и на шину OUT;

сигнал IN передается на шину DB, шина OUT отключена;

сигнал DB и на шину OUT;

шина OUT отключена.

Ниже приведен текст описания работы шинного приёмо-передатчика нa языке AHDL.

Subdesign shina

( IN1,IN2,CS,ADR: INPUT;

DB1,DB2:BIDIR;

OUT1,OUT2: OUTPUT;)