- •1.Электропроводность полупроводников (собственная и примесная), полупроводники n и p типа

- •2.Параметры p – n перехода. Вах.Виды пробоя.

- •4.Выпрямительный диод и стабилитрон

- •5. Биполярный транзисторах: характеристика,схемы вкл и параметры

- •8.Полевые транзисторы мдп-типа, принцип работы, осн.Хар-ки

- •9.Тиристоры

- •10. Однофазный однополупериодный выпрямитель

- •11.Однофазный мостовой выпрямитель.

- •14. Мостовой трехвазный выпрямитель.Схема Ларионова

- •15.Сглаживающие фильтры

- •16.Стабилизаторы постоянного напряжения.

- •18. Однофазный упарвляемый выпрямитель:работа на активную нагрузку

- •17.Стабилизаторы постоянного тока

- •43. T-триггер

- •45.Регистры. Параллельный регистр памяти

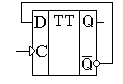

43. T-триггер

T-триггер —

это счетный триггер.

У данного триггера имеется только один

вход. Принцип работы T-триггера заключается

в следующем. После поступления на вход

T импульса, состояние триггера меняется

на прямо противоположное. Счётным он

называется потому, что T триггер как

бы подсчитывает количество импульсов,

поступивших на его вход. Жаль только,

что считать этот триггер умеет только

до одного. При поступлении второго

импульса T-триггер снова сбрасывается

в исходное состояние.T-триггеры

строятся только на базе двухступенчатых

триггеров, подобных рассмотренному

ранее D триггеру. Использование двух

триггеров позволяет избежать

неопределенного состояния схемы при

разрешающем потенциале на входе

синхронизации "C", так как счетные

триггеры строятся при помощи схем с

обратной связью.T триггер

можно синтезировать из любого

двухступенчатого триггера. Рассмотрим

пример синтеза T триггера из

динамического D триггера. Для того

чтобы превратить D триггер

в счётный, необходимо ввести цепь

обратной связи с инверсного выхода

этого триггера на вход, как показано на

рисунке 1.

T-триггер —

это счетный триггер.

У данного триггера имеется только один

вход. Принцип работы T-триггера заключается

в следующем. После поступления на вход

T импульса, состояние триггера меняется

на прямо противоположное. Счётным он

называется потому, что T триггер как

бы подсчитывает количество импульсов,

поступивших на его вход. Жаль только,

что считать этот триггер умеет только

до одного. При поступлении второго

импульса T-триггер снова сбрасывается

в исходное состояние.T-триггеры

строятся только на базе двухступенчатых

триггеров, подобных рассмотренному

ранее D триггеру. Использование двух

триггеров позволяет избежать

неопределенного состояния схемы при

разрешающем потенциале на входе

синхронизации "C", так как счетные

триггеры строятся при помощи схем с

обратной связью.T триггер

можно синтезировать из любого

двухступенчатого триггера. Рассмотрим

пример синтеза T триггера из

динамического D триггера. Для того

чтобы превратить D триггер

в счётный, необходимо ввести цепь

обратной связи с инверсного выхода

этого триггера на вход, как показано на

рисунке 1.

44.

JK-триггеры

JK-триггеры подразделяются

на универсальные и комбинированные.

Универсальный JK-триггер имеет два

информационных входа J и K. По входу J

триггер устанавливается в состояние

Q=1, /Q=0, а по входу K-в состояние Q=0, /Q=1.

JK-триггер отличается от RS-триггера

прежде всего тем что в нем устранена

неопределенность, которая возникает в

RS-триггере при определенной комбинации

входных сигналов. Универсальность

JK-триггера состоит в том, что он может

выполнять функции RS-, Т- и D-триггеров.

Комбинированный JK-триггер отличается

от универсального наличием дополнительных

асинхронных входов S и R для предварительной

установки триггера в определенное

состояние (логической 1 или 0).Простейший

JK-триггер можно получить из синхронного

RS-триггера с динамическим управлением,

если ввести дополнительные обратные

связи с выходов триггера на входы,

которые позволяют устранить неопределенность

в таблице состояний (рис. 2.50.а). Рис.

2.50.a. Преобразование синхронного

RS-триггера в JK-триггер

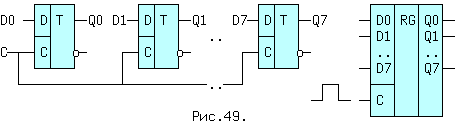

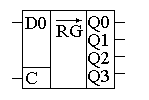

45.Регистры. Параллельный регистр памяти

Регистр предназначен для хранения многоразрядных двоичных чисел (слов). Кроме хранения, регистр может осуществлять сдвиг принятого слова, преобразование параллельного кода в последовательный и наоборот, преобразование кода из прямого в обратный (когда единицы заменяются нулями, а нули — единицами) и наоборот, и некоторые арифметические и логические операции. В соответствии со способом ввода и вывода разрядов числа различают регистры параллельные, последовательные и комбинированные. В параллельном регистре (регистре памяти) ввод и вывод слова осуществляется в параллельной форме — одновременно всех разрядов, в последовательном (сдвиговом) регистре разряды числа вводятся и выводятся последовательно, в комбинированном регистре ввод числа осуществляется в параллельной форме, а вывод в последовательной или наоборот.Регистры с параллельной записью называются, также регистрами памяти. В них могут использоваться, как прозрачные "защелки" , так и триггеры сдинамическим управлением . На рис.49 приведена схема 8-ми разрядного регистра памяти с общим входом управления записью информацией и ее условное обозначение. Высокий уровень на входе C переписывает информацию с входа на выход (Qi=Di), а низкий уровень - защелкивает данные.

4 6.Последовательный

сдвиговый регистр Последовательный

регистр (регистр сдвига или сдвиговый

регистр) обычно служит для преобразования

последовательного кода в параллельный

и наоборот. Применение последовательного

кода связано с необходимостью передачи

большого количества двоичной информации

по ограниченному количеству соединительных

линий. При параллельной передаче разрядов

требуется большое количество соединительных

проводников. Если двоичные разряды

последовательно бит за битом передавать

по одному проводнику, то можно значительно

сократить размеры соединительных линий

на плате (и размеры корпусов микросхем).

6.Последовательный

сдвиговый регистр Последовательный

регистр (регистр сдвига или сдвиговый

регистр) обычно служит для преобразования

последовательного кода в параллельный

и наоборот. Применение последовательного

кода связано с необходимостью передачи

большого количества двоичной информации

по ограниченному количеству соединительных

линий. При параллельной передаче разрядов

требуется большое количество соединительных

проводников. Если двоичные разряды

последовательно бит за битом передавать

по одному проводнику, то можно значительно

сократить размеры соединительных линий

на плате (и размеры корпусов микросхем).

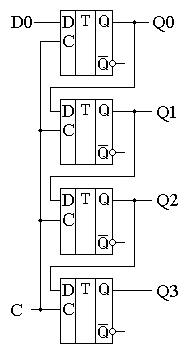

С двиговый

регистр построен на четырех D триггерах

с динамической блокировкой входов. Для

управления регистром сформированы:

вход С -- вход синхронизации и вход R --

общий сброс регистра. Информационным

входом регистра является вход D первого

триггера (обозначен - DS).Кроме

параллельного соединения триггеров

для построения регистров используются

последовательное соединение этих

элементов.Входы

синхронизации в последовательных

(сдвиговых) регистрах, как и в параллельных

регистрах, объединяются. Это обеспечивает

одновременность смены состояния всех

триггеров, входящих в состав

последовательного (сдвигового) регистра.Условно-графическое

обозначение последовательного

(сдвигового) регистра

двиговый

регистр построен на четырех D триггерах

с динамической блокировкой входов. Для

управления регистром сформированы:

вход С -- вход синхронизации и вход R --

общий сброс регистра. Информационным

входом регистра является вход D первого

триггера (обозначен - DS).Кроме

параллельного соединения триггеров

для построения регистров используются

последовательное соединение этих

элементов.Входы

синхронизации в последовательных

(сдвиговых) регистрах, как и в параллельных

регистрах, объединяются. Это обеспечивает

одновременность смены состояния всех

триггеров, входящих в состав

последовательного (сдвигового) регистра.Условно-графическое

обозначение последовательного

(сдвигового) регистра

![]() 47.Счетчик

импульсов.Суммирующий счетчик импульсов

на Т-триггерах. Электронный

счетчик импульсов

предназначен для подсчета количества

импульсов, поступающих с измерительных

датчиков

на счетные входы (или один счетный вход)

счетчика импульсов и пересчета их в

требуемые физические единицы измерения

путем умножения на заданный множитель

(например, в метры, литры, штуки, килограммы

и т. д.); подсчета суммарной выработки

за смену, сутки, неделю, месяц и т. д.;

управления исполнительными механизмами

одним или несколькими дискретными

выходами (чаще всего, в счетчиках

импульсов в качестве дискретного выхода

используется реле

или оптопара).

Электронные счетчики импульсов сохраняют

результат измерений при исчезновении

напряжения питания в течение неограниченного

периода времени в энергонезависимой

памяти (EEPROM).

После возврата напряжения питания счет

импульсов продолжается, начиная с

сохраненного значения; некоторые модели

счетчиков импульсов идентифицируют

факт пропадания напряжения питания во

время работы. Кроме того, счётчики

импульсов классифицируют по направлению

счета (режиму работы):суммирующие

счетчики импульсов;вычитающие счетчики

импульсов;реверсивные счетчики импульсов.

Двоичные

счетчики.

Начнем с двоичных счетчиков. Для их

построения можно использовать различные

типы триггеров. Наиболее удобным является

триггер Т-типа (счетный триггер), который

осуществляет подсчет импульсов по

модулю 2. Такой триггер по сути дела

является простейшим счетчиком с Ксч=2.

Соединив несколько счетных триггеров

определенным образом, можно получить

схему многоразрядного счетчика. Если

в качестве базовых используются

Т-триггеры с прямым динамическим счетным

входом, то для построения трехразрядного

суммирующего двоичного счетчика, их

необходимо объединить так, как это

показано на рис.

5.14,а.

Срабатывание всех триггеров происходит

по переднему фронту счетного импульса.

Поэтому, чтобы реализовать операцию

суммирования, необходимо на триггеры

Т2 и Т3 информацию подавать с инверсных

выходовпредыдущих триггеров.

47.Счетчик

импульсов.Суммирующий счетчик импульсов

на Т-триггерах. Электронный

счетчик импульсов

предназначен для подсчета количества

импульсов, поступающих с измерительных

датчиков

на счетные входы (или один счетный вход)

счетчика импульсов и пересчета их в

требуемые физические единицы измерения

путем умножения на заданный множитель

(например, в метры, литры, штуки, килограммы

и т. д.); подсчета суммарной выработки

за смену, сутки, неделю, месяц и т. д.;

управления исполнительными механизмами

одним или несколькими дискретными

выходами (чаще всего, в счетчиках

импульсов в качестве дискретного выхода

используется реле

или оптопара).

Электронные счетчики импульсов сохраняют

результат измерений при исчезновении

напряжения питания в течение неограниченного

периода времени в энергонезависимой

памяти (EEPROM).

После возврата напряжения питания счет

импульсов продолжается, начиная с

сохраненного значения; некоторые модели

счетчиков импульсов идентифицируют

факт пропадания напряжения питания во

время работы. Кроме того, счётчики

импульсов классифицируют по направлению

счета (режиму работы):суммирующие

счетчики импульсов;вычитающие счетчики

импульсов;реверсивные счетчики импульсов.

Двоичные

счетчики.

Начнем с двоичных счетчиков. Для их

построения можно использовать различные

типы триггеров. Наиболее удобным является

триггер Т-типа (счетный триггер), который

осуществляет подсчет импульсов по

модулю 2. Такой триггер по сути дела

является простейшим счетчиком с Ксч=2.

Соединив несколько счетных триггеров

определенным образом, можно получить

схему многоразрядного счетчика. Если

в качестве базовых используются

Т-триггеры с прямым динамическим счетным

входом, то для построения трехразрядного

суммирующего двоичного счетчика, их

необходимо объединить так, как это

показано на рис.

5.14,а.

Срабатывание всех триггеров происходит

по переднему фронту счетного импульса.

Поэтому, чтобы реализовать операцию

суммирования, необходимо на триггеры

Т2 и Т3 информацию подавать с инверсных

выходовпредыдущих триггеров.

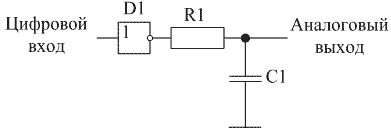

4 8.

Цифро-аналоговый преобразователь,

Аналого-цифровой

преобразователь.

Цифро-аналоговый преобразователь (ЦАП)

- это устройство для преобразования

цифрового кода в аналоговый сигнал по

величине, пропорциональной значению

кода. ЦАП применяются для связи цифровых

управляющих систем с устройствами,

которые управляются уровнем аналогового

сигнала. Также, ЦАП является составной

частью во многих структурах аналого-цифровых

устройств и преобразователей. ЦАП

характеризуется функцией преобразования.

Она связывает изменение цифрового кода

с изменением напряжения или тока.

Простейшим цифроаналоговым преобразователем

(ЦАП) является одноразрядный преобразователь.

В качестве такого ЦАП может служить

простой усилитель-ограничитель, в

качестве которого можно применить

логический инвертор. Схема такого

цифро-аналогового преобразователя

приведена на рисунке . Одноразрядный

ЦАП преобразует в аналоговую форму знак

числа. Для цифро-аналогового преобразования

на очень высокой частоте дискретизации,

во много раз превышающей частоту

Котельникова, такого ЦАП вполне

достаточно, однако, в большинстве случаев

для цифро-аналогового преобразования

требуется большее количество разрядов.

ЦАП можно реализовать с помощью

суммирования токов, суммирования

напряжений и деления напряжений. В

первом и втором случае в соответствии

со значениями разрядов входного кода,

суммируются сигналы генераторов токов

и источников Э.Д.С. Последний способ

представляет собой управляемый кодом

делитель напряжения. Два последних

способа не нашли широкого распространения

в связи с практическими трудностями их

реализации. Аналого-цифровой

преобразователь—

устройство, преобразующее входной

аналоговый

сигнал

в дискретный код (цифровой

сигнал).

Обратное преобразование осуществляется

при помощи ЦАП (цифро-аналогового

преобразователя,

DAC). Как правило, АЦП — электронное

устройство, преобразующее напряжение

в двоичный цифровой код. Тем не менее,

некоторые неэлектронные устройства с

цифровым выходом, следует также относить

к АЦП, например, некоторые типы

преобразователей

угол-код.

Простейшим одноразрядным двоичным АЦП

является компаратор.

По способу применяемых алгоритмов АЦП

делят на:Последовательные прямого

перебора,Последовательного приближения,

Последовательные с сигма-дельта-модуляцией,

Параллельные одноступенчатые, Параллельные

двух- и более ступенчатые (конвейерные).

Передаточная характеристика АЦП —

зависимость числового эквивалента

выходного двоичного кода от величины

входного аналогового сигнала. Говорят

о линейных и нелинейных АЦП. Такое

деление условное. Обе передаточные

характеристики — ступенчатые. Но

для «линейных» АЦП всегда возможно

провести такую прямую линию, чтобы все

точки передаточной характеристики,

соответствующие входным значениям

delta*2^k (где delta — шаг дискретизации, k

лежит в диапазоне 0..N, где N — разрядность

АЦП) были от неё равноудалены. Большинство

АЦП считаются линейными,

хотя аналого-цифровое преобразование

по сути является нелинейным процессом

(поскольку операция отображения

непрерывного пространства в дискретное —

операция нелинейная). Одним из важнейших

параметров аналого-цифровых преобразователей

является разрядность его выходных

данных. Именно этот параметр обеспечивает

отношение сигнал/шум преобразования и

в конечном итоге динамический диапазон

цифрового сигнала. Разрядность АЦП

стараются увеличивать для увеличения

отношения сигнал/шум. Отношение сигнал/шум

аналого-цифрового преобразователя

можно определить по следующей формуле:

SN = N

× 6 + 3,5 (дБ) где N —

количество двоичных разрядов на выходе

АЦП.

8.

Цифро-аналоговый преобразователь,

Аналого-цифровой

преобразователь.

Цифро-аналоговый преобразователь (ЦАП)

- это устройство для преобразования

цифрового кода в аналоговый сигнал по

величине, пропорциональной значению

кода. ЦАП применяются для связи цифровых

управляющих систем с устройствами,

которые управляются уровнем аналогового

сигнала. Также, ЦАП является составной

частью во многих структурах аналого-цифровых

устройств и преобразователей. ЦАП

характеризуется функцией преобразования.

Она связывает изменение цифрового кода

с изменением напряжения или тока.

Простейшим цифроаналоговым преобразователем

(ЦАП) является одноразрядный преобразователь.

В качестве такого ЦАП может служить

простой усилитель-ограничитель, в

качестве которого можно применить

логический инвертор. Схема такого

цифро-аналогового преобразователя

приведена на рисунке . Одноразрядный

ЦАП преобразует в аналоговую форму знак

числа. Для цифро-аналогового преобразования

на очень высокой частоте дискретизации,

во много раз превышающей частоту

Котельникова, такого ЦАП вполне

достаточно, однако, в большинстве случаев

для цифро-аналогового преобразования

требуется большее количество разрядов.

ЦАП можно реализовать с помощью

суммирования токов, суммирования

напряжений и деления напряжений. В

первом и втором случае в соответствии

со значениями разрядов входного кода,

суммируются сигналы генераторов токов

и источников Э.Д.С. Последний способ

представляет собой управляемый кодом

делитель напряжения. Два последних

способа не нашли широкого распространения

в связи с практическими трудностями их

реализации. Аналого-цифровой

преобразователь—

устройство, преобразующее входной

аналоговый

сигнал

в дискретный код (цифровой

сигнал).

Обратное преобразование осуществляется

при помощи ЦАП (цифро-аналогового

преобразователя,

DAC). Как правило, АЦП — электронное

устройство, преобразующее напряжение

в двоичный цифровой код. Тем не менее,

некоторые неэлектронные устройства с

цифровым выходом, следует также относить

к АЦП, например, некоторые типы

преобразователей

угол-код.

Простейшим одноразрядным двоичным АЦП

является компаратор.

По способу применяемых алгоритмов АЦП

делят на:Последовательные прямого

перебора,Последовательного приближения,

Последовательные с сигма-дельта-модуляцией,

Параллельные одноступенчатые, Параллельные

двух- и более ступенчатые (конвейерные).

Передаточная характеристика АЦП —

зависимость числового эквивалента

выходного двоичного кода от величины

входного аналогового сигнала. Говорят

о линейных и нелинейных АЦП. Такое

деление условное. Обе передаточные

характеристики — ступенчатые. Но

для «линейных» АЦП всегда возможно

провести такую прямую линию, чтобы все

точки передаточной характеристики,

соответствующие входным значениям

delta*2^k (где delta — шаг дискретизации, k

лежит в диапазоне 0..N, где N — разрядность

АЦП) были от неё равноудалены. Большинство

АЦП считаются линейными,

хотя аналого-цифровое преобразование

по сути является нелинейным процессом

(поскольку операция отображения

непрерывного пространства в дискретное —

операция нелинейная). Одним из важнейших

параметров аналого-цифровых преобразователей

является разрядность его выходных

данных. Именно этот параметр обеспечивает

отношение сигнал/шум преобразования и

в конечном итоге динамический диапазон

цифрового сигнала. Разрядность АЦП

стараются увеличивать для увеличения

отношения сигнал/шум. Отношение сигнал/шум

аналого-цифрового преобразователя

можно определить по следующей формуле:

SN = N

× 6 + 3,5 (дБ) где N —

количество двоичных разрядов на выходе

АЦП.

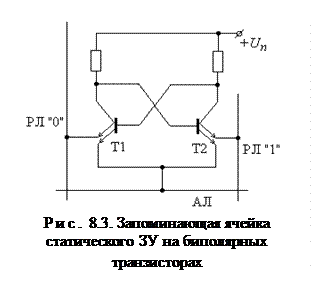

4 9.Элементы

памяти ОЗУ.Элементы

памяти статистического ОЗУ.

ЭП биполярного ОЗУ представляет собой

асинхронный RS-триггер, построенный из

двух логических элементов И-НЕ,

выполненных на двух двухэмиттерных

транзисторах. подключен к двум разряд-ным

линиям РЛ “0” и РЛ “1” и адресной линии

АЛ. В зави-симости от комбинации

на-пряжений на этих линиях ЭП может

работать в режимах хранения, записи и

считыва-ния информации. Запоминающие

устройства (ЗУ) служат для приема,

хранения и выдачи информации. Запоминающие

устройства по выполняемым функциям

делятся на оперативные

и постоянные.

Оперативные запоминающие устройства

(ОЗУ) осуществляют запись, хранение и

считывание информации и работают только

при включенном питании, т. е. ОЗУ являются

энергозависимыми.

Постоянные запоминающие устройства

(ПЗУ) хранят информацию при отключении

питания, т. е. ПЗУ являются энергонезависимыми.

ОЗУ по виду хранения информации

разделяются на статические

и динамические.

В статическом ОЗУ в качестве элемента

памяти используется триггер,

в динамическом - конденсатор.

По-буржуйски ОЗУ называется RAM (random

access memory - память с произвольным доступом).

Статическое ОЗУ соответственно SRAM,

динамическое DRAM. ОЗУ работают в режимах

записи, хранения и считывания информации.

ОЗУ применяются для хранения кодов

выполняемых программ и промежуточных

результатов обработки информации. В

запоминающих устройствах статического

типа в качестве элементов памяти

используют триггеры на биполярных или

полевых транзисторах. Большее

быстродействие имеют устройства на

биполярных транзисторах. В качестве

запоминающего элемента микросхем памяти

статического типа может быть использован,

например, D-триггер,

снабженный специальным входом разрешения.

По режиму

доступа микросхемы статических ОЗУ

подразделяются на тактируемые и

нетактируемые (асинхронные). Тактируемые

микросхемы ОЗУ при каждом обращении к

любой ячейке памяти требуют подачи

импульса на вход CS.

Сигналы разрешения выхода, записи-считывания

могут быть поданы импульсом или уровнем.

Всем компьютерам требуется место для

временного хранения информации во время

обработки других фрагментов информации.

Обычно в цифровых компьютерах хранение

информации выполняется на двух различных

уровнях: в первичной памяти (построенной

на полупроводниковых чипах ОЗУ и ПЗУ)

и в памяти для хранения больших объемов

информации (обычно использующей жесткие

диски) Большая часть первичной памяти

системы располагается на системной

плате. На системной плате первичная

память существует, как правило, в двух

или трех формах:1) Постоянное запоминающее

устройство (ПЗУ). Содержит постоянные

программы начального запуска компьютера.

2)Оперативное запоминающее устройство

(ОЗУ). Эта память имеет достаточно высокое

быстродействие, чтобы взаимодействовать

непосредственно с процессором, и

допускает считывание и запись в него с

любой требуемой частотой. 3)Кэш-память.

Быстродействующая система ОЗУ,

предназначенная специально для хранения

информации, которая, скорее всего, будет

использована процессором.

9.Элементы

памяти ОЗУ.Элементы

памяти статистического ОЗУ.

ЭП биполярного ОЗУ представляет собой

асинхронный RS-триггер, построенный из

двух логических элементов И-НЕ,

выполненных на двух двухэмиттерных

транзисторах. подключен к двум разряд-ным

линиям РЛ “0” и РЛ “1” и адресной линии

АЛ. В зави-симости от комбинации

на-пряжений на этих линиях ЭП может

работать в режимах хранения, записи и

считыва-ния информации. Запоминающие

устройства (ЗУ) служат для приема,

хранения и выдачи информации. Запоминающие

устройства по выполняемым функциям

делятся на оперативные

и постоянные.

Оперативные запоминающие устройства

(ОЗУ) осуществляют запись, хранение и

считывание информации и работают только

при включенном питании, т. е. ОЗУ являются

энергозависимыми.

Постоянные запоминающие устройства

(ПЗУ) хранят информацию при отключении

питания, т. е. ПЗУ являются энергонезависимыми.

ОЗУ по виду хранения информации

разделяются на статические

и динамические.

В статическом ОЗУ в качестве элемента

памяти используется триггер,

в динамическом - конденсатор.

По-буржуйски ОЗУ называется RAM (random

access memory - память с произвольным доступом).

Статическое ОЗУ соответственно SRAM,

динамическое DRAM. ОЗУ работают в режимах

записи, хранения и считывания информации.

ОЗУ применяются для хранения кодов

выполняемых программ и промежуточных

результатов обработки информации. В

запоминающих устройствах статического

типа в качестве элементов памяти

используют триггеры на биполярных или

полевых транзисторах. Большее

быстродействие имеют устройства на

биполярных транзисторах. В качестве

запоминающего элемента микросхем памяти

статического типа может быть использован,

например, D-триггер,

снабженный специальным входом разрешения.

По режиму

доступа микросхемы статических ОЗУ

подразделяются на тактируемые и

нетактируемые (асинхронные). Тактируемые

микросхемы ОЗУ при каждом обращении к

любой ячейке памяти требуют подачи

импульса на вход CS.

Сигналы разрешения выхода, записи-считывания

могут быть поданы импульсом или уровнем.

Всем компьютерам требуется место для

временного хранения информации во время

обработки других фрагментов информации.

Обычно в цифровых компьютерах хранение

информации выполняется на двух различных

уровнях: в первичной памяти (построенной

на полупроводниковых чипах ОЗУ и ПЗУ)

и в памяти для хранения больших объемов

информации (обычно использующей жесткие

диски) Большая часть первичной памяти

системы располагается на системной

плате. На системной плате первичная

память существует, как правило, в двух

или трех формах:1) Постоянное запоминающее

устройство (ПЗУ). Содержит постоянные

программы начального запуска компьютера.

2)Оперативное запоминающее устройство

(ОЗУ). Эта память имеет достаточно высокое

быстродействие, чтобы взаимодействовать

непосредственно с процессором, и

допускает считывание и запись в него с

любой требуемой частотой. 3)Кэш-память.

Быстродействующая система ОЗУ,

предназначенная специально для хранения

информации, которая, скорее всего, будет

использована процессором.

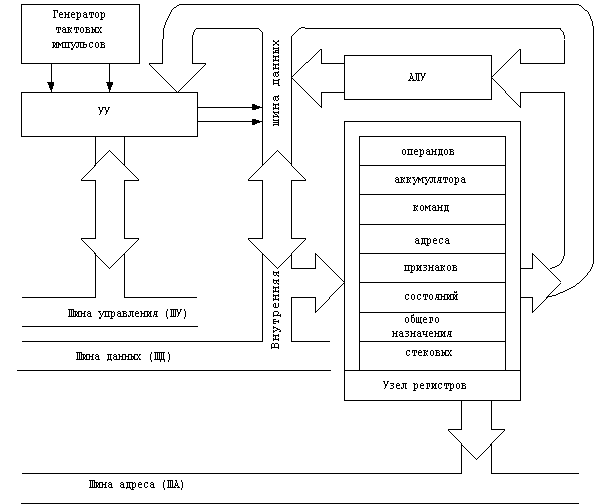

50.Микропроцессоры:

структурная схема и назначение ее

элементов Микропроце́ссор —

процессор

(устройство, отвечающее за выполнение

арифметических, логических операций и

операций управления, записанных в

машинном

коде),

реализованный в виде одной микросхемы[1]

или комплекта из нескольких

специализированных микросхем[2]

(в отличие от реализации процессора в

виде электрической схемы на элементной

базе общего назначения или в виде

программной модели).

В

состав МП (рис. 1) входят арифметическо-логическое

устройство, устройство управление и

блок внутренних регистров.Арифметическо-логическое

устройство

состоит из двоичного сумматора со

схемами ускоренного переноса, сдвигающего

регистры и регистров для временного

хранения операндов. Обычно это устройство

выполняет по командам несколько

простейших операций: сложение, вычитание,

сдвиг, пересылку, логическое сложение

(ИЛИ), логическое умножение (И), сложение

по модулю 2. Устройство

управления

управляет работой АЛУ и внутренних

регистров в процессе выполнения команды.

Согласно коду операций, содержащемуся

в команде, оно формирует внутренние

сигналы управления блоками МП. Адресная

часть команды совместно с сигналами

управления используется для считывания

данных из определенной ячейке памяти

или для записи данных в ячейку. По

сигналам УУ осуществляется выборка

каждой новой, очередной команды.

Блок

внутренних регистров

БВР, расширяющий возможности АЛУ, служит

внутренней памятью МП и используется

для временного хранения данных и команд.

Он также выполняет некоторые процедуры

обработки информации.блок

внутренних регистров содержит регистры

общего назначения и специальные регистры:

регистр-аккумулятор, буферный регистр

адреса, буферный регистр данных, счетчик

команд, стека, признаков. Регистры

общего назначения (РОН),

число которых может изменятся от 4 до

64, определяют вычислительные возможности

МП. Их функция – хранение операндов. Но

могут выполнять также и роль регистров.

Все РОН доступны программисту, который

рассматривает их как сверхоперативное

запоминающее устройство. Регистр

– аккумулятор

(“накопитель”), предназначен для

временного хранения операнда или

промежуточного результата действий

производимой в АЛУ. Разрядность регистра

равна разрядности информационного

слова. Буферный

регистр адреса

служит для приема и хранения адресной

части выполняемой команды. Возможное

количество адресов, определяется

разрядностью регистра. Буферный

регистр данных

используется для временного хранения

выбранного из памяти слова перед

передачей его во внешнюю шину данных.

Его разрядность определяется количеством

байт информационного слова.

Счетчик команд

содержит адрес ячейки памяти, в которой

помещены байты выполняемой команды.

Регистр

команд

принимает и хранит код очередной команды,

адрес которой находится в счетчике

команд. По сигналу УУ в него передается

из регистра хранимая там информация.

Регистры

стека делятся

на стек и указатель стека. В МП стек –

набор регистров, хранящих адреса команд

возврата при обращении к подпрограммам

или состояние внутренних регистров при

обработке прерываний. Стек может быть

выполнен не только на внутренних

регистрах МП, составляя его часть, но и

находиться в ОЗУ, занимая там отведенную

для него зону. В последнем случае для

обращения к нему необходим специальный

регистр – указатель стека. Указатель

стека хранит

адреса последней занятой ячейки стека,

которую называют вершиной. Содержащее

в указателе число указывает, где находится

вершина стека. Когда в стек записывается

очередное слово, то число в указателе

стека соответственно увеличивается.

Извлечение слова из стека сопровождается,

наоборот, уменьшением числа, заполняющего

указатель стека. Кроме такой процедуры

предусматривается возможность считывания

без разрушений содержимого любой ячейки

стека при неизменном числе, хранимом в

указателе стека.

В

состав МП (рис. 1) входят арифметическо-логическое

устройство, устройство управление и

блок внутренних регистров.Арифметическо-логическое

устройство

состоит из двоичного сумматора со

схемами ускоренного переноса, сдвигающего

регистры и регистров для временного

хранения операндов. Обычно это устройство

выполняет по командам несколько

простейших операций: сложение, вычитание,

сдвиг, пересылку, логическое сложение

(ИЛИ), логическое умножение (И), сложение

по модулю 2. Устройство

управления

управляет работой АЛУ и внутренних

регистров в процессе выполнения команды.

Согласно коду операций, содержащемуся

в команде, оно формирует внутренние

сигналы управления блоками МП. Адресная

часть команды совместно с сигналами

управления используется для считывания

данных из определенной ячейке памяти

или для записи данных в ячейку. По

сигналам УУ осуществляется выборка

каждой новой, очередной команды.

Блок

внутренних регистров

БВР, расширяющий возможности АЛУ, служит

внутренней памятью МП и используется

для временного хранения данных и команд.

Он также выполняет некоторые процедуры

обработки информации.блок

внутренних регистров содержит регистры

общего назначения и специальные регистры:

регистр-аккумулятор, буферный регистр

адреса, буферный регистр данных, счетчик

команд, стека, признаков. Регистры

общего назначения (РОН),

число которых может изменятся от 4 до

64, определяют вычислительные возможности

МП. Их функция – хранение операндов. Но

могут выполнять также и роль регистров.

Все РОН доступны программисту, который

рассматривает их как сверхоперативное

запоминающее устройство. Регистр

– аккумулятор

(“накопитель”), предназначен для

временного хранения операнда или

промежуточного результата действий

производимой в АЛУ. Разрядность регистра

равна разрядности информационного

слова. Буферный

регистр адреса

служит для приема и хранения адресной

части выполняемой команды. Возможное

количество адресов, определяется

разрядностью регистра. Буферный

регистр данных

используется для временного хранения

выбранного из памяти слова перед

передачей его во внешнюю шину данных.

Его разрядность определяется количеством

байт информационного слова.

Счетчик команд

содержит адрес ячейки памяти, в которой

помещены байты выполняемой команды.

Регистр

команд

принимает и хранит код очередной команды,

адрес которой находится в счетчике

команд. По сигналу УУ в него передается

из регистра хранимая там информация.

Регистры

стека делятся

на стек и указатель стека. В МП стек –

набор регистров, хранящих адреса команд

возврата при обращении к подпрограммам

или состояние внутренних регистров при

обработке прерываний. Стек может быть

выполнен не только на внутренних

регистрах МП, составляя его часть, но и

находиться в ОЗУ, занимая там отведенную

для него зону. В последнем случае для

обращения к нему необходим специальный

регистр – указатель стека. Указатель

стека хранит

адреса последней занятой ячейки стека,

которую называют вершиной. Содержащее

в указателе число указывает, где находится

вершина стека. Когда в стек записывается

очередное слово, то число в указателе

стека соответственно увеличивается.

Извлечение слова из стека сопровождается,

наоборот, уменьшением числа, заполняющего

указатель стека. Кроме такой процедуры

предусматривается возможность считывания

без разрушений содержимого любой ячейки

стека при неизменном числе, хранимом в

указателе стека.

Регистр признаков представляет собой набор триггеров – флажков. В зависимости от результатов операций, выполняемых АЛУ, каждый триггер устанавливается в состояние 0 или 1. Флажковые биты, определяющие содержимое регистра, индицируют условные признаки: нулевого результата, знака результата, перевыполнения и т. п. Эта информация, характеризующая состояние процессора, важна для выбора дальнейшего пути вычислений.