УП часть 2 ТА

.pdf

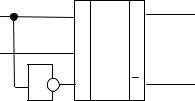

Одним из способов устранения недостатка RSтриггеров – наличие запрещенных кодовых комбинаций входных сигналов - является построение еще одной разновидности триггерных схем, которая получила название D-триггер. Для управления синхронным однотактным RS-триггером необходимо три входных сигнала (два - информационных; один - управляющий). D-триггеры имеют один информационный D-вход и один управляющий вход – С. В D- триггерах запрещенные комбинации исключаются путем соединения через инвертор S и R входов синхронного RS-триггера так, как показано на рис.6.13 а.

D

S T Q

C

С

1

R Q

Рис. 6.13 (а) Схема D-триггера с включением инвертора между информационными входами синхронного RS-триггера.

При этом на информационные входы RS-триггера никогда не поступают одинаковые сигналы, то есть исключаются не только заперещенные кодовые комбинации (S=R=1), но и режим хранения (S=R=0), который реализуется путем подачи на вход C нулевого уровня сигнала [4].

Значение сигнала на выходе Q D-триггера в момент времени (t+1) равно значению сигнала на входе D в предыдущий момент времени t. Таким образом, входной сигнал передается на выход с

задержкой на один такт, то есть Qt+1 = Dt . Поэтому D-триггер

называют триггером задержки.

Асинхронный D-триггер не применяется, так как его выход просто повторяет входной сигнал после окончания режима состязаний.

Синхронный D-триггер функционирует в соответствии с таблицей 6.6.

Таблица 6.6

C |

D |

Q |

Q+ |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

Как видно из этой таблицы, D-триггер способен запоминать по синхросигналу и хранить один бит информации. При отсутствии сигнала синхронизации (С=0) состояние триггера остается неизменным.

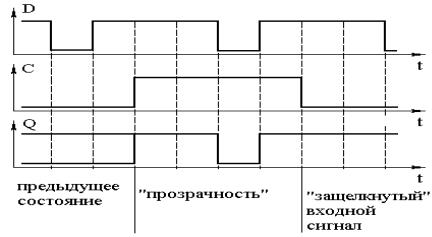

Во всех рассмотренных ранее схемах синхронных триггеров синхросигнал работает по уровню, поэтому триггеры называются триггерами, работающими по уровню. Ещё одно название таких триггеров, пришедшее из иностранной литературы - триггерызащёлки. Легче всего объяснить появление этого названия по временной диаграмме, приведенной на рис.6.13 (б) [10].

Рис. 6.13 (б). Временная диаграмма D-триггера (защелки)

По этой временной диаграмме видно, что триггер-защелка хранит данные на выходе только при нулевом уровне на входе синхронизации. Если на входе С синхронного D-триггера постоянно будет присутствовать логическая единица, то принято говорить, что D-триггер становится прозрачным. Этим хотят подчеркнуть то обстоятельство, что сигнал на выходе Q будет повторять значение сигнала на входе D.

Входное напряжение запоминается только в момент изменения уровня напряжения на входе синхронизации C с высокого уровня на низкий уровень. Входные данные как бы "защелкиваются" в этот момент, отсюда и название – триггерзащелка.

Принципиально в этой схеме входной переходной процесс может беспрепятственно проходить на выход триггера. Поэтому там, где это важно, необходимо сокращать длительность импульса синхронизации до минимума. Чтобы преодолеть такое ограничение были разработаны триггеры, работающие по фронту.

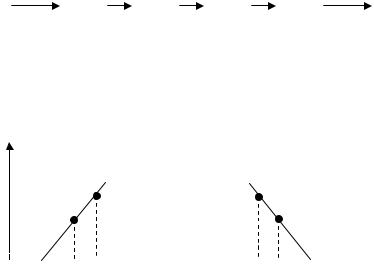

Для синтеза синхронного D-триггера воспользуемся асинхронным RS-триггером, который управляется низким потенциалом сигналов. Как видно из табл. 6.6, сигнал на входе D должен воздействовать на триггер только в том случае, когда имеется единичный уровень сигнала С. Следовательно, как и в случае синхронного RS-триггера, на входе D-триггера должны быть двухвходовые элементы И-НЕ, пропускающие сигнал с входа D при С=1.

Рассмотрим правую часть таблицы 6.6. Переход триггера в состояние единицы должен происходить, когда на входах воздействуют сигналы С=1 и D=1. Значит, при таком сочетании

сигналов на входе S асинхронного RS-триггера должен быть нуль,

то есть S = C * D . Переход триггера в состояние нуля должен происходить, когда на входах имеется комбинация C=1, D=0.

Значит, на входе R асинхронного RS-триггера при таком сочетании

сигналов также должен быть нуль, то есть R = C * D .

Следовательно, D-триггер может быть синтезирован на основе асинхронного RS-триггера [6], так как показано на рис. 6.13 (в).

Уравнение однотактного асинхронного RS-триггера в элементном базисе И-НЕ имеет вид:

Q+ = S * R *Q

Если в этом уравнении произвести соответствующие нашим

рассуждениям замены переменных, то есть |

S |

= |

C * D |

, |

R |

= C * |

D |

, |

|||||||||||||||||||

то получим уравнение для однотактного синхронного D-триггера |

|||||||||||||||||||||||||||

(6.7). |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q+ |

= |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

*C * |

|

|

*Q |

|

|

|

|

|

|

|

|

|

|

|

|

(6.7) |

||||||||||

C * D |

D |

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

S |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D |

|

|

|

|

|

|

& |

|

|

|

|

|

|

& |

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

C |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

&

& &

& &

R

Рис. 6.13 (в) Синтезированный на основе RS-триггера однотактный

синхронный D-триггер.

На рис. 6.14 представлено УГО однотактного синхронного D- триггера.

D T Q

C Q

Рис. 6.14. УГО однотактного синхронного D-триггера

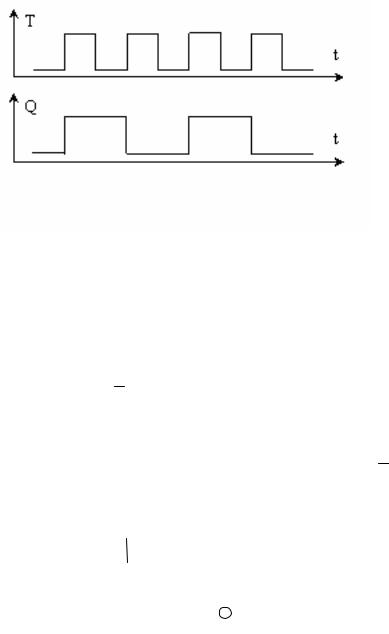

6.6. Однотактный Т-триггер

Т-триггер – это счетный триггер. У Т-триггера имеется только один вход. После поступления на этот вход импульса, состояние Т- триггера меняется на прямо противоположное. Счётным он

называется потому, что он как бы подсчитывает количество импульсов, поступивших на его вход. Жаль только, что считать этот триггер умеет только до одного. При поступлении второго импульса T-триггер снова сбрасывается в исходное состояние.

Булеву функцию, отражающую работу Т-триггера, содержательно можно представить так: триггер инвертирует свое предыдущее состояние при подаче на его вход Т единичного

|

|

Qt+1 |

|

|

|

|

|

|

сигнала, то есть |

= Qt |

при Т=1. Соответствующая таблица |

||||||

переключений Т-триггера представлена в табл. 6.7 |

||||||||

|

|

|

|

|

|

|

|

Таблица 6.7 |

|

|

|

|

|

|

|

|

|

|

T |

Q |

|

|

Q+ |

|

}режим хранения |

|

|

0 |

0 |

|

0 |

|

|

||

|

0 |

1 |

|

1 |

|

|

||

|

1 |

0 |

|

1 |

|

|

}режим счета |

|

|

1 |

1 |

|

0 |

|

|

||

Вход Т называют счетным входом триггера. При подаче на триггер первого единичного сигнала он устанавливается в единицу, при подаче второго – сбрасывается в нуль, третьего – опять в единицу и т.д. Таким образом, изменение выходного сигнала происходит с частотой, вдвое меньшей, чем входного (рис. 6.18 а). Это позволяет использовать Т-триггер для синтеза двоичных счетчиков, в которых каждый триггер соответствует одному двоичному разряду.

Рис. 6.18 а. Временная диаграмма работы Т-триггера

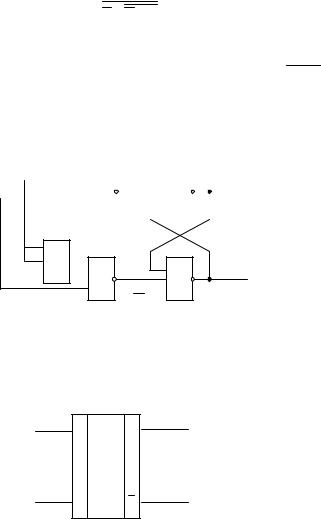

Т-триггер может быть синтезирован на логических элементах И-НЕ или ИЛИ-НЕ, однако чаще всего для синтеза однотактного Т- триггера используют имеющийся в составе серий интегральных микросхем D-триггер. Превращение D-триггера в Т-триггер осуществляется с помощью соответствующего соединения выводов микросхемы.

Так, если в синхронном D-триггере вход D соединить с

инверсным выходом Q , то он превращается в Т-триггер.

Действительно, если посмотреть в табл. 6.6 строки, в которых состояние триггера Q меняется на противоположное (строки 6 и 7 в правой части таблицы), увидим, что значение сигнала на входе D

противоположно значению Q. Поскольку сигнал на выходе Q

всегда противоположен состоянию Q, то подавая счетные сигналы Т вместо синхроимпульсов на вход С (рис. 6.18 б), из D-триггера получим Т-триггер [6].

|

|

|

|

|

|

|

|

|

|

D |

T |

Q |

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|||

|

|

|

|

_ |

|

|

|

Т |

|

C |

|

Q |

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

Рис. 6.18 б Синтез однотактного Т-триггера на основе D-триггера

Данная схема будет работоспособной только при определенном условии, что длительность сигнала Т будет надежно меньше времени переключения триггера. Для однотактных триггеров это условие на практике обеспечить сложно.

6.7. Принцип построения двухтактного триггера

Рассмотренные разновидности одноактных триггерных схем усложняют реализацию так называемого режима счета (деления входной тактовой частотой). Но именно данный режим работы триггерных схем является очень важным при построении различных вычислительных устройств. Именно данной обстоятельство потребовало построения двухтактных триггерных схем.

Рассмотрим два сигнала на временной диаграмме.

a |

|

|

|

|

|

|

|

а= |

|

|

|

|

|

|

|

|

|

|

t |

в |

|||||

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

в=а |

|

|||

в

t

t

Рис. 6.15 Временная диаграмма сигналов a и B.

Данные сигналы можно трактовать как различные сигналы, а можно понимать как один и тот же безинверсный и инверсный сигнал.

Данная особенность положена в основу работы двухтактных триггерных схем.

В [5] рассмотрен принцип построения двухтактного триггера, который называют также триггером типа MS (от англ. master, slave, что переводят обычно как «ведущий», «ведомый»). Его упрощенная структурная схема приведена на рис. 6.16. В схеме имеются два одноступенчатых триггера (ведущий M, ведомый S) и два электронных ключа (Кл1 и Кл2).

Входные |

|

|

|

|

|

|

|

|

информа- |

|

|

|

|

|

|

Выходные |

|

ционные |

|

|

|

|

|

|

||

сигналы |

|

|

|

|

|

|

|

сигналы |

Кл1 |

|

М |

|

Кл2 |

S |

|||

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

Рис. 6.16 Структурная схема двухтактного триггера.

Временная диаграмма сигнала синхронизации, поясняющая работу триггера, приведена на рис. 6.17

С

b |

|

с |

a |

|

d |

|

0 t

t

ta |

tb |

tc |

td |

Рис. 6.17 Временная диаграмма сигнала синхронизации Рассмотрим ряд временных интервалов указанной диаграммы:

t < ta - ведущий триггер отключен от информационных входов, ведомый триггер подключен к ведущему;

ta ≤ t ≤ tb - ведущий триггер отключен от информационных входов, ведомый триггер отключен от ведущего;

tb < t < tc - ведущий триггер подключен к информа-ционным

входам, ведомый триггер отключен от ведущего. В ведущий триггер записывается информация;

tc ≤ t ≤ td - ведущий триггер отключен от информационных входов, ведомый триггер отключен от ведущего;

td < t - ведущий триггер отключен от информационных входов,

ведомый триггер подключен к ведущему; информация из ведущего триггера переписывается в ведомый. Это происходит сразу после

момента времени td и означает, что фактически двухступенчатый триггер срабатывает при изменении сигнала синхронизации от 1 к 0. При этом выходные сигналы определяются теми входными информационными сигналами, которые имели место непосредственно перед отрицательным фронтом сигнала синхронизации.

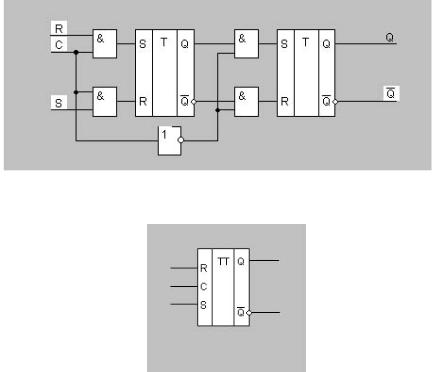

6.7.1 Двухтактные RS-триггеры

На рис.6.19 (а) приведен вариант схемы, наиболее доступный для понимания, принципа работы двухтактного синхронного RSтриггера, на рис.6.19 (б) представлено его графическое обозначение.

Рис. 6.19 (а) Синхронный двухтактный RS-триггер

Рис. 6.19 (б) УГО синхронного двухтактного RS-триггера

В схеме на рис. 6. 19 (а) использованы два синхронных RSтриггера и инвертор.

При С=1 производится запись информации в первый триггер, при этом второй триггер заблокирован и находится в режиме хранения, так как на его С-вход через инвертор подается нулевой сигнал.

При С=0 блокируется первый триггер, на вход С второго триггера поступает единичный сигнал и информация с выхода первого триггера переписывается на выход второго.

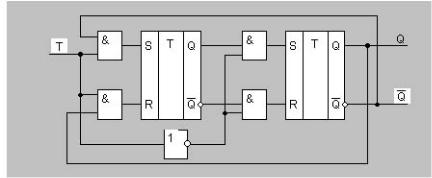

6.7.2 Двухтактные T-триггеры

Т-триггеры строятся только на базе двухступенчатых триггеров. Использование двух триггеров позволяет избежать самовозбуждения схемы, так как счетные триггеры строятся при помощи схем с обратной связью

Т-триггер можно синтезировать из любого двухступенчатого триггера. Основой для построения двухтактных Т-триггеров могут служить двухтактные синхронные RS-триггеры, в которых для изменения состояния триггера на инверсное используются собственные входные сигналы.

Рис. 6.19 Синтез двухтактных асинхронных Т-триггеров на основе двухтактных синхронных RS-триггеров

На рис. 6.20 представлено УГО двухтактного асинхронного Т- триггера.