УП часть 2 ТА

.pdfПервая советская полупроводниковая микросхема была создана в 1961 году в Таганрогском радиотехническом институте, в лаборатории Л. Н. Колесова.[ http://ru.wikipedia.org/wiki/Интегральная_схема]

Усложнение цифровых электронных устройств привело к резкому росту числа корпусов интегральных схем малой и средней степени интеграции. В результате увеличилась потребляемая мощность и габаритные размеры устройства, снизилось быстродействие и надежность, усложнился монтаж устройства. В то же время даже небольшая модификация устройства стала требовать значительных усилий от разработчика, поскольку зачастую приходилось разрабатывать практически новые устройства [5].

Построение цифровых электронных устройств на специализированных больших и сверхбольших интегральных схемах (БИС и СБИС) позволило не только улучшить технические характеристики устройств, но и расширить их функциональные возможности. Однако это оказалось экономически целесообразно лишь при больших объемах выпускаемых устройств, поскольку разработка и изготовление заказных специализированных БИС и СБИС — это длительный и дорогостоящий процесс.

Современная схемотехническая база цифровых комбинационных автоматов.

Сложность цифровых интегральных микросхем принято оценивать количеством логических элементов, размещенных на одном кристалле. С этой точки зрения цифровые интегральные микросхемы подразделяются на следующие типы:

1.МИС – малые интегральные схемы (до 100 логических элементов в кристалле).

2.СИС – средние интегральные схемы (до 1000 логических элементов в кристалле).

3.БИС – большие интегральные схемы (до 10000 логических элементов в кристалле).

4.СБИС – сверхбольшие интегральные схемы (до 1 миллиона логических элементов в кристалле).

5.УБИС – ультрабольшие интегральные схемы (до 1 миллиарда логических элементов в кристалле).

6. ГБИС – гигабольшая интегральная схема— более 1 миллиарда элементов в кристалле.

Устранить возникшие противоречия удалось созданием универсальных логических устройств большой степени интеграции, алгоритмы работы которых задаются разработчиком. Такие устройства получили название программируемых логических интегральных схем (ПЛИС). Программируя ПЛИС, получают требуемые изменения структуры, что и обеспечивает реализацию необходимых функций. Очевидно, что универсальность, присущая ПЛИС, достигается избыточностью их аппаратной части, что, конечно, сказывается на быстродействии, которое ниже, чем при использовании специализированных БИС и СБИС, но значительно выше, чем при применении интегральных схем малой и средней степени интеграции.

Однако преимущества ПЛИС и прежде всего многофункциональность способствуют их широкому распространению.

Для понимания принципа, положенного в основу ПЛИС, рассмотрим, в какой структуре можно реализовать систему логических уравнений, заданных в совершенной дизъюнктивной нормальной форме (СДНФ) (3.1).

F1 = xn × xn−1 Lx2 × x1 + xn × xn−1 Lx2 × x1 +K+ xn × xn−1 Lx2 × x1;

K |

(3.1) |

Fm = xn × xn−1 Lx2 × x1 + xn × xn−1 ××x2 × x1 +K+ xn × xn−1 Lx2 × x1;

Число конъюнкций (произведений) в каждой функции не может превышать 2n (n — число аргументов функции).

Очевидно, чтобы реализовать такую систему логических функций, необходимо два блока, в одном из которых осуществляется формирование конъюнкций (произведений входных переменных), а в другом — их логическое сложение (т. е. дизъюнкция). Следовательно, укрупненная структура ПЛИС выглядит следующим образом (рис. 3.1).

x1 |

Вх |

|

Матрица |

|

Матрица |

|

Вх |

F |

|

|

|

И |

|

ИЛИ |

|

|

1 |

... |

|

... |

... |

... |

|

... |

||

|

|

|

|

|||||

xn |

|

|

|

|

|

|

|

F |

|

|

|

|

|

|

|

|

m |

Рис.3.1 Структура ПЛИС

Входные (Вх) и выходные (Вых) буферные каскады осуществляют необходимые (иногда довольно сложные) преобразования входных и выходных сигналов. Например, формируют прямые и инверсные входные сигналы, формируют сигналы необходимой мощности, обеспечивают необходимую нагрузочную способность выходов и т. п. Входные переменные (прямые и инверсные) поступают на матрицу И и на ее выходах формируются необходимые произведения этих переменных, которые затем складываются в матрице ИЛИ, обеспечивая реализацию требуемых логических функций.

Одним из классов программируемых логических интегральных схем являются программируемые логические матрицы (ПЛМ).

3.1 Программируемые логические матрицы

Создание двухуровневых программируемых пользователем логических матриц (ППЛМ) было ответом производителей цифровых интегральных микросхем на сложившуюся в конце 60-х годов прошлого века парадоксальную ситуацию: разновидностей логических микросхем требовалось все больше и больше, а объемы производства каждой разновидности постоянно снижались. В такой ситуации был найден, возможно, единственно правильный выход, который заключался в разработке и массовом выпуске достаточно универсальных интегральных микросхем, которые могли

использоваться |

и в единичных экземплярах, но миллионами |

|||

индивидуальных |

пользователей. |

Именно |

таким |

образом |

обеспечивался компромисс между большими затратами на организацию массового производства некоторого типа интегральных микросхем и быструю окупаемость этих затрат.

Такими интегральными микросхемами и стали, так называемые ныне, двухуровневые программируемые пользователем

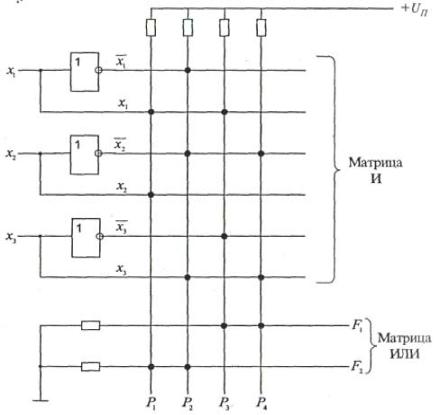

логические матрицы. Эти интегральные микросхемы позволяют (при наличии у пользователя специальных программаторов) оперативно реализовывать достаточно сложные многовыходные логические преобразователи (ЛП), закон функционирования которых изначально представляется в естественной для человека форме. Строгое математическое выражение этой естественной формы в научно-технической литературе принято называть совершенной дизъюнктивной нормальной формой (СДНФ) или ее минимизированным эквивалентом – дизъюнктивной нормальной формой (ДНФ). Универсализм двухуровневых ППЛМ обеспечивается введением на этапе их серийного производства значительной структурной избыточности как электронных элементов ППЛМ, так и электрических связей между этими элементами. При этом в архитектуру ППЛМ вводятся дополнительные электронные узлы, обеспечивающие по командам извне разрушение в определенных местах ненужных электрических связей между избыточными элементами, образующими собственно ППЛМ. Схема электрическая функциональная незапрограммированной ППЛМ показана на рис. 3.2.

Рис. 3.2 Схема электрическая функциональная незапрограммированной ППЛМ (без дополнительных электронных узлов)

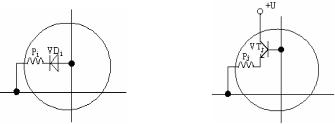

Как видно из рис.3.2 двухуровневая ППЛМ состоит из блока инверторов (DD1...DDS), на входы которых подаются входные логические переменные (X1...XS), и двух матриц. В матрице И на шинах Z1...Zq формируются элементарные конъюнкции с любым набором прямых и инверсных значений логических переменных X1...XS, а в матрице ИЛИ реализуются элементарные дизъюнкции с элементарными конъюнкциями, сформированными на шинах Z1...Zq. Результат операций дизъюнкции формируется на выходных шинах Y1...Yt. Матрицы И и ИЛИ представляют собой систему ортогональных проводников, в узлах пересечения которых располагаются полупроводниковые элементы, реализующие с резисторами нагрузки операции И и ИЛИ. Операцию И реализуют при помощи диодов, а операцию ИЛИ – при помощи триодов. Электрическое подключение диодов и триодов к соответствующим ортогональным проводникам осуществляется через специальные перемычки Pi (Pj), некоторые из которых при программировании ППЛМ удаляются (пережигаются) в соответствующих узлах.

На рис. 3.3 показано подключение диодов в узлах матрицы И, а на рис. 3.4 – подключение триодов в узлах матрицы ИЛИ.

Рис. 3.3 Подключение |

Рис. 3.4 |

Подключение |

|

триодов в |

узлах матрицы |

||

диодов в узлах матрицы И |

|||

ИЛИ |

|

||

|

|

Логические уравнения для выходных сигналов Y1...Yt, формируемых незапрограммированными ППЛМ, имеют один и тот же вид в СДНФ:

q |

s |

|

||

Y r = (X ji |

|

ji), |

(3.2) |

|

X |

||||

j = |

1i =1 |

|

||

|

|

|

|

где |

r =1,t ; |

||

|

- операция логического сложения (дизъюнкции); |

||

- операция логического умножения (конъюнкции).

В[5] рассмотрен пример, как с учетом рис. 3.3, 3.4 , можно

определить, какие логические функции F1, F2 будут реализованы на ПЛМ, имеющей показанные на рис. 3.5 соединения.

Рис. 3.5 Программируемая логическая матрица

Только при наличии и на входе х1 и на входе х2 сигналов высокого уровня (соответствующих логической единице), на выходе первого столбца Р1, имеется сигнал высокого уровня. Таким образом, по отношению к выходу первого столбца реализуется функция

И, т. е P1 = x1 * x2 .. Для второго столбца высокое напряжение на выходе (логическая 1) будет лишь тогда, когда высокий уровень напряжения будет на шинах x1 , x2 , x3 , т. е. P2 = x1 × x2 × x3 .

Аналогично получим P3 = x1 × x3 , P4 = x2 × x3 .

Высокий уровень напряжения (логическая 1) на шине F1 матрицы ИЛИ будет лишь тогда, когда высокий уровень напряжения (логическая 1) действует или на третьем, или на четвертом столбцах, т. е. по отношению к выходной шине F1 выполняется функция ИЛИ:

F1 = P3 + P4 = x1 × x3 + x2 × x3 ,

По аналогии получим

F2 = P1 + P2 = x1 × x2 + x1 × x2 × x3

Таким образом, программируемая логическая матрица — это сетка взаимно перпендикулярных проводников (рис. 3.2), в местах пересечения которых находятся полупроводниковые элементы — диоды или транзисторы, включенные через легкоплавкие перемычки к проводникам матрицы. Программирование ПЛМ заключается в пережигании перемычек, соединяющих горизонтальные и вертикальные шины матриц, которое выполняется на специальных устройствах — программаторах. В исходном состоянии все перемычки целы. Если в переменную Р входит прямое значение аргумента х, то пережигается перемычка, соединяющая вертикальную шину Р с инверсной горизонтальной шиной, если значение аргумента инверсное — то с шиной, передающей прямое значение аргумента. Если аргумент не участвует в формировании переменной, пережигаются обе перемычки. Если переменная Р входит в функцию у, то перемычка сохраняется, в противном случае

— пережигается [6].

4 КОНЕЧНЫЕ ФУНКЦИОНАЛЬНЫЕ ПРЕОБРАЗОВАТЕЛИ

В [7] изложен систематический подход к построению комбинационных схем — простейших преобразователей информации, реализующих функциональное отображение конечных множеств.

Рассмотрим проблемы построения простейших дискретных преобразователей информации.

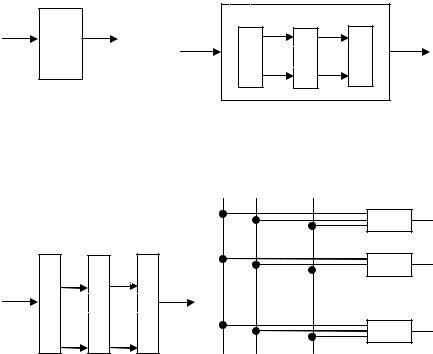

Пусть А — некоторое множество элементов информации, представленных тем или иным образом, В — другое множество элементов информации, а Ф — функция преобразования. Преобразователь информации можно представить себе схематично как устройство, реализующее отображение Ф : А → В одного множества на другое (рис. 4.1, а). Рассмотрим возможность систематического построения таких преобразователей. Очевидно, что трудно предложить какое-то решение в общем случае, когда множества А и В имеют произвольную природу, а о самом отображении Ф ничего не известно. Однако, если множества А и В являются конечными (то есть преобразователь, который мы хотим построить, является «конечным функциональным преобразователем») и дискретными (то есть преобразование осуществляется в дискретные моменты времени), существует систематический метод решения этой проблемы. Этот метод состоит в том, что элементы множеств А и В предварительно кодируют двоичными кодами и строят преобразование одного множества двоичных векторов в другое (рис. 4.1,б). Рассмотрим этот метод на примере.

Двоичное кодирование состоит во взаимно однозначном сопоставлении всем элементам конечного множества некоторых двоичных векторов одной и той же длины. При таком подходе проблема реализации преобразователя Ф сводится к построению трех преобразователей: кодировщика К : А → Х , собственно функционального преобразователя F : X → Y и декодировщика D : Y → B , причем эти отображения должны быть выбраны так, что К ∙ F ∙ D = Ф (рис. 4.1, б). Рассмотрим проблемы построения этих трех преобразователей поочередно.

A |

В |

Ф |

|

Y |

|

A |

|

В |

|||

|

Ф |

|

|

||

|

К |

… |

F … |

D |

|

|

|

||||

|

а ) |

|

|

б) |

|

|

X |

A |

x1 |

|

|

К |

… |

|

xm |

|

в) |

|

x1 |

x2 |

xm |

|

|

|

f1 |

Y |

|

|

f2 |

f1 |

В |

|

|

|

|

||

… D |

|

… |

… |

fn |

|

|

fn |

г)

Рис. 4.1 Реализация конечного функционального преобразователя

Число двоичных векторов длины n равно 2", и если все элементы множества S закодировать двоичными векторами одной и той же длины n, то для однозначности кодирования n должно быть не меньше, чем log2|S|. Пусть m и n — длины двоичных векторов для кодирования соответственно множеств А и В входных и выходных информационных элементов конечного функционального преобразователя Ф. Тогда кодирование — это построение

некоторого |

отображения |

К : А → {0,1}n |

декодирование — |

построение |

отображения |

D : {0,1}n → B , |

а функциональное |

отображение F сопоставляет каждому вектору из {0,1}m некоторый вектор из {0,1}n, причем так, чтобы К ∙ F ∙ D = Ф .

Пример 4.1

Пусть множество А = {а1,а2,аЗ,а4,а5}, а множество В = {b1,b2,bЗ} и отображение Ф задается табл. 4.1.

Таблица 4.1. Отображение Ф : А → В

A |

B |

a1 |

b2 |

a2 |

b3 |

a3 |

b2 |

a4 |

b1 |

a5 |

b2 |

Понятно, что в данном примере m должно быть не меньше 3, n должно быть не меньше 2. Мы можем выбрать произвольно функции кодирования и декодирования (например, представленные на рис. 1.2 в виде таблиц I и II). Отображение F строим таким образом, чтобы соотношение выполнялось К ∙ F ∙ D = Ф .

|

I |

|

II |

|

|

|

III |

|

|

|

IV |

|||

К : А → {0,1}3 |

|

F : {0,1}3 |

→ {0,1}2 |

D : {0,1}2 |

→ B |

Ф : А → В |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A |

{0,1}3 |

|

{0,1}3 |

|

{0,1}2 |

{0,1}2 |

|

B |

A |

|

B |

|||

a1 |

010 |

|

000 |

|

-- |

|

|

00 |

|

b1 |

= |

a1 |

|

b2 |

a2 |

110 |

∙ |

001 |

|

10 |

|

∙ |

01 |

|

-- |

a2 |

|

b3 |

|

a3 |

001 |

|

010 |

|

10 |

|

|

10 |

|

b2 |

|

a3 |

|

b2 |

a4 |

100 |

|

011 |

|

10 |

|

|

11 |

|

b3 |

|

a4 |

|

b1 |

a5 |

011 |

|

100 |

|

00 |

|

|

|

|

|

|

a5 |

|

b2 |

|

|

|

101 |

|

-- |

|

|

|

|

|

|

|

|

|

|

|

|

110 |

|

11 |

|

|

|

|

|

|

|

|

|

|

|

|

111 |

|

-- |

|

|

|

|

|

|

|

|

|

|

|

|

Рис. 4.2 |

Отображение F |

|

|

|

|

|

|||||