- •Экзаменационный билет № 1

- •Экзаменационный билет № 2

- •Экзаменационный билет № 3

- •Экзаменационный билет № 4

- •Экзаменационный билет № 5

- •Экзаменационный билет № 6

- •Экзаменационный билет № 7

- •Экзаменационный билет № 8

- •Экзаменационный билет № 9

- •Экзаменационный билет № 10

- •Экзаменационный билет № 11

- •Экзаменационный билет № 12

- •Экзаменационный билет № 13

- •Экзаменационный билет № 14

- •Экзаменационный билет № 15

- •Экзаменационный билет № 16

- •Экзаменационный билет № 17

- •Экзаменационный билет № 18

- •Экзаменационный билет № 19

- •Экзаменационный билет № 20

Экзаменационный билет № 9

Оперативное запоминающее устройство (ОЗУ), постоянное запоминающее устройство (ПЗУ). Статические запоминающие устройства. Динамические запоминающие устройства.

Основная

память предназначена для хранения

и оперативного обмена информацией с

прочими блоками машины. ОП содержит

два вида запоминающих устройств:

постоянное запоминающее устройство

(ПЗУ) и оперативное запоминающее

устройство (ОЗУ).

ПЗУ

служит для хранения неизменяемой

(постоянной) программной и справочной

информации, позволяет оперативно

только считывать хранящуюся в нем

информацию (изменить информацию в ПЗУ

нельзя).

ОЗУ предназначено для оперативной записи, хранения и считывания информации (программ и данных), непосредственно участвующей в информационно-вычислительном процессе, выполняемом ПК в текущий период времени. Главными достоинствами оперативной памяти являются ее высокое быстродействие и возможность обращения к каждой ячейке памяти отдельно (прямой адресный доступ к ячейке), В качестве недостатка ОЗУ следует отметить невозможность сохранения информации в ней после выключения питания машины (энергозависимость).

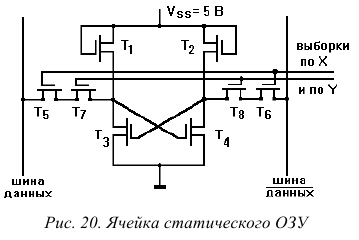

Статическая операционная память с произвольным доступом – полупроводниковая операционная память, в которой каждый 2-й разряд хранится в системе с полной обратной связью, позволяющей поддерживать состояние сигнала без постоянной перезаписи.

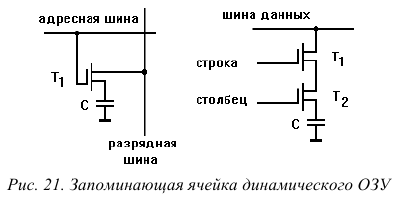

Динамическая память – получила название от принципа действия ее запоминающих ячеек, которые выполнены в виде конденсаторов. Из-за присутствия токов утечки, конденсаторы разряжаются и информация теряется, поэтому необходимо периодическая подзарядка.

Механизмы реализации условных переходов в машинной программе.

Условный переход — команда программируемому вычислительному устройствуна изменение порядка выполненияпрограммыв соответствии с результатом проверки некоторого условия.

Наиболее часто условный переход имеет две стадии: на первой происходит сравнение между собой некоторых величин, определяющих условие перехода, на второй выполняется сам переход. Необходимость корректной обработки условных переходов накладывает серьёзный отпечаток на логику работы современных конвейерных процессоров. Условные переходы могут выполняться двумя способами. Выполняемые условные переходы меняют значениесчётчика командпроцессорана вычисленное значение адреса перехода. Невыполняемые — прибавляют к значению счётчика команд число, равное длине текущей команды в байтах, для перехода к выполнению следующей команды. Неправильное определение типа условного перехода может приводить к возникновению существенных задержек в работеконвейераи соответственно к большой потери производительностикомпьютера.

Экзаменационный билет № 10

Прерывание, обработчик прерывание, работа микропроцессора.

Задачей аппаратных средств обработки прерывания в процессоре микроЭВМ как раз и является приостановка выполнения одной программы (ее еще называют основной программой) и передача управления подпрограмме обработки прерывания.

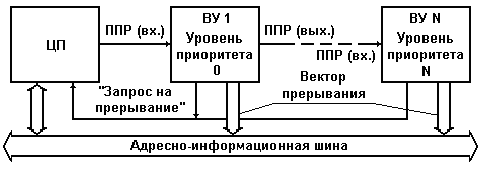

Процессор при поступлении в него по общей линии системного интерфейса "Запрос на прерывание" сигнала прерывания формирует управляющий сигнал "Предоставление прерывания (вх.)", который поступает сначала в контроллер ВУ с наивысшим приоритетом (рис. 41).

Если это устройство не требовало обслуживания, то его контроллер пропускает сигнал "Предоставление прерывания" на следующий контроллер, иначе дальнейшее распространение сигнала прекращается и контроллер выдает вектор прерывания на адресно – информационную шину.

Аппаратный опрос готовности ВУ производится гораздо быстрее, нежели программный. Но если обслуживания запросили одновременно два или более ВУ, обслуживание менее приоритетных ВУ будет отложено на время обслуживания более приоритетных, как и в системе прерывания с программным опросом.

Последовательность работы микропроцессора на примере типовой команды (с использованием упрощенных структурных схем устройства управления, арифметико-логического устройства и типовой структуры микропроцессора).

• Первый такт: считывание КОП из ОЗУ по адресу, установленному в регистре-счетчике команд, запись этого кода в блок регистров команд устройства управления, декодирование КОП, приращение регистра счётчика команд.

• Второй такт: запись содержимого аккумулятора в буферный регистр АЛУ.

• Третий такт: считывание из ячейки ОЗУ по адресу addr второго слагаемого и перемещение его во второй буферный регистр АЛУ, приращение регистра счётчика команд;

• Четвёртый такт: сложение в АЛУ переданных туда чисел и формирование суммы.

• Пятый такт: считывание из АЛУ суммы чисел и запись её в аккумулятор.

Далее МП приступит к выполнению следующей команды по адресу, содержащемуся в регистре-счётчике команд. Команды будут выполняться последовательно одни за другой, пока не завершится вся программа.