- •Экзаменационный билет № 1

- •Экзаменационный билет № 2

- •Экзаменационный билет № 3

- •Экзаменационный билет № 4

- •Экзаменационный билет № 5

- •Экзаменационный билет № 6

- •Экзаменационный билет № 7

- •Экзаменационный билет № 8

- •Экзаменационный билет № 9

- •Экзаменационный билет № 10

- •Экзаменационный билет № 11

- •Экзаменационный билет № 12

- •Экзаменационный билет № 13

- •Экзаменационный билет № 14

- •Экзаменационный билет № 15

- •Экзаменационный билет № 16

- •Экзаменационный билет № 17

- •Экзаменационный билет № 18

- •Экзаменационный билет № 19

- •Экзаменационный билет № 20

Экзаменационный билет № 3

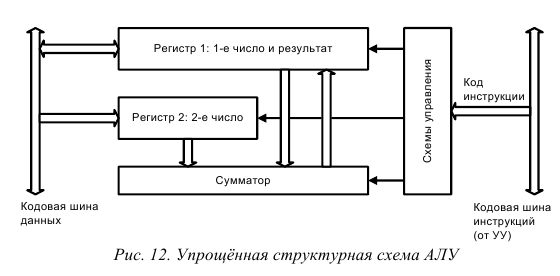

Арифметико-логическое устройство (АЛУ), функции АЛУ.

Арифметико-логическое устройство (АЛУ) – предназначено для выполнения всех арифметических и логических операций над числовой и символьной информацией.

Основные функции АЛУ:

1. Приём операндов из ОЗУ и регистров (микропроцессорной памяти).

2. Выполнение арифметических и логических операций.

3. Передача результатов в регистры и в ОЗУ.

4. Формирование признаков результатов выполнения операций и их запись в регистр слова состояния процессора.

Основные системные шины ISA, PCI (общие сведения).

ISA (от англ.IndustryStandardArchitecture, ISAbus, произносится как ай-эс-эй) — 8- или 16-разрядная шина ввода/вывода IBMPC-совместимых компьютеров. Служит для подключения плат расширения стандарта ISA. Конструктивно выполняется в виде 62-х или 98-контактного разъёма на материнской плате. Максимально адресное пространство для устройств ввода/вывода, поддерживаемое шиной ISA составляет 64 Кб (16 адресных линий). Первые 256 адресов зарезервированы для устройств, расположенных, как правило, на материнской плате - регистры контроллера ПДП, контроллера прерываний, часов реального времени, таймера-счетчика и других устройств, требующихся для AT совместимости различных компьютеров.При описании шины целесообразно представить компьютер как состоящий из материнской платы (motherboard) и внешних плат, которые взаимодействуют между собой и ресурсами материнской платы через шину

PCI — шина ввода/вывода для подключения периферийных устройств к материнской плате компьютера.Шина децентрализована, нет главного устройства, любое устройство может стать инициатором транзакции. Для выбора инициатора используется арбитраж с отдельно стоящей логикой арбитра. Арбитраж «скрытый», не отбирает времени — выбор нового инициатора происходит во время транзакции, исполняемой предыдущим инициатором. Транзакция состоит из 1 или 2 циклов адреса (2 цикла адреса используются для передачи 64-битных адресов, поддерживаются не всеми устройствами, дают поддержку DMA на памяти более 4 Гб) и одного или многих циклов данных. Поддерживаются «расщеплённые» транзакции, когда целевое устройство отвечает состоянием «в процессе» и инициатор должен освободить шину для других устройств, захватить её снова через арбитраж и повторить транзакцию. Это делается, пока целевое устройство не ответит «сделано». Используется для сопряжения шин с разными скоростями (сама PCI и frontside процессора) и для предотвращения тупиковых ситуаций в сценарии со многими межшинными мостами. Транзакция (англ. transaction) — в информатике, группа последовательных операций, которая представляет собой логическую единицу работы с данными. Транзакция может быть выполнена либо целиком и успешно, соблюдая целостность данных и независимо от параллельно идущих других транзакций, либо не выполнена вообще и тогда она не должна произвести никакого эффекта.

Экзаменационный билет № 4

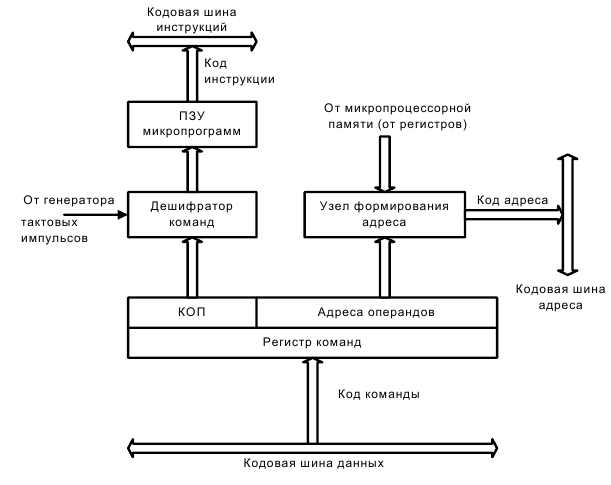

Устройство управления (УУ), функции УУ.

Устройство управления (УУ) – формирует и подает во все блоки машины в нужные моменты времени определенные сигналы управления (управляющие импульсы), обусловленные спецификой выполняемой операции и результатами предыдущих операций; формирует адреса ячеек памяти, используемых выполняемой операцией, и передает эти адреса в соответствующие блоки ЭВМ.

Основные

функции:

1. Формирование адреса инструкции.

2. Считывание инструкции из ОЗУ (ПЗУ) и её хранение во время выполнения.

3. Дешифрация кода операции.

4. Формирование управляющих сигналов.

5. Считывание из регистра команд и регистров микропроцессорной памяти отдельных составляющих адресов операндов (чисел), участвующих в вычислениях, и формирование полных адресов операндов.

6. Выборка операндов (по сформированным адресам) и выполнение заданной операции обработки этих операндов.

7. Запись результатов операции в память.

8. Формирования адреса следующей команды программы.

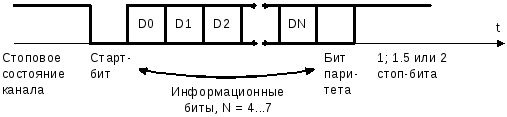

Асинхронная последовательная передача данных, сигнальные линии. Формат информационного кадра (временная диаграмма). Основы программирования последовательной асинхронной передачи данных.

В асинхронном режиме побитная синхронизация приемника и передатчика осуществляется обычно по первому (стартовому) биту и затем поддерживается абонентами в течение времени передачи кадра стабильностью тактовых частот генераторов передатчика и приемника, частоты которых равны и, как правило, минимум в 16 раз превышают частоту передачи данных.

Покадровая синхронизация в асинхронном режиме осуществляется обрамлением информации при передаче по линии стартовым и стоповым битами.

Стандартный кадр для асинхронного режима передачи данных представлен на рисунке