Структура вычислительной системы — это совокупность ее функциональных элементов и связей между ними. Элементами могут быть самые различные устройства, узлы и элементы устройств и компьютеров. Структура графически представляется в виде структурных схем, с помощью которых можно дать описание вычислительной системы на любом уровне детализации.

Архитектурой вычислительной системы называется ее описание на некотором общем уровне, включающее описание пользовательских возможностей программирования, системы команд, системы адресации, организации памяти и т.д. Архитектура определяет принципы действия, информационные связи и взаимное соединение основных логических узлов вычислительной системы.

НУЛЕВОЕ ПОКОЛЕНИЕ. МЕХАНИЧЕСКИЕ ВЫЧИСЛИТЕЛЬНЫЕ УСТРОЙСТВА (1642-1945 гг.)

Суммирующая машина Блеза Паскаля (1642):

Выполняет операции: сложения и вычитания

Механическая машина Готфрида Вильгельма Лейбница (1673):

Выполняет операции: сложение, вычитание, умножение и деление

НУЛЕВОЕ ПОКОЛЕНИЕ. МЕХАНИЧЕСКИЕ ВЫЧИСЛИТЕЛЬНЫЕ УСТРОЙСТВА (1642-1945 гг.)

Разностная машина Чарльза Бэббиджа (1834):

только складывать и вычитать,

заложен только один алгоритм — метод конечных разностей с использованием полиномов

Аналитическая машина Чарльза Бэббиджа (1834) состоит из :

запоминающее устройство (память),

вычислительное устройство,

устройство ввода (для считывания перфокарт),

устройство вывода (перфоратор и печатающее устройство).

Аналитическая машина могла выполнять разные задачи.

НУЛЕВОЕ ПОКОЛЕНИЕ. МЕХАНИЧЕСКИЕ ВЫЧИСЛИТЕЛЬНЫЕ УСТРОЙСТВА (1642-1945 гг.)

Электромеханическое вычислительное устройство Говарда Айкена «Марк I»:

Запоминающее устройство - 72 слова по 23 десятичных разряда каждое;

Выполнение любой команды за 6 секунд.

В устройствах ввода-вывода использовалась перфолента.

ПЕРВОЕ ПОКОЛЕНИЕ — ЭЛЕКТРОННЫЕ ЛАМПЫ (1945-1955)

ENIAC (Electronic Numerical Integrator and Computer — электронный цифровой интегратор и калькулятор) Джона Моушли и Дж. Преспера Экерта(1946):

Состоял из 18 000 электровакуумных ламп и 1500 реле.

ENIAC весил 30 тонн и потреблял 140 киловатт электроэнергии.

У машины было 20 регистров, каждый из которых мог содержать 10-разрядное десятичное число

Производительность приблизительно в 500 флопс.

ПЕРВОЕ ПОКОЛЕНИЕ — ЭЛЕКТРОННЫЕ ЛАМПЫ (1945-1955)

EDS AC (Electronic Delay Storage Automatic Computer) Мориса Уилкса (1949):

3000 электронных ламп,

потребляемая мощность — 12 кВт,

занимаемая площадь — 20 м²

первый компьютер с программами, хранящимися в памяти

ПЕРВОЕ ПОКОЛЕНИЕ — ЭЛЕКТРОННЫЕ ЛАМПЫ (1945-1955)

IAS (Immediate Address Storage — память с прямой адресацией) Фон Неймана (1952) состояла из пяти основных частей:

памяти,

арифметико-логического устройства,

устройства управления,

устройства ввода,

устройства вывода.

Использование двоичной системы исчисления.

Эти принципы используются в большинстве современных компьютеров.

IBM-701 (1953) - первый компьютер, лидирующий на рынке в течение десяти лет

ВТОРОЕ ПОКОЛЕНИЕ — ТРАНЗИСТОРЫ (1955-1965)

PDP-1 (1961) корпорации DEC (Digital Equipment Corporation) - первый мини-компьютер:

память - 4 Кбайт слов по 18 битов

время цикла 5 микросекунд.

IBM 360 (1964) - семейство компьютеров класса мейнфреймов (начало производства на транзисторах).

Это семейство компьютеров с одним и тем же языком (ассемблером).

Мультипрограммирование. В памяти компьютера могло находиться одновременно несколько программ, и пока одна программа ждала, когда закончится процесс ввода-вывода, другая выполнялась.

Компьютеры серии IBM-360 могли имитировать работу других компьютеров, потому что они создавались с использованием микропрограммирования.

CDC 6600 был в 3 раза быстрее своего главного конкурента — компьютера IBM Stretch— при гораздо более низкой цене — чуть больше 7 млн долларов США против 13 млн за IBM Stretch.

ТРЕТЬЕ ПОКОЛЕНИЕ — ИНТЕГРАЛЬНЫЕ СХЕМЫ (1965-1980)

PDP-8 (1965) - первый мини-компьютер массового потребления.

PDP-11(1970) - русский аналог PDP-11 - ЭВМ серии «Электроника-60» и СМ-1700 Некоторые из машин серии были прямыми аналогами PDP-11 на отечественной элементной базе

ТРЕТЬЕ ПОКОЛЕНИЕ — ИНТЕГРАЛЬНЫЕ СХЕМЫ (1965-1980)

Схема фирмы Intel 8080 (1974) - первый восьмибитный микропроцессор общего назначения.

Apple I (1976) - первый персональный компьютер. Но первым массовым персональным компьютером, выпускавшимся миллионами экземпляров, стал компьютер Apple II (1977)

ЧЕТВЕРТОЕ ПОКОЛЕНИЕ — СВЕРХБОЛЬШИЕ ИНТЕГРАЛЬНЫЕ СХЕМЫ (1980-?)

IBM тоже решила заняться производством персональных компьютеров. Но вместо того чтобы конструировать компьютер с нуля, что заняло бы слишком много времени, компания IBM предоставила одному из своих работников, Филипу Эстриджу, на разработку персонального компьютера. Эстридж открыл предприятие, взял Intel 8088 в качестве центрального процессора и создал персональный компьютер из серийных компонентов. Этот компьютер (IBM PC) появился в 1981 году и стал самым покупаемым компьютером в истории.

Но компания IBM сделала одну вещь, о которой она позже пожалела. Вместо того чтобы держать проект машины в секрете (или по крайней мере оградить себя патентами), как она обычно делала, компания опубликовала полные проекты, включая все электронные схемы, в книге стоимостью $49. Эта книга была опубликована для того, чтобы другие компании могли производить сменные платы для IBM PC, что повысило бы совместимость и популярность этого компьютера. К несчастью для IBM, как только проект IBM PC стал широко известен, поскольку все составные части компьютера можно было легко приобрести, многие компании начали делать клоны PC и часто продавали их гораздо дешевле, чем IBM. Так началось бурное производство персональных компьютеров.

Накопители на гибких магнитных дисках.

Дискеты (гибкие магнитные диски):

8 дюймов (80, 256, 800 КБ) = 12.000 перфокарт или около 300 метров перфоленты

5,25 дюйма (110, 360, 720, 1200 КБ)

3,5 дюйма (1,44, 2,88 Мб)

Iomega Zip (100, 250, 750 Мб)

Классическая архитектура (архитектура фон Неймана)

Классическая архитектура (архитектура фон Неймана) — одно арифметико-логическое устройство, через которое проходит поток данных, и одно устройство управления, через которое проходит поток команд — программа. Это однопроцессорный компьютер

Принципы фон Неймана

Принцип однородности памяти

Команды и данные хранятся в одной и той же памяти и внешне в памяти неразличимы. Распознать их можно только по способу использования; то есть одно и то же значение в ячейке памяти может использоваться и как данные, и как команда, и как адрес в зависимости лишь от способа обращения к нему.

Принцип адресности

Структурно основная память состоит из пронумерованных ячеек, причем процессору в произвольный момент доступна любая ячейка. Двоичные коды команд и данных разделяются на единицы информации, называемые словами, и хранятся в ячейках памяти, а для доступа к ним используются номера соответствующих ячеек — адреса.

Принцип программного управления

Команды программы хранятся в последовательных ячейках памяти вычислительной машины и выполняются в естественной последовательности, то есть в порядке их положения в программе. При необходимости, с помощью специальных команд, эта последовательность может быть изменена.

Принцип двоичного кодирования

Согласно этому принципу, вся информация, как данные, так и команды, кодируются двоичными цифрами 0 и 1. Каждый тип информации представляется двоичной последовательностью и имеет свой формат.

Классификация архитектур вычислительных систем с параллельной обработкой данных

Цели, которым должна служить хорошо построенная классификация архитектур:

облегчать понимание того, что достигнуто на сегодняшний день в области архитектур вычислительных систем, и какие архитектуры имеют лучшие перспективы в будущем;

подсказывать новые пути организации архитектур — речь идет о тех классах, которые в настоящее время по разным причинам пусты;

показывать, за счет каких структурных особенностей достигается увеличение производительности различных вычислительных систем; с этой точки зрения классификация может служить моделью для анализа производительности.

Классификация М. Флинна

|

Поток данных |

Поток команд | |

|

|

одиночный |

множественный |

|

Одиночный |

SISD - Single Instruction stream / Single Data stream (Одиночный поток Команд и Одиночный поток Данных - ОКОД) |

MISD - Multiple Instruction stream / Single Data stream (Множественный поток Команд и Одиночный поток Данных - МКОД) |

|

Множественный |

SIMD - Single Instruction stream / Multiple Data stream (Одиночный поток Команд и Множественный поток Данных - ОКМД) |

MIMD - Multiple Instruction stream / Multiple Data stream (Множественный поток Команд и Множественный поток Данных - МКМД) |

Классификация Джонсона.

Это классификация MIMD-архитектур на основе структуры памяти и реализации механизма взаимодействия и синхронизации между процессорами.

|

Обмен данными |

Память | |

|

общая |

распределенная | |

|

Общие данные |

GMSV - General Memory-Shared variables (Общая память - разделяемые переменные) Класс 1. «Системы с разделяемой памятью» |

DMSV - Distributed Memory, Shared variables (Распределенная память - разделяемые переменные) Класс 2. «Гибридная архитектура» |

|

Передача данных |

GMMP - General Memory, Message propagation (Общая память - передача сообщений) |

DMMP - Distributed Memory, Message propagation) (Распределенная память - передача сообщений) Класс 3. «Архитектуры с передачей сообщений» |

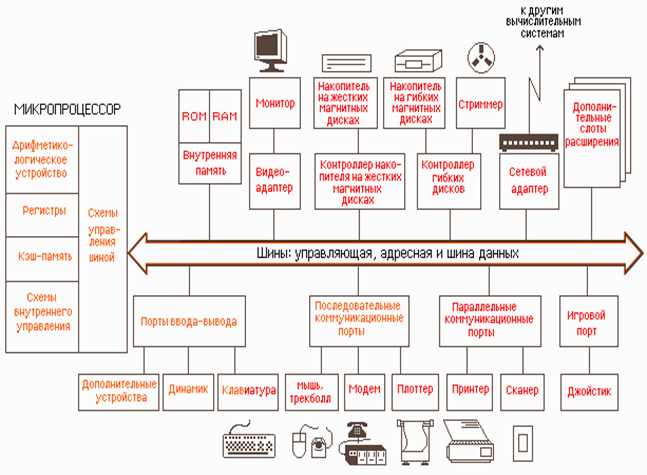

Общая структура персонального компьютера с подсоединенными периферийными устройствами

Технические характеристики аппаратных платформ

Процессоры

Основные характеристики процессоров

Основными характеристиками центральных процессоров являются:

Тип архитектуры или серия (Intel x86, Intel Pentium, Pentium overdrive, RISC …)

Система поддерживаемых команд (standard 86/88, 286, 386, 486, Pentium,( Pentium2-4),MMX) и адресации (real mode, protected mode, virtual mode, EMS, paging).

Разрядность (бит)

Количество ядер

Тактовая частота (мгц)

КЭШ

Гнездо для процессора (Socket 7, Slot1 и др.)

Величина питающего напряжения (Вольт)

Архитектура системы команд. Классификация процессоров (CISC и RISC)

В широком смысле архитектура охватывает понятие организации системы, включающее такие высокоуровневые аспекты разработки компьютера как систему памяти, структуру системной шины, организацию ввода/вывода и т.п.

Процессор c полным набором команд

Для процессоров c полным набором команд (CISC-процессоров) характерно:

сравнительно небольшое число регистров общего назначения;

RAX

RBX

RCX

RDX

EAX

EBX

ECX

EDX

AX

BX

CX

DX

AH

AL

BH

BL

CH

CL

DH

DL

большое количество методов адресации;

большое количество форматов команд различной разрядности;

преобладание двухадресного формата команд;

наличие команд обработки типа регистр-память.

Процессоры с сокращенным набором команд

Для процессоров с сокращенным набором команд (RISC - Reduced Instruction Set Computer) характерно:

Выполнение любой команды занимало небольшое количество машинных тактов (предпочтительно один машинный такт).

Наличие достаточно большого регистрового файла (в типовых RISC-процессорах реализуются 32 или большее число регистров по сравнению с 8 - 16 регистрами в CISC-архитектурах).

Конвейерная организация работы и большая скорость выполнения команд.

Реализация задержанных переходов и суперскалярной обработки.

Основные элементы процессора

Регистры

АЛУ – арифметико-логическое устройство

БУ – блок управления

ТГ – тактовый генератор

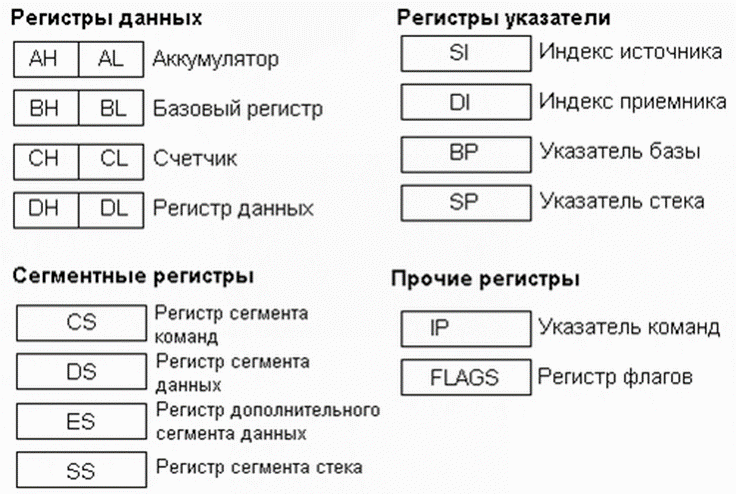

Процессор архитектуры x86 содержит:

регистры общего назначения,

сегментные регистры,

указатель команд,

регистр флагов.

Регистры общего назначения (РОН)

служат для хранения промежуточных вычислений.

RAX, RCX, RDX, RBX, RSP, RBP, RSI, RDI, R8 — R15 — 64-битные

EAX, ECX, EDX, EBX, ESP, EBP, ESI, EDI, R8D — R15D — 32-битные (extended AX)

AX, CX, DX, BX, SP, BP, SI, DI, R8W — R15W — 16-битные

AH, AL, CH, CL, DH, DL, BH, BL, SPL, BPL, SIL, DIL, R8B — R15B — 8-битные (половинки 16-ти битных регистров)

например, AH — high AX — старшая половинка 8 бит AL — low AX — младшая половинка 8 бит

Счётчик команд

Регистр, содержащий адрес-смещение следующей команды, подлежащей исполнению, относительно кодового сегмента CS в процессорах семейства x86.

Регистр IP связан с CS в виде CS:IP, где CS является текущим кодовым сегментом, а IP — текущим смещением относительно этого сегмента.

Регистр IP является регистром-указателем. Кроме него, в состав регистров этого типа входят SP (англ. Stack Pointer — указатель стека) и BP (англ. Base Pointer — базовый указатель).

При выполнении текущей инструкции процессор автоматически изменяет значение в регистре IP, в результате чего регистровая пара CS:IP всегда указывает на следующую подлежащую исполнению инструкцию.

Регистр флагов FLAGS / EFLAGS / RFLAGS

Флаги состояния (биты 0, 2, 4, 6, 7 и 11) отражают результат выполнения арифметических инструкций, таких как ADD, SUB, MUL, DIV.(+-/*):

CF — устанавливается при переносе из/заёме в (при вычитании) старший значащий бит результата и показывает наличие переполнения в беззнаковой целочисленной арифметике.

PF — устанавливается, если младший значащий байт результата содержит чётное число единичных (ненулевых) битов.

AF — устанавливается при переносе или заёме из бита 4 результата. Этот флаг ориентирован на использование в двоично-десятичной арифметике.

ZF — устанавливается, если результат машинной операции по модулю 2 в степени k (где k - разрядность ячейки) равен нулю.

SF — равен значению старшего значащего бита результата, который является знаковым битом в знаковой арифметике.

OF — устанавливается, если целочисленный результат слишком длинный для размещения в целевом операнде (регистре или ячейке памяти). Этот флаг показывает наличие переполнения в знаковой целочисленной арифметике (в дополнительном коде).

Регистр флагов FLAGS / EFLAGS / RFLAGS

Системные флаги и поле IOPL

IF — обнуление этого флага запрещает отвечать на маскируемые запросы на прерывание.

TF — установка этого флага разрешает пошаговый режим отладки.

IOPL (биты 12 и 13)— показывает уровень приоритета ввода-вывода исполняемой программы или задачи: чтобы программа или задача могла выполнять инструкции ввода-вывода или менять флаг IF, её текущий уровень приоритета (CPL) должен быть ≤ IOPL.

NT — этот флаг устанавливается, когда текущая задача «вложена» в другую, прерванную задачу, и сегмент состояния TSS текущей задачи обеспечивает обратную связь с TSS предыдущей задачи. Флаг NT проверяется инструкцией IRET для определения типа возврата — межзадачного или внутризадачного.

RF — флаг маскирования ошибок отладки.

VM — установка этого флага в защищённом режиме вызывает переключение в режим виртуального 8086.

AC — установка этого флага вместо с битом AM в регистре CR0 включает контроль выравнивания операндов при обращениях к памяти — обращение к невыравненному операнду вызывает исключительную ситуацию.

VIF — виртуальная копия флага IF; используется совместно с флагом VIP.

VIP — устанавливается для указания наличия отложенного прерывания; используется совместно с флагом VIF.

ID — возможность программно изменить этот флаг в регистре флагов указывает на поддержку инструкции CPUID.

Система команд.

Команды

Команда — это описание элементарной операции, которую должен выполнить компьютер.

В общем случае, команда содержит следующую информацию:

· код выполняемой операции;

· указания по определению операндов (или их адресов);

· указания по размещению получаемого результата.

В зависимости от количества операндов, команды бывают:

· безадресные;

· одноадресные;

· двухадресные;

· трехадресные;

· четырехадресные;

· переменноадресные.

Варианты команды сложения

одноадресная команда add x (содержимое ячейки x сложить с содержимым сумматора, а результат оставить в сумматоре)

двухадресная команда add x, y (сложить содержимое ячеек x и y, а результат поместить в ячейку y)

трехадресная команда add x, y, z (содержимое ячейки x сложить с содержимым ячейки y, сумму поместить в ячейку z)

четырехадресная команда add x, y, z (содержимое ячейки x сложить с содержимым ячейки y, сумму поместить в ячейку z, выполнить и выполнить следующую команду по адресу А)

Время выполнения команды

Время выполнения одной команды складывается из времени выполнения операции и времени обращения к памяти. Для трехадресной команды последнее суммируется из четырех составляющих времени:

выборки команды;

выборки первого операнда;

выборки второго операнда;

Одноадресная команда требует двух обращений к памяти:

выборки команды;

выборки операнда.

Кодирование команд

Команды преобразования дискретной информации могут быть:

передача информации в пространстве;

хранение информации;

логические операции;

арифметические операции.

По характеру выполняемых операций различают команды:

1) команды арифметических операций для чисел с фиксированной и плавающей запятой;

2) команды десятичной арифметики;

3) команды логических операций;

4) команды передачи кодов;

5) команды ввода-вывода;

6) команды передачи управления;

7) команды задания режима работы машины.

Способы адресации

Подразумеваемый операнд (Неявная адресация).

В команде может не содержаться явных указаний об операнде; в этом случае операнд подразумевается и фактически задается кодом операции команды.

Пример:

Inc rax

Увеличение операнда на 1.

Подразумеваемый адрес

В команде может не содержаться явных указаний об адресе участвующего в операции операнда или адресе, по которому должен быть размещен результат операции, но этот адрес подразумевается. Примеры:

cbw

mul al

Команда CBW (Команда копирует знаковый бит регистра AL/AX на все биты регистра АН/ЕАХ.) всегда работает с регистрами AX и AL, а у команды MUL фиксировано положение первого множителя и результата (Команда выполняет целочисленное умножение без учёта знака. Явно задается один из множителей. Второй множитель задается неявно в регистре AL/AX/EAX (это местоположение фиксировано).). Такой режим адресации делает машинную команду короткой, так как в ней отсутствует указание одного или нескольких операндов.

Непосредственная адресация.

В команде содержится не адрес операнда, а непосредственно сам операнд. При непосредственной адресации не требуется обращения к памяти для выборки операнда и ячейки памяти для его хранения. Это способствует уменьшению времени выполнения программы и занимаемого ею объема памяти. Непосредственная адресация удобна для хранения различного рода констант.

При непосредственной адресации значение операнда является частью машинной команды. Понятно, что в этом случае операнд представляет собой константу. Примеры:

mov al,5

add bx,1234h

Прямая адресация

В адресной части команды может быть непосредственно указан исполнительный адрес.

В машинной команде содержится адрес операнда, находящегося в памяти. Пример:

mov dx,[a]

Вот тут уже в DX помещается значение из памяти по адресу a. Сравните с предыдущим пунктом. Квадратные скобки обозначают обращение по адресу, указанному внутри этих скобок.

Относительная (базовая) адресация

При этом способе адресации исполнительный адрес определяется как сумма адресного кода команды и базового адреса, как правило хранящегося в специальном регистре - регистре базы

Этот режим используется в командах передачи управления. В машинной команде содержится смещение, которое прибавляется к значению указателя команд IP. То есть указывается не сам адрес перехода, а на сколько байтов вперёд или назад надо перейти. Пример:

metka:

...

loop metka

У такого режима адресации два преимущества. Во-первых, машинная команда становится короче, так она содержит не полный адрес, а только смещение. Во-вторых, такой код не зависит от адреса, по которому он размещается в памяти.

Укороченная адресация

Для уменьшения длины кода команды часто применяется так называемая укороченная адресация. Суть ее сводится к тому, что в команде задаются только младшие разряды адресов, а старшие разряды при этом подразумеваются нулевыми. Регистровая адресация является частным случаем укороченной, когда в качестве фиксированных ячеек с короткими адресами используются регистры процессора. Например, если таких регистров 16, то для адреса достаточно четырех двоичных разрядов. Регистровая адресация наряду с сокращением длины адресов операндов позволяет увеличить скорость выполнения операций, так как уменьшается число обращений к оперативной памяти.

Операнд находится в регистре. Пример:

add ax,bx

Косвенная адресация

Адресный код команды в этом случае указывает адрес ячейки памяти, в которой находится адрес операнда или команды(«адрес адреса»). Косвенная адресация широко используется в малых и микроЭВМ, имеющих короткое машинное слово, для преодоления ограничений короткого формата команды.

Адрес операнда находится в одном из регистров BX, SI или DI. Примеры:

add ax,[bx]

mov dl,[si]

Размер операнда в памяти здесь определяется размером первого операнда. Косвенная регистровая (базовая) адресация со смещением

Адрес операнда вычисляется как сумма содержимого регистра BX, BP, SI или DI и 8- или 16-разрядного смещения. Примеры:

add ax,[bx+2]

mov dx,[array1+si]

В качестве смещения можно указать число или адрес метки. О размере смещения не беспокойтесь — компилятор сам его определяет и использует нужный формат машинной команды.

Адресация слов переменной длины

Эффективность вычислительных систем, предназначенных для обработки данных, повышается, если имеется возможность выполнять операции со словами переменной длины. В этом случае в машине может быть предусмотрена адресация слов переменной длины, которая обычно реализуется путем указания в команде местоположения в памяти начала слова и его длины.

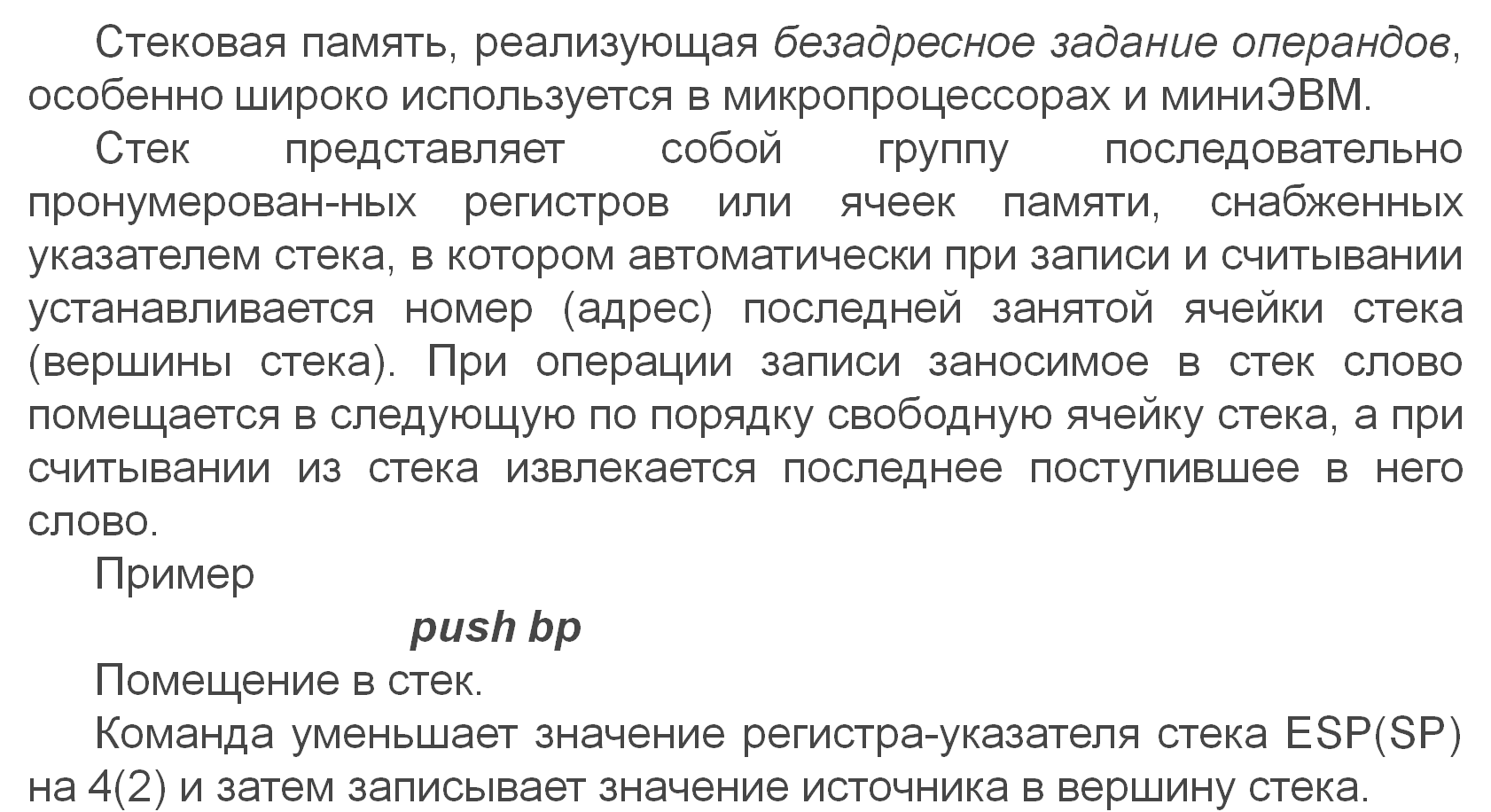

Стековая

адресация

Автоинкрементная и автодекрементная адресации

Это механизм автоматического приращения или уменьшения содержимого регистра при каждом обращении к нему. Такой механизм называется соответственно автоинкрементной и автодекрементной адресацией. При автоинкрементной адресации сначала содержимое регистра используется как адрес операнда, а затем получает приращение, равное числу байт в элементе массива.

Автоинкрементная и автодекрементная адресации могут рассматриваться как упрощённый вариант индексации - весьма важного механизма преобразования адресных частей команд и организации вычислительных циклов, поэтому их часто называют автоиндексацией.

Пример: