Шпоры по ЭСА

.pdf

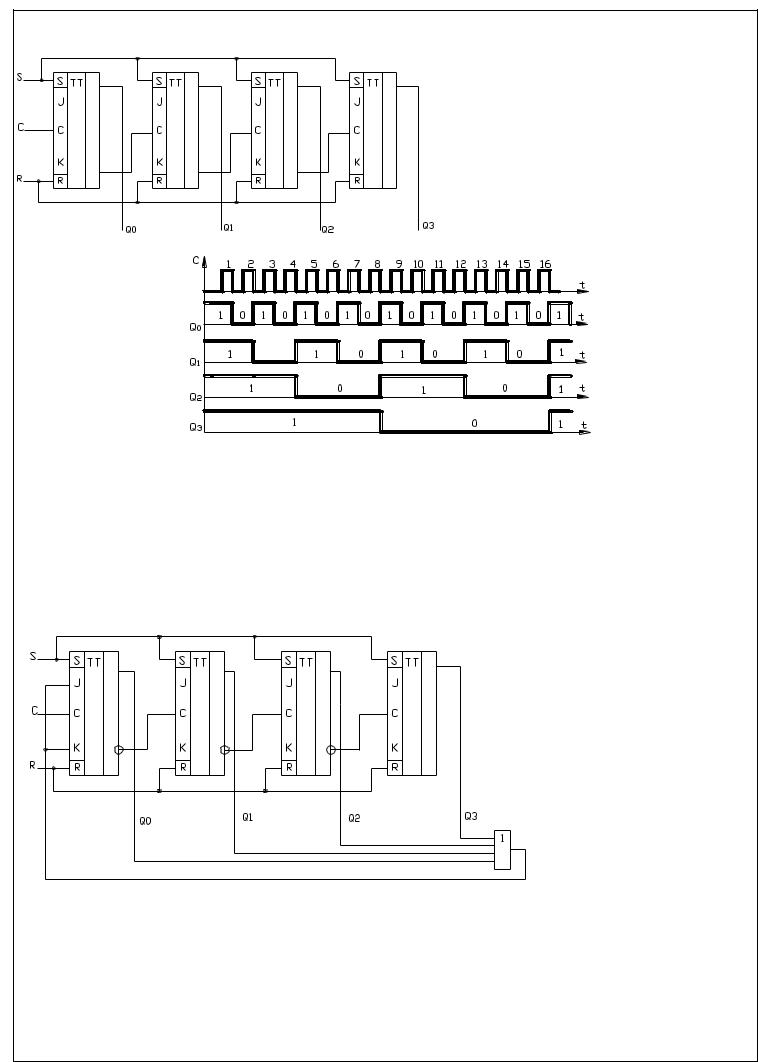

Вычитающие счѐтчики |

|

|

|

Ранее мы рассматривали счѐтчики, у |

|||

которых число на выходе с приходом |

|||

каждого импульса увеличивалось на |

|||

1. В вычитающем счѐтчике приход |

|||

каждого импульса уменьшает на 1 |

|||

число на выходе. Исходное состояние |

|||

вычитающего счѐтчика, в отличии от |

|||

суммирующего, |

единичное. |

|

|

Спад первого тактового импульса переключает первый триггер в состояние 0. На инверсном |

|||

выходе этого триггера появляется 1, которая подаѐтся на тактовый импульс второго тригге- |

|||

ра. После второго тактового импульса вновь происходит переключение первого триггера, |

|||

т.к. он работает в переключающем режиме. На инверсном выходе первого триггера появля- |

|||

ется 0, что является сигналом переключения второго триггера. Дальше аналогично. |

|

||

Вычитающий счётчик с самоостановом |

|

|

|

Часто возникает необходимость остановить счѐт при определѐнном выходном коде. На схе- |

|||

ме |

показана |

реализация |

|

самоостанова |

|

счѐтчика |

|

при нуле. |

|

|

|

Исходное состояние счѐт- |

|||

чика «1» и пока хотя бы |

|||

на |

одном |

из |

выходов |

счѐтчика имеется «1», ко- |

|||

торая подаѐтся на входы J |

|||

и K – первого триггера, |

|||

обеспечивая |

возможность |

||

его работы в переклю- |

|||

чающем режиме. |

|

||

«0» на выходе элемента появляется только тогда, когда на всех входах будет «0». «0» с вы- |

|||

хода элемента «ИЛИ», будучи поданным на входа J и K первого триггера переводит его в |

|||

режим хранения информации, запрещая дальнейшую работу счѐтчика. |

|

|

|

В этом состоянии он будет находится сколь угодно долго, до прихода сигнала на вход S. |

|||

|

|

|

41 |

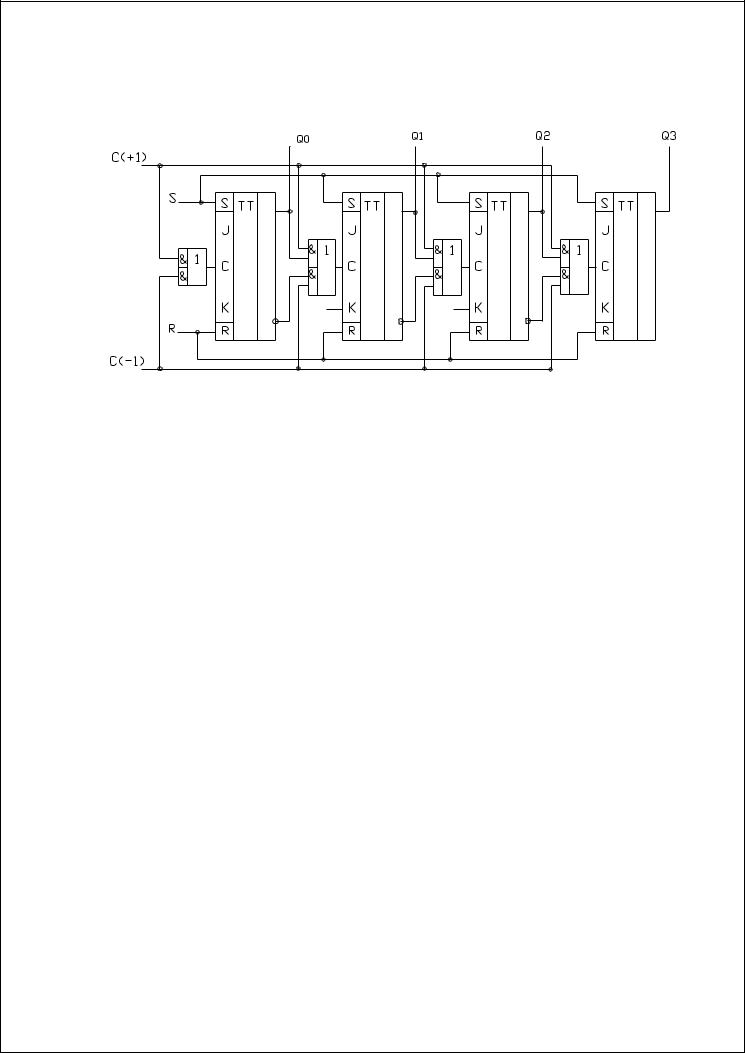

Реверсивный счѐтчик |

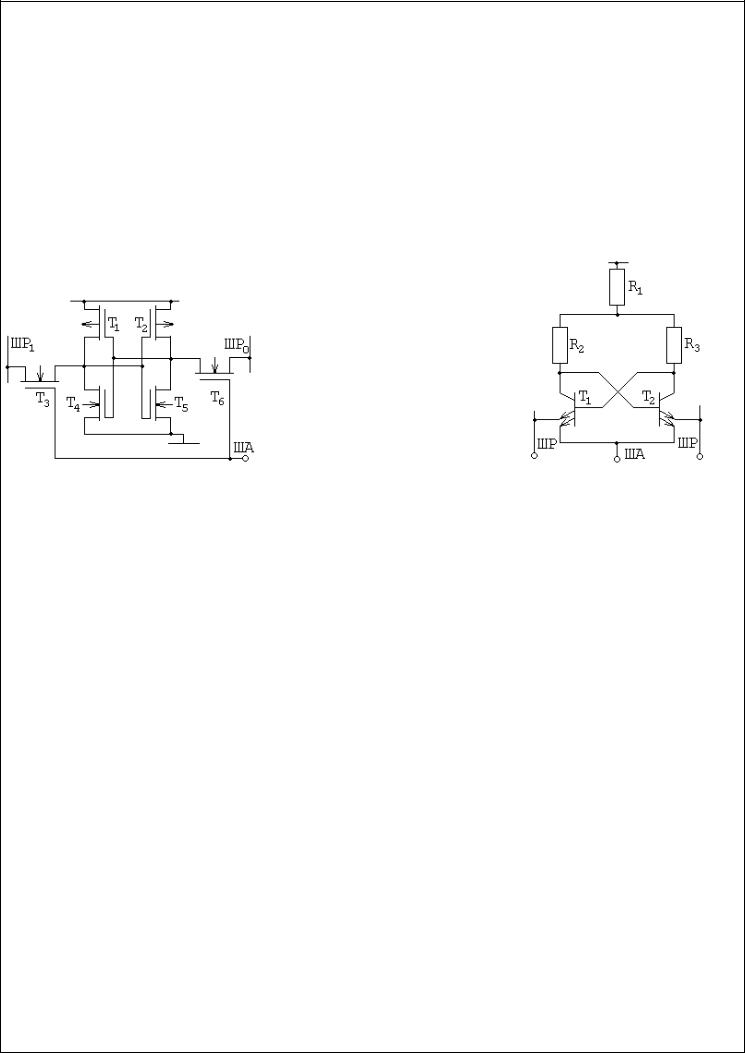

Реверсивный счѐтчик имеет два тактовых входа на увеличение и на уменьшение. Счѐтчик |

является синхронным. В этой схеме при суммировании счѐтчиком на тактовый вход «С-1» |

подаѐтся 0. В режиме вычитания счѐтчика на вход «С+1» подаѐтся 0. |

42 |

2.25 Оперативные и постоянные запоминающие устройства

Одним из важнейших функциональных устройств информационных систем являются запоминающие устройства (ЗУ). На них возлагаются функции хранения программ обработки информации и данных. Полупроводниковые ЗУ характеризуются высшим быстродействием, надежностью, малым токопотреблением. В кристалле ПП ЗУ совмещены матрица запоминающих элементов, каждый из которых хранит 1 бит информации, и схема управления, обеспечивающая обращение к запоминающим элементам. Запоминающие элементы организуются в ячейки, имеющие разрядность в несколько бит. Каждая ячейка имеет свой идентификатор, представленный двоичным кодом (адрес). Полупроводниковые ЗУ могут выполнять две основные операции:

-ввод информации в адресуемую ячейку - запись, WRITE (WR); -вывод информации из ячейки - считывание, READ (RD).

Обе операции называются операциями обращения к памяти. Если кристаллический ЗУ выполняет только операцию считывания, он называется постоянным запоминающим устройством (ПЗУ, ROM). Информация, хранимая в ПЗУ, может наноситься на заводе изготовителе в процессе изготовления микропроцессора с помощью специальных фотошаблонов. Такие микросхемы называются непрограммируемыми ПЗУ и применяются для хранения неизменяющихся программ. Следующим типом ПЗУ являются микропроцессоры, позволяющие однократное занесение информации, так называемые программируемые ПЗУ. При этом в исходном состоянии в ПЗУ уже содержится какая-либо информация. Запись информации осуществляется на специальных устройствах - программаторах, путем пережигания импульсами тока тонких проводящих перемычек. Наконец, имеются ПЗУ, позволяющие осуществлять многократное занесение информации. Эти ПЗУ называются перепрограммируемыми ПЗУ. В зависимости от способа стирания различают ПЗУ с электрическим стиранием и с ультрафиолетовым стиранием информации. Все ПЗУ являются энергонезависимыми источниками информации, так как информация, записанная в них не пропадает при исчезновении питания. Полупроводниковые ЗУ, в процессе работы выполняющие как операцию записи, так и считывание, называются запоминающими устройствами с произвольной выборкой (ЗУПВ)(RAM) и используются для создания оперативной памяти. ОЗУ являются энергозависимыми.

Полупроводниковые ЗУ имеют большое число характеристик. Наиболее важные следующие:

Емкость, выражаемая в битах, означает количество хранимой информации, например, 256 бит, 1024 бит(1 кбит) и так далее;

Организация ЗУ, например, ЗУ емкостью 1024 бита может содержать 1024 адресуемых ячейки размерностью 1 бит (1024 х 1) или 256 ячеек размерностью 4 бита (256 х 4);

Эксплуатационные характеристики (диапазон дополнительных температур, потребляемая мощность в пассивном (хранение) и активном режиме;

Быстродействие.

Кроме матрицы ЗЭ в микросхеме статического ЗУПВ содержатся схемы дешифрации, формирователи адресных сигналов, схемы согласования уровней, формирователи сигналов записи, усилители считывания, схемы выборки кристалла.

43

Постоянные запоминающие устройства

Основным требованием, предъявляемым к ПЗУ, является сохранение информации при отключении питания. Это требование обеспечивается конструкцией ЗЭ. Наиболее распространены ЗУ с ЗЭ, выполненными на биполярных и МОП-транзисторах. МОПтранзисторный ЗЭ может хранить 1 или 0 в зависимости от того, имеет ли сток транзистора связь с корпусом. Если сток изолирован от корпуса, на разрядной шине присутствует высокий уровень напряжения. Когда же сток связан с корпусом при подаче в адресную шину высокого уровня (выборка ЗЭ), на разрядной шине будет низкий уровень. Связь стоков

нужных транзисторов с корпусом устанавливается в микросхеме путем металлизации нужных участков кристалла после того, как все транзисторы уже сформированы.

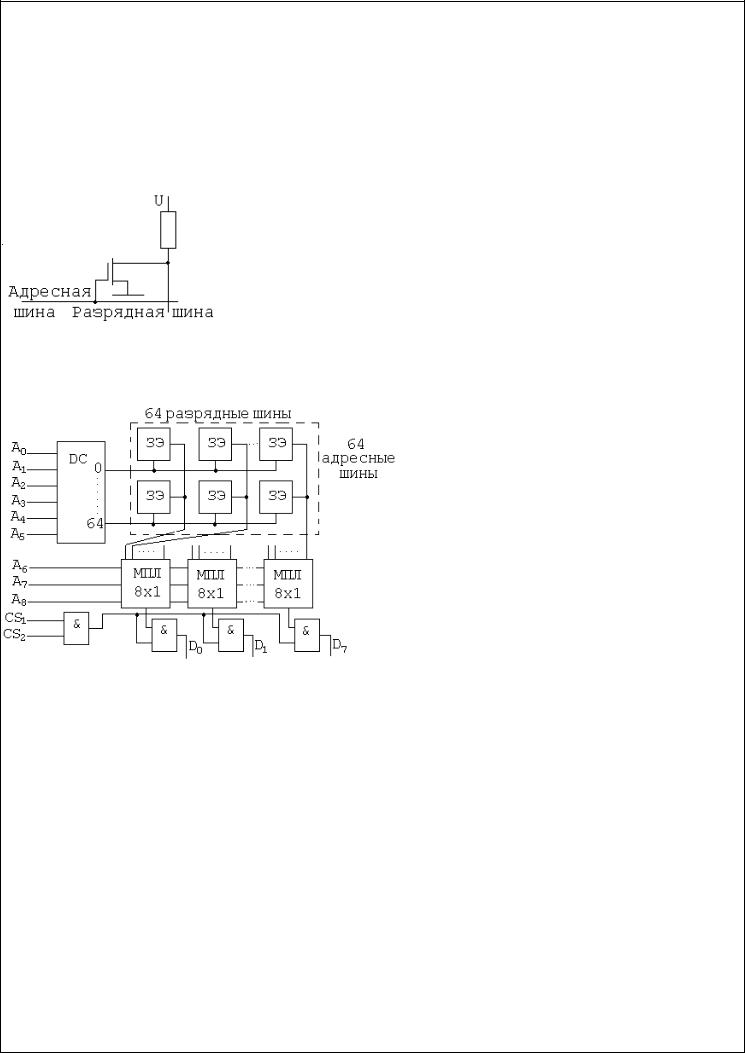

Рисунок 1 ЗЭ на МОП-транзисторе

На рис. 2 представленна структурная схема типичного полупроводникового ПЗУ с организацией 512 8.

Рисунок 2 Структурная схема полупроводникового ПЗУ

Запоминающие элементы объединены в матрицу 64 64, младшие разряды адреса А0-А5 используются для выборки 64 ЗЭ одной из сторк матрицы. Старшие разряды адреса А6-А8 управляют работой восьми мультиплексоров. Каждый мультиплексор подключен к восьмиразрядным шинам и выбирает требуемую. Сигналы выборки кристалла управляют передачей 8-битного слова с выхода мультиплексоров на выходы ЗУ D0-D7 и служат для организации ПЗУ большой ем-

кости из нескольких микросхем. В полупроводниковых ЗУ, программируемых пользователем (ППЗУ), в исходном состоянии во всех пересечениях адресных шин с разрядными выполнены ЗЭ, последовательно с которыми включаются плавкие нихромовые или титановольфрамовые перемычки, пережигаемые в процессе программирования.

Стираемые программируемые ПЗУ выполняются двух типов:

-В ПЗУ первого типа матрица ЗЭ изготавливается аналогично матрице ПЗУ по МОПтехнологии, но между металлическим затвором и слоем изолирующего окисла осаждается тонкий слой нитрида кремния, который способен захватывать и сохранять длительное время эл. заряд. Это электрически программируемое ПЗУ. В них стирание информации осуществляется определенным уровнем напряжения. Этот тип ППЗУ более надежен, т.к. гарантирован от случайного стирания информации.

-В ПЗУ второго типа матрица ЗЭ выполняется из МОП-транзисторов с плавающим затвором. Стирание информации осуществляется засвечиванием транзисторов через кварцевое окно ультрафиолетовым излучением, которое разряжает затворы транзисторов п приводит их в непроводящее состояние. При этом солнечные свет не влияет на запрограммированное ПЗУ.

44

Запоминающие устройства с произвольной выборкой

ЗУПВ служат для оперативного запоминания информации и способны хранить ее только при включенном питании. По принципу действия различают статические и динамические ЗУПВ. Запоминающими элементами статических ЗУПВ служат триггеры, которые могут быть реализованы по любой технологии. В динамических ЗУПВ носителем информации является емкость между затвором МОП-транзистора и корпусом, которая может быть заряжена или разряжена. ЗЭ биполярного ЗУПВ представляет собой асинхронный триггер с непосредственными связями, выполненный на двух эмиттерных транзисторах.

ЗЭ статического ЗУПВ на МОП-транзисторах – это триггерная схема на транзисторах VT4 и VT5, нагрузкой которых служат транзисторы VT1 и VT2. Транзисторы VT3 и VT6 – управляющие: при отпирании их положительным сигналом, передаваемым по шине адреса ША, они становятся проводящими в обоих направлениях.

Рисунок 3 - Схема биполярного ЗУПВ

Рисунок 4 - Схема ЗУПВ на КМОП-транзисторах

Биполярные ЗУПВ обладают наивысшим быстродействием среди ЗУПВ, однако, по сравнению с ЗУПВ, выполненными по КМОП-технологии, имеют значительно меньшую емкость

ибольшее энергопотребление.

Сцелью увеличения информационной емкости микросхем создали динамические ЗУПВ. Принцип действия таких ОЗУ основан на хранении заряда емкости между затвором МОП-транзистора и общей точкой микросхемы. Емкость образуется параллельно включенными емкостью затвор-сток транзистора и паразитной емкостью. Наличие или отсутствие заряда соответствует логическим 0 и 1. Для восстановления заряда есть специальный режим

– режим регенерации.

45

2.26 Цифро-аналоговые и аналогово-цифровые преобразователи

ЦАП служит для преобразования цифровой информации в аналоговую форму, т.е. выходной сигнал ЦАП в общепринятых единицах измерения тока или напряжения (мВ, В, мА) соответствует численному значению входной кодовой комбинации.

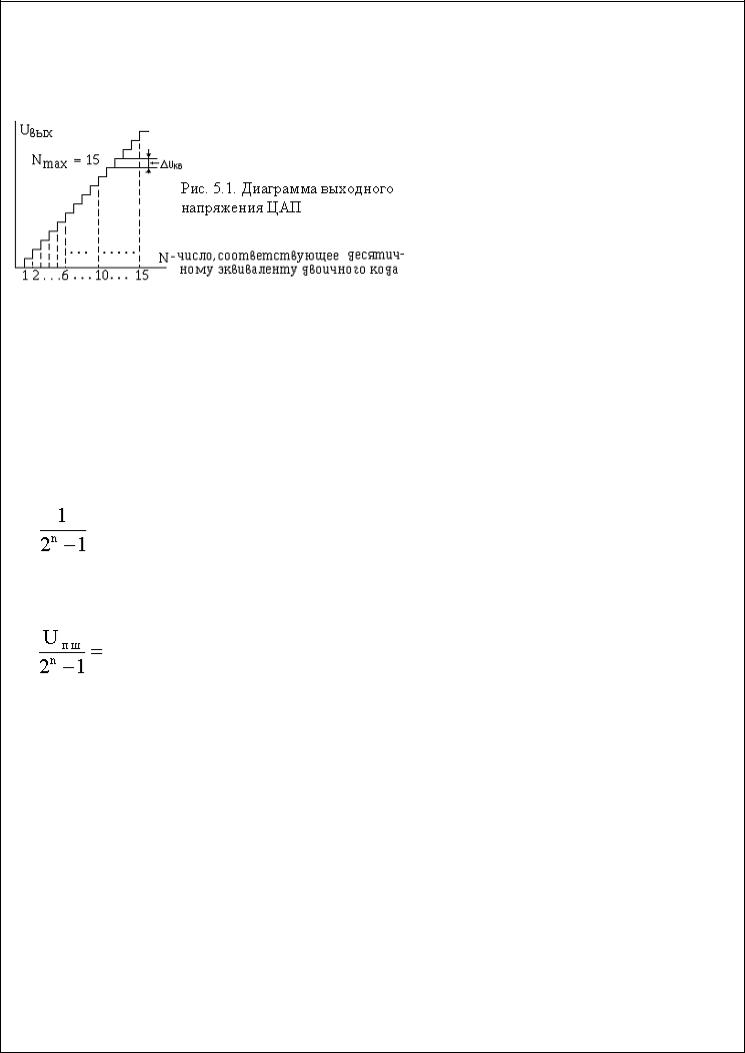

Величина напряжения, соответствующая одной единице цифровой информации, называется шагом квантования uкв. При подаче на вход ЦАП последовательной цифровой комбинации, меняющейся от 0 до N, на его выходе появится ступенчато-нарастающее напряжение (рис. 5.1). Высота каждой ступени соответствует одному шагу

квантования uкв.

Если число входной кодовой комбинации соответствует N, то выходное напряжение Uвых ЦАП = N uкв. Таким образом можно вычислить значение выходного напряжения для любой входной кодовой комбинации. Так как uкв определяет минимальное значение выходного напряжения аналогового сигнала Uвых мин. = uкв, при выборе его значения необходимо учитывать также шумовые факторы, погрешности усиления масштабирующих усилителей и компаратора.

Основные параметры ЦАП 1. Относительная разрешающая способность

о = , здесь n- количество разрядов двоичного числа, подаваемого на вход ЦАП (n - соответствует числу разрядных входов ЦАП). Относительная разрешающая способность - это обратная величина от максимального числа уровней квантования.

2. Абсолютная разрешающая способность

а = uкв, где Uпш - напряжение полной шкалы, соответствующее опорному напряжению ЦАП. Это напряжение можно считать равным максимальному выходному напряжению; 2n - 1 = N - количество ступеней квантования.

Численно абсолютная разрешающая способность равна шагу квантования uкв.

3.Абсолютная погрешность преобразования пш  показывает максимальное от-

показывает максимальное от-

клонение выходного напряжения Uвых в точке пересечения с идеальной характеристикой (прямой) на уровне напряжения полной шкалы. Абсолютная погрешность преобразования оценивается в процентах или же в единицах младшего значащего разряда (МР). При оценке значения абсолютной погрешности преобразования знак напряжения не учитывается.

4.Нелинейность преобразования ЦАП лн определяет максимальное отклонение реальной характеристики от идеальной и оценивается также в процентах или в единицах младшего значащего разряда.

5. Дифференциальная нелинейность преобразования ЦАП дф.лн численно равна максимальной разности двух соседних приращений (шагов квантования)

дф.лн = uкв 1 - uкв2.

Дифференциальная нелинейность оценивается в младших значащих разрядах и обычно не превышает нескольких единиц мр.

46

Время установления выходного напряжения или тока tуст - интервал времени от подачи входного двоичного входного кода до вхождения выходного сигнала в заданные пределы.

Максимальная частота преобразования fпр - наибольшая частота дискретизации, при которой параметры ЦАП соответствуют заданным значениям. Максимальная частота и время установления определяют быстродействие ЦАП.

Виды ЦАП условно можно разделить на две группы: с резисторными матрицами, безматричные ЦАП. В интегральном исполнении применяются только ЦАП с прецизионными резисторными матрицами, формирующими выходные сигналы путем суммирования токов.

ЦАП содержит элементы цифровой и аналоговой схемотехники. В качестве аналоговых элементов используются операционные усилители, аналоговые ключи (коммутаторы), резисторные матрицы и т.д.

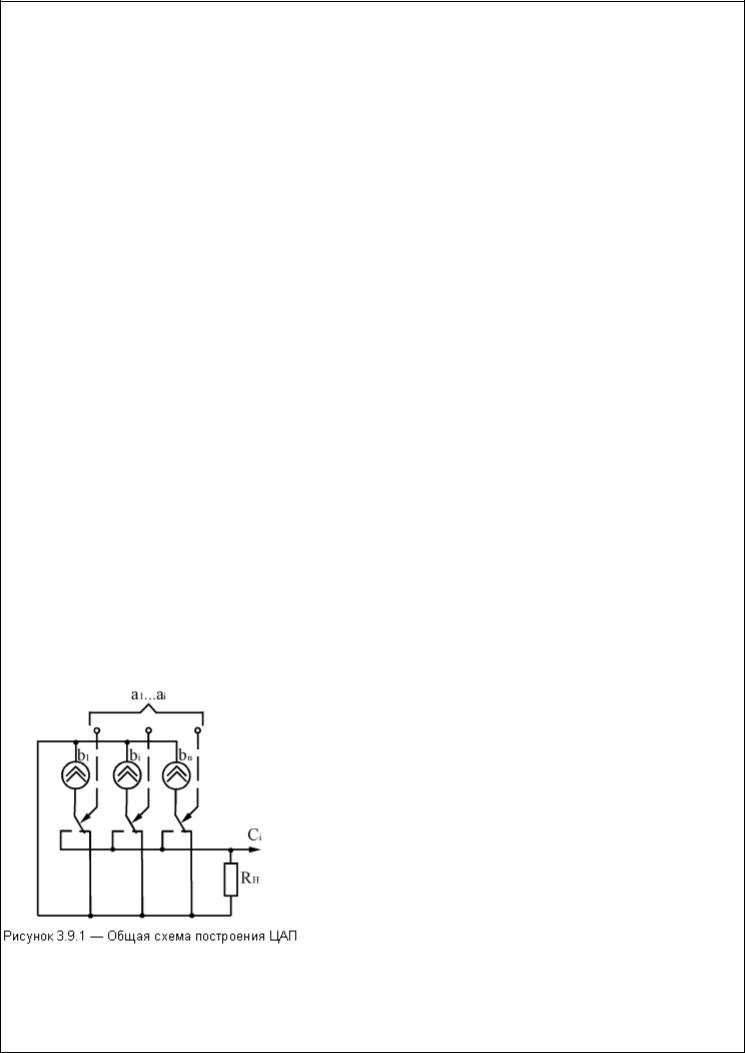

Цифро-аналоговые преобразователи (далее — ЦАП) предназначены для преобразования цифровых сигналов в аналоговые и служат для сопряжения цифровых устройств формирования и обработки сигналов с аналоговыми потребителями информации. Они широко используются для управления аналоговыми устройствами при помощи ЭВМ. Принцип работы заключается в следующем. Для формирования аналогового сигнала на выходе, однозначно соответствующего цифровому коду входного сигнала, аналоговые ключи аi подключают к выходу ЦАП необходимое количество источников опорных сигналов bi, величина которых пропорциональна весу соответствующего двоичного разряда (рисунок 3.9.1). Наибольшее распространение в настоящее время получили микроэлектронные ЦАП. Их в общем случае можно разделить на преобразователи с прямым и промежуточным преобразованием. Преобразователи с прямым преобразованием обычно параллельного типа. В состав простейшей схемы ЦАП обычно входят источники опорного напряжения, резистивные или активные делители, аналоговые ключи. В качестве делителей чаще всего применяются матрицы R – 2R. Суммирование токов, образованных подключением соответствующих источников, производится операционным усилителем (далее — ОУ). Учитывая, что входное сопротивление и коэффициент усиления ОУ очень велики, можно заключить, что ток в его входной цепи практически не протекает, а все составляющие токов, протекающих через открытые ключи схемы, замыкаются на землю через резистор RОС, уравновешиваясь током IОС, текущим в цепи ОС. ОУ выполняет операцию суммирования токов, которые определяются зна-

чениями сопротивлений в тех разрядах ЦАП, где аi=1

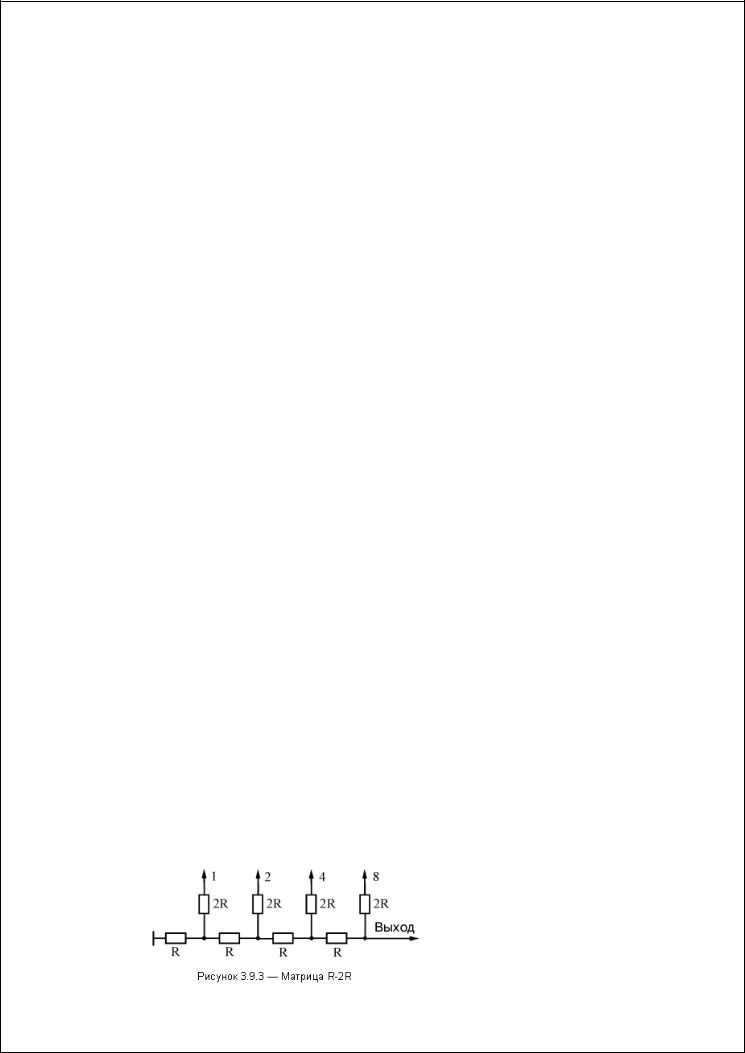

Подключая несколько резисторов к суммирующему входу операционного усилителя, на выходе можно получить напряжение, пропорциональное взвешенной сумме входных напряжений. Способ масштабирующих резисторов становится неудобным, если преобразованию подвергаются много разрядов. Матрица R-2R, показанная на рисунке 3.9.3, приводит к изящному решению этой задачи. Здесь требуется только 2 значения резисторов, по которым матрица R-2R- формирует токи с двоичным масштабированием. Особенностью такой матрицы являться то, что ее входное сопротивление при любом положении клю-

чей равно R, т.е. общий ток, втекающий в матрицу равен Распределение потенциалов в узлах матрицы не меняется при изменении положения ключей, поскольку входное сопротивление операционного усилителя фактически равно нулю, следовательно, потенциал на вхо-

47

де равен потенциалу «земли». Это обстоятельство приводит к последовательному уменьшению вдвое напряжения в узлах схемы по мере их удаления от источника опорного напряжения и такому же уменьшению токов, протекающих через ключи. Приведенная схема формирует напряжение от 0 В до 5 В с числом уровней дискретизации равным 16, при подаче на разряды матрицы входного двоичного 4-х разрядного числа с ТТЛ уровнями. Схемы ЦАП на основе резистивных матриц R-2R практичны, надежны, обладают высокой скоростью преобразования и легко реализуются в интегральном исполнении. Не требуется широкого диапазона номиналов и чрезвычайной точности при их подгонке.

Аналого-цифровые преобразователи

Аналого-цифровые преобразователи (АЦП) предназначены для преобразования аналоговых (непрерывных) сигналов в цифровую форму. Преобразование аналогового сигнала происходит в определенные моменты времени, которые называются точками отсчета. Количество отсчетов за единицу времени определяет частоту дискретизации (преобразования), которая, в свою очередь, определяется быстродействием и условиями использования АЦП. Интервал времени между отсчетами Тотс и частота дискретизации fпр связаны соотношением:

Тотс = 1/fпр.

В измерительной технике для преобразования медленно меняющихся процессов частота преобразования может быть установлена небольшой - единицы Герц и менее. В устройствах, где требуется преобразовывать сигналы в масштабе реального времени, частота преобразования выбирается из условия достижения максимальной точности восстановления цифрового сигнала в аналоговую форму. Например, преобразование речевого сигнала в дискретную форму. При этом частота дискретизации определяется как fпр = 2Fмах, где Fмах - максимальная частота речевого сигнала.

Для обеспечения преобразования без искажений требуется выполнение условия:

tпр Тотс,

где tпр - время преобразования АЦП одного отсчета.

Основные параметры АЦП определяются также как и параметры ЦАП.

По принципу дискретизации и структуре построения АЦП делятся на две группы: 1- группа АЦП с применением ЦАП и 2-группа АЦП без ЦАП.

К первой группе относятся:

- АЦП последовательного счета (развѐртывающего типа); - АЦП последовательного приближения (поразрядного уравновешивания); - следящий АЦП.

К второй группе относятся:

-АЦП прямого преобразования;

-АЦП двойного интегрирования;

-АЦП с применением генератора, управляемого напряжением (ГУН).

Каждый тип АЦП имеет свои достоинства и недостатки. На практике встречаются все выше перечисленные типы АЦП.

48

Аналого-цифровые преобразователи (далее — АЦП) представляют собой устройства, которые преобразуют входные аналоговые сигналы в соответствующие им цифровые сигналы, пригодные для работы с ЭВМ и другими цифровыми устройствами.

Параллельные АЦП. Данный тип АЦП реализует метод непосредственного считывания и является на сегодняшний день самым быстродействующим. В параллельных АЦП входной сигнал одновременно квантуется с помощью набора компараторов, включенных параллельно эталонному источнику сигнала. Пороговые уровни компараторов установлены с помощью резистивного делителя в соответствии с используемой шкалой квантования. При подаче на такой набор компараторов входного сигнала на выходах последних будет иметь место проквантованный сигнал, представленный в параллельном коде, который с помощью кодирующей логики преобразуется в двоичный. Схема содержит m резистивных делителей эталонного напряжения и столько же компараторов. Число m определяется количеством дискретных значений преобразуемого напряжения в полном диапазоне преобразования.

Каждое из опорных напряжений подается на первые входы компараторов, на вторые входы которых подается входное напряжение. При подаче Uвх переключаются те компараторы, где Uвх > Uэi. Выходные сигналы этих компараторов принимают единичное значение, запоминаясь в регистре. Выходы регистра соединяются с шифратором, который преобразует этот m разрядный параллельный единичный код в n разрядный параллельный двоичный код.

Последовательные АЦП делятся на АЦП счета и интегрирующие АЦП.

АЦП счета: Схема содержит два компаратора К1 и К2, первый из которых имеет опорное напряжениеUоп. а второй Uвх.

Интегрирующий АЦП. Полный цикл работы схемы состоит из двух тактов. В первом с помощью аналогового интегратора происходит интегрирование входного напряжения за фиксированный интервал времени. В результате этой операции на выходе интегратора формируется напряжение Uвых. Во втором такте происходит разряд конденсатора от источника опорного напряжения Uоп. до нуля.

АЦП последовательного приближения.

Принцип состоит в формировании цифровым способом эталонного напряжения Uэ путем последовательного приближения его к входному напряжению Uвх.

49