Шпоры по ЭСА

.pdf

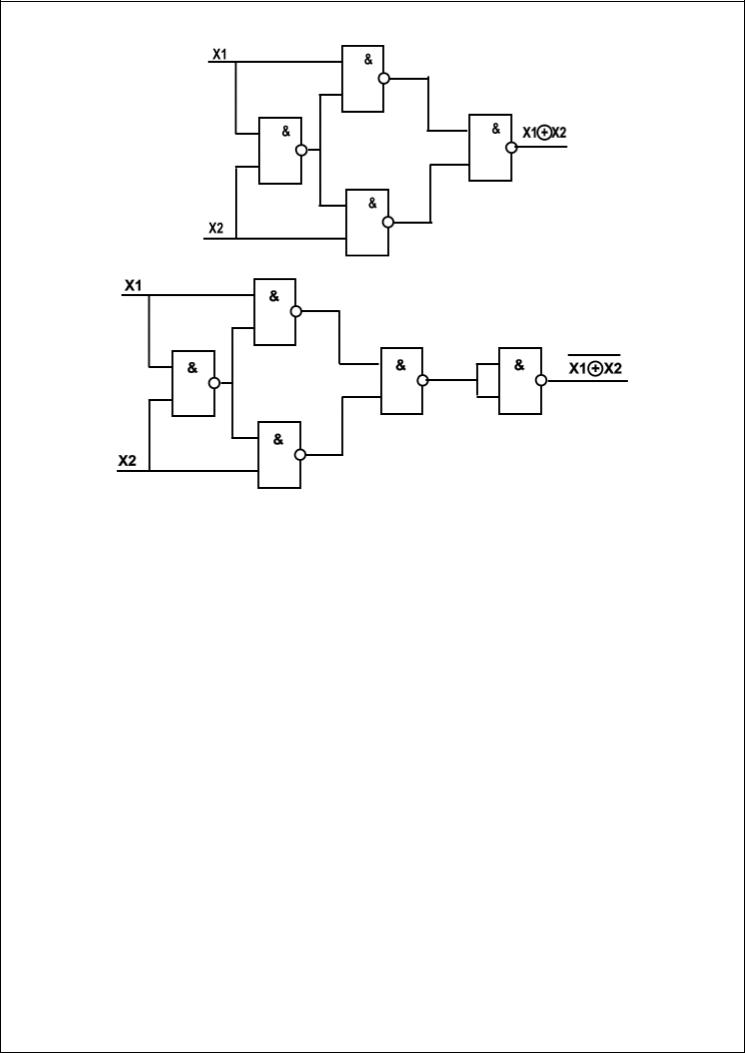

Элемент «исключающее ИЛИ»

Элемент «исключающее ИЛИ – НЕ»

31

2.20 Мультиплексоры

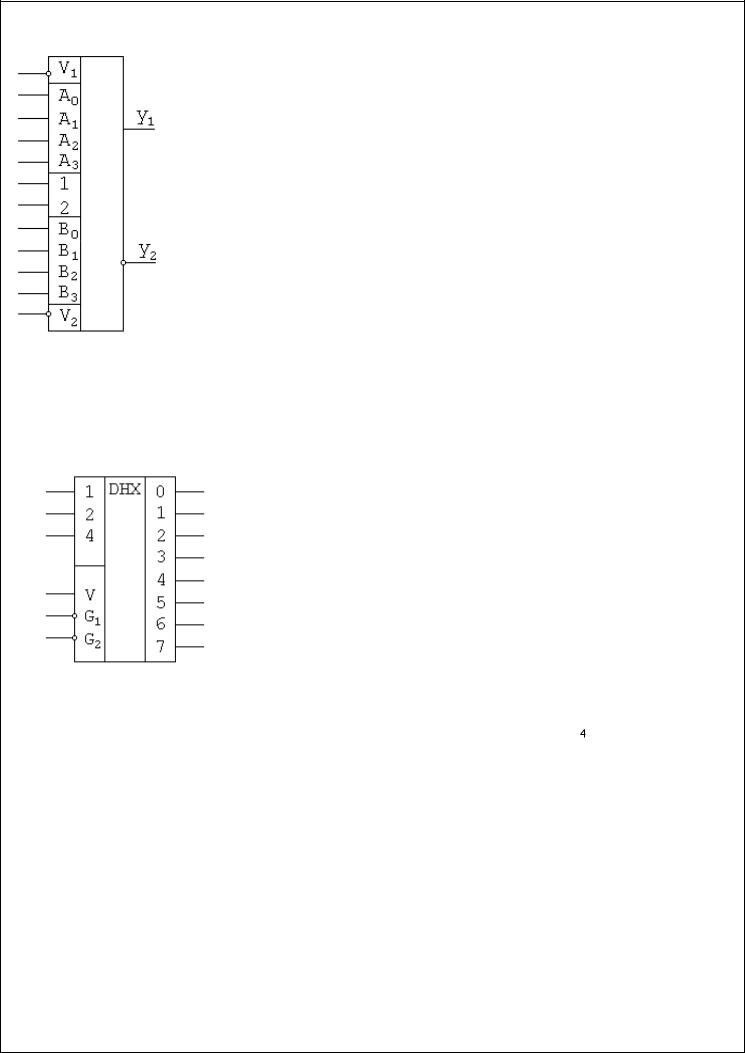

Рисунок 1 - Условное обозначение сдвоенного четырехканального селектора-мультиплексора 155КП12

Мультиплексором называется схема, имеющая m+2m входов и один выход, где m - число адресных входов, а 2m - число информационных входов мультиплексора. Адреса представляются в двоичном коде и им присваивается номер j. Каждому адресу с номером j соответствует свой информационный вход Аj, сигнал которого при данном адресе походит на выход.

Основным назначением мультиплексора является коммутация 2m входных сигналов на один выход.

Мультиплексоры могут использоваться в качестве устройства для выбора соответствующего канала.

На рис.1 приведено условное обозначение сдвоенного четырехканального селектора-мультиплексора 155КП12.

Демультиплексоры

Демультиплексор (распределитель) является схемой, выполняющей функцию, противоположную мультиплексору. У демультиплексора один вход и несколько выходов.

Рисунок 2 - Условное обозначение

|

|

A0 |

MIX |

|

|

|

|

A1 |

|

|

|

|

|

A2 |

|

|

|

|

|

A3 |

|

|

|

Мультиплексор |

|

A |

|

|

|

|

A5 |

|

|

Y |

|

|

|

|

|

||

Amинформационные входы. |

|

A6 |

|

|

|

amадресные входы. |

A7 |

|

|

|

|

Число информационных входов мультиплексора |

|

|

|

|

|

|

a0 |

|

|

|

|

|

|

|

|

||

равно числу комбинаций адресных входов. |

|

a1 |

|

|

|

|

a3 |

|

|

|

|

|

|

|

|

|

|

(Мультиплексор из восьми в один) |

|

|

|

|

|

|

|

|

|

||

Принцип действия аналогичен принципу кругового переключателя: |

|

|

|

|

|

В каждый момент времени к выходу мультиплексора подсоединѐн только один вход , причѐм тот, индекс которого в двоичном коде набран на адресных входах.

32

2.21 Шифраторы

Шифраторы выполняют функцию, обратную дешифраторам, преобразуя код в двоичный код.

Шифраторы приоритета, если «1» появляется не на одном, а на нескольких входах, то на выходе появляется код старшего числа.

Рисунок 1 - Условное обозначение шифратора

Дешифраторы

Полным дешифратором называется комбинационная схема, имеющая n входов и 2n выходов. Причем каждой комбинации значений входных сигналов соответствует сигнал равный логической 1 только на одном выходе. Таблица 1 - таблица истинности дешифратора на 8 кодовых комбинаций. Его условное обозначение смотрите на рис.2 Таблица 1 Таблица истинности дешифратора

для преобразования двоичного кода в другой

DC 0

1

2

a0 3

a1 4

a2 5

a3 6

7

8

9

Рисунок 2

Дешифраторы могут быть неполными, реализующими m<2n комбинаций. Такие дешифраторы используются, например, для преобразования двоичного кода в десятичный. Например 155ИД1 или 564ИД1, то есть дешифратор 4 10.

Дешифраторы предназначены

0 C

1

2

3a0

4a1

5a2

6a3

8

9

Дешифратор |

Шифратор |

33

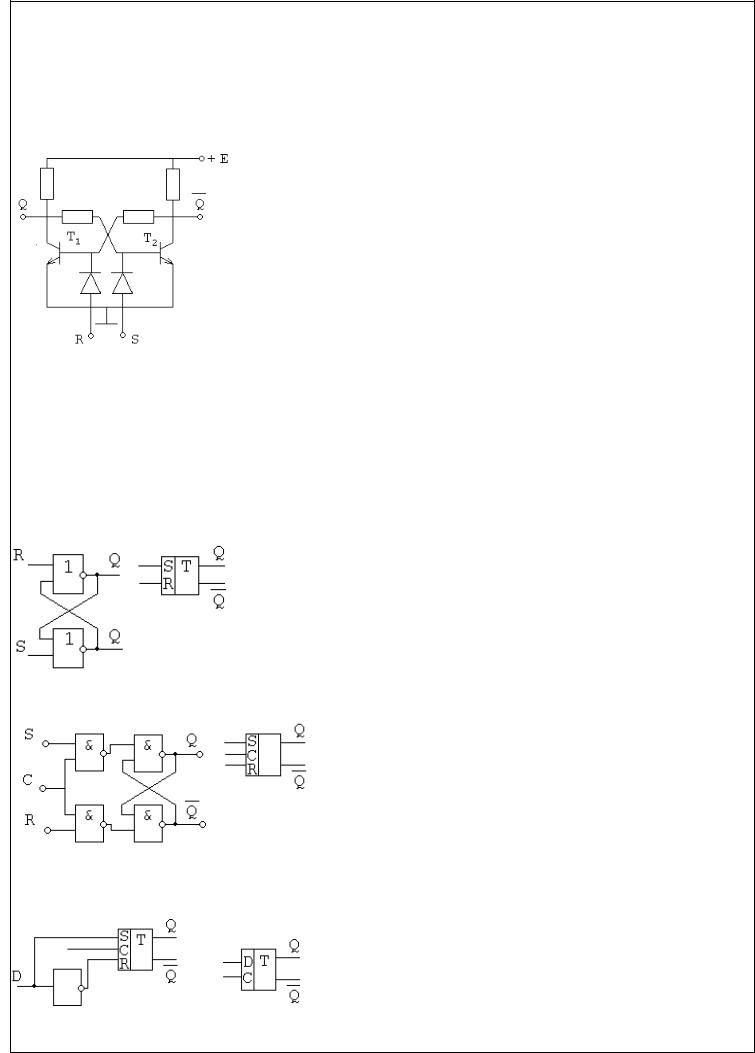

2.22 Триггеры

Триггер - электронное устройство, с помощью которого можно записывать, хранить и считывать двоичную информацию. Он имеет два устойчивых состояния равновесия, одно из которых принимают за логическую 1, а другое за 0.

Триггер – устройство, имеющее 2 устойчивых состояния, в которых он может находиться сколь угодно долго до прихода управляющего воздействия.

Рисунок 1 - Принципиальная схема триггера В схемном отношении триггер представляет собой два про-

стейших усилительных каскада с взаимно обратными положительными связями, наличие которых приводит к тому, что в устойчивом состоянии один транзистор усилителя открыт, а другой - закрыт. Сигналя, снимаемые с выходов триггера имеют два уровня постоянного напряжения. Так коду 1 соответствует состояние триггера, когда транзистор VT1 закрыт и на его коллекторе высокое напряжение. Ввод в триггер дво-

ичных цифр производится по цепям установки единицы S (set), и установки 0 - R (reset). С помощью таких цепей триггер переводится из одного состояния в другое. Положительные сигналы S или R подаются на базы транзисторов VT1 и VT2.

Если триггер находится в состоянии 0, то при подаче сигнала S на базу VT2 последний открывается, потенциал на его коллекторе понижается, что вызывает запирание VT1. По окончании переходных процессов триггер оказывается в состоянии 1. В этом состоянии он будет находиться до тех пор, пока не поступит сигнал R.

Триггер может быть выполнен на элементах ИЛИ-НЕ (см. рис.2).

Рисунок 2 - Схема триггера на элементах ИЛИ-НЕ и его условное обозначение

Такой триггер называется асинхронным RS-триггером. При R=1 и S=0 триггер устанавливается в нулевое состояние (Q=0), при R=0 и S=1 - в единичное состояние (Q=1); при R=S=0 триггер сохраняет состояние. Комбинация R=S=1 RSтриггера запрещена.

Синхронный RS-триггер

Рисунок 3 - Схема синхронного RS-триггера и его условное обозначение.

Такие RS-триггеры имеют кроме информационных входов R и S вход синхронизации C. Входная информация заносится в синхронный RSтриггер в момент поступления импульса синхронизации. При С=0 триггер будет находится в режиме

хранения независимо от сигналов на R и S входах. D-триггер

Рисунок 4 - D-триггер и его условное обозначение

D-триггер соответствует RS-триггеру, работающему только в режимах установки, то есть либо с комбинацией сигналов R=1 и S=0, либо с комбинациями сиг-

налов R=0 и S=1. Для организации хранения информации используется вход С.

34

JK-триггер

Рисунок 5 - Схема JK-триггера и его условное обозначение

JK-триггера наиболее универсален. Вход J и К соответствует S и R RS-триггера. Отличие состоит в том, что в JK-триггере нет запрещенного состояния входов. При состоянии на входах J=1, К=0 приход тактового импульса пере-

ключает триггер в состояние 1. При состоянии на входах J= 0, К=1 приход тактового импульса переключает триггер в состояние 0. Состояние на входах J= 0, К=0 соответствует режиму хранения информации.

Введение дополнительных обратных связей позволяет исключить запрещенное состояние входов. При состоянии входов J=K=1 триггер работает в переключающем режиме.

Двухтактные триггеры

Рисунок 6 - Схема двухтактного триггера и его условное обозначение Двухтактный триггер изменяет свое состояние

только после окончания действия импульса синхронизации.

С приходом тактового импульса по его фронту первый триггер переключается в состояние, сформированное соответствующим состоянием входа. В момент действия тактового импульса на вхо-

де С второго триггера сохраняется состояние 0. По спаду тактового импульса на входе С второго триггера появляется логическая 1. Информация, записанная на первом такте в первом триггере переписывается на выход второго триггера.

35

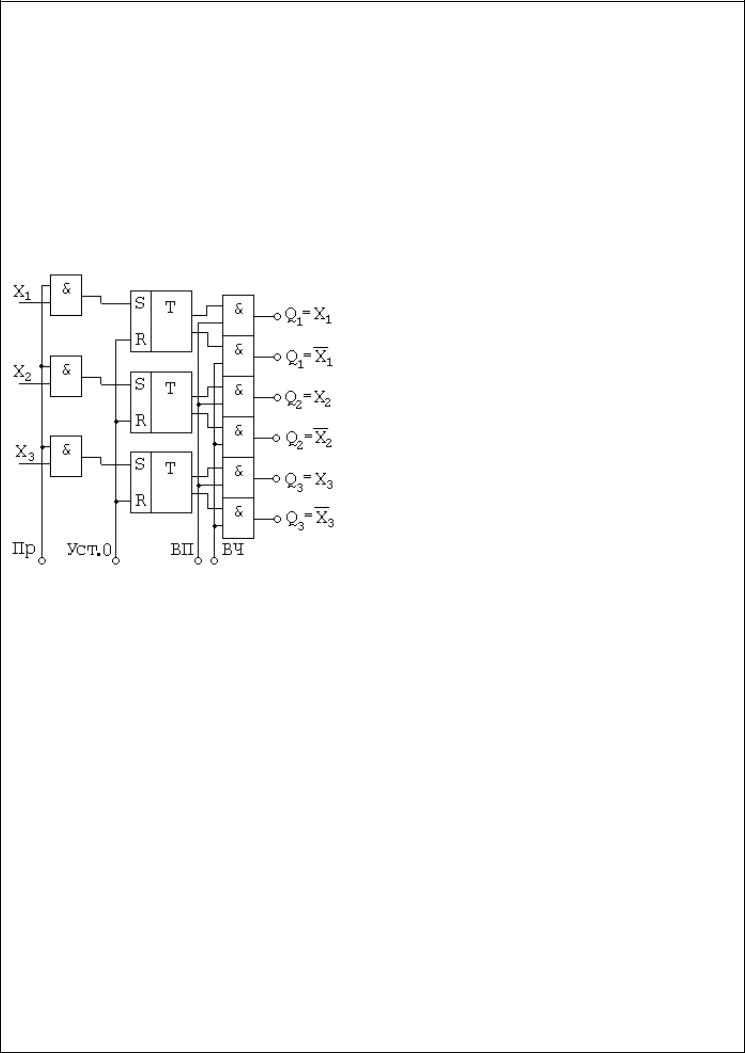

2.23 Регистры

Регистр - функциональное устройство, предназначенное для запоминания n-разрядного слова, а также для выполнения определенных микроопераций над этим словом. Он представляет собой упорядоченную совокупность триггеров со схемой управления входными и выходными сигналами. Разрядность регистра соответствует количеству используемых в нем триггеров.

По виду выполняемых операций над словами различают регистры для приема, передачи и сдвига информации.

По способу приема и передачи информации различают последовательные, параллельные и последовательнопараллельные регистры.

По количеству тактов управления различают одно-, двух- и многотактные регистры.

Регистры приема и передачи информации

Рисунок 1 - Схема регистра приема и передачи информации

В этой схеме используются RS-триггеры, группа входных и выходных U-схем. Информация в регистр заносится по шинам x1, х2, х3 только в том случае, когда на шину Пр подан управляющий сигнал приема информации. Записанный в регистр код слова будет храниться в нем до тех пор, пока не будет подан сигнал установки регистра в состояние 0. Прямой код хранимого слова будет выдан при наличии на шине ВП управляющего сигнала ―Выдача прямого кода‖. Сигнал выдачи инверсного кода ВИ позволяет через группу схем И получить инверсное значение кода, хранимого в регистре.

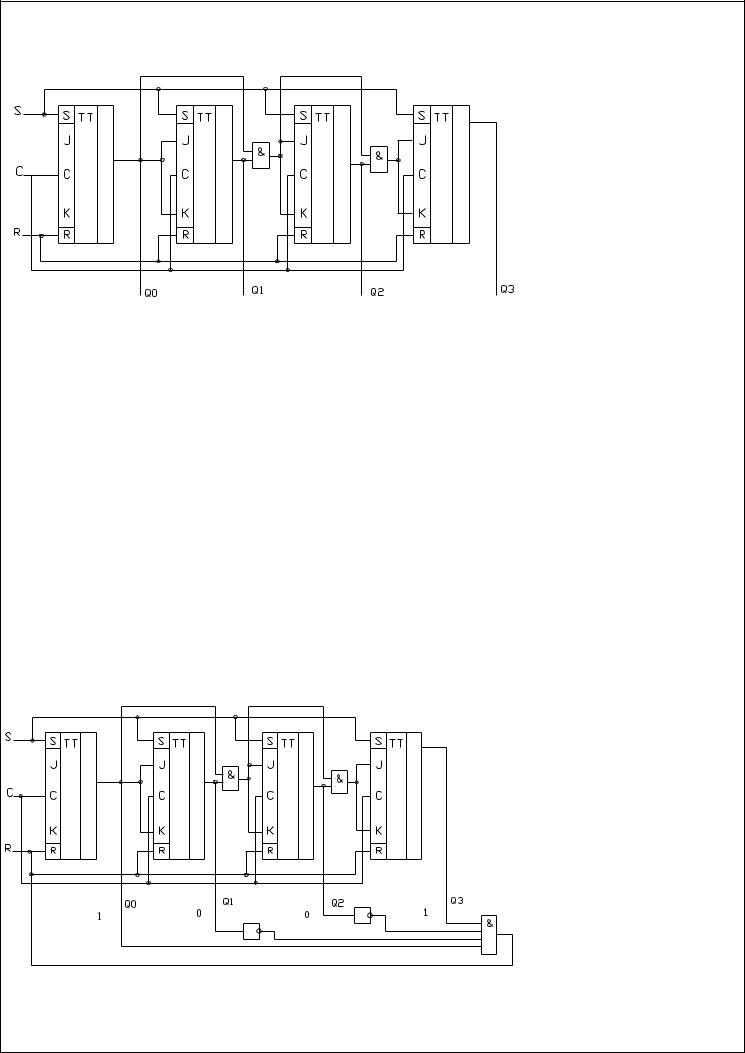

Сдвиговые регистры

Сдвиговые регистры предназначены для выполнения операции сдвига слова информации, то есть для перемещения всех цифр слова в направлении от старших к младшим разрядам (сдвиг влево) или от младших к старшим разрядам (сдвиг вправо). Сдвиг кода влево на один разряд будет соответствовать умножению кода числа на основание системы счисления, а сдвиг вправо - делению. В регистрах, как правило, сдвиг числа на k разрядов осуществляется за k тактов.

С приходом первого тактового импульса старший разряд вводимого числа записывается в первый триггер. После прихода второго тактового импульса, старший разряд вводимого числа, который находится на входе второго триггера, переписывается на его выход. На выходе первого триггера появляется следующий разряд двоичного числа. Третий импульс переписывает старший разряд на выход второго, т.е. осуществляется сдвиг записанной информации на один разряд вправо. Аналогичным образом записываются следующие разряды и естественно, что 4х-разрядное число можно записать с помощью 4х тактовых импульсов. Пятый тактовый импульс, осуществляя сдвиг информации вправо, приводит к потере информации о старшем разряде. Если необходимо сохранить записанное число при сдвиге информации применяют кольцевые регистры.

36

Однако данная схема не применяется, т.к. не происходит ввод информации. Для реализации |

||||

регистров с циклическим переносом (кольцевых) используют универсальные регистры |

||||

сдвига, которые имеют возможность как параллельного, так и последовательного ввода ин- |

||||

формации. |

|

|

|

|

Рис. 2. Схема реализации кольце- |

||||

вого регистра |

|

|

||

Сдвигающий регистр можно ис- |

||||

пользовать не только для сдвига |

||||

кода, но и для преобразования па- |

||||

раллельного кода, принятого в ре- |

||||

гистр, в последовательный или на- |

||||

оборот. С точки зрения уменьше- |

||||

ния количества связей и оборудо- |

||||

вания сдвиговые регистры целесообразно строить на D-триггерах. Установка этого регистра |

||||

в состояние 0 выполняется отрицательным импульсом, подаваемым на вход R. Параллель- |

||||

ный код поступает на входы x. Запись параллельного кода осуществляется положительным |

||||

импульсом, подаваемым на вход C2. Последовательный код поступает на вход D1. |

|

|

||

Рисунок 3 - Схема сдвигающего регистра |

|

|

|

|

Слово, состоящее из 8 бит, называется байтом. |

|

|

|

|

Рис. 5 - Параллельный регистр |

|

|

|

|

При поступлении сигнала «за- |

||||

пись», двоичное слово, подан- |

||||

ное |

на |

информационный |

вход |

|

регистра, записывается в ре- |

||||

гистр, причѐм запись каждого |

||||

разряда |

осуществляется |

|

одно- |

|

временно или параллельно. От- |

||||

сюда и название регистра. |

|

|||

Рис. 6 – Последовательный ре- |

||||

гистр |

|

|

|

|

Изображенный регистр называют |

||||

ещѐ |

последовательным |

регист- |

||

ром, т.к. информация в него вво- |

||||

дится посредством входа Т по- |

||||

следовательно, в течение 4х так- |

||||

товых импульсов. |

|

|

||

|

|

|

|

37 |

2.24 Счетчики

Счетчик представляет собой устройство, предназначенное для подсчета числа сигналов, поступающих на его вход, и фиксации этого числа в виде кода, хранящегося в триггерах. По целевому назначению счетчики подразделяют на простые (суммирующие и вычитающие) и реверсивные. Суммирующий счетчик предназначен для работы в прямом направлении, то есть для сложения. С поддачей на вход очередного единичного сигнала показание счетчика увеличивается на единицу. Каждый сигнал, поступающий на вход вычитающего счетчика, уменьшает его показания на единицу. Реверсивные счетчики могут работать в обоих режимах. По способу организации счета счетчики подразделяют на асинхронные и синхронные. По способу организации цепей переноса между разрядами различают счетчики с последовательным, параллельным и частично-параллельным переносом. Основными характеристиками счетчика являются модуль счета, разрешающая способность, время регистрации и емкость. Модуль счета характеризует число устойчивых состояний счетчика, то есть предельное число входных сигналов, которое может сосчитать счетчик. Разрешающая способность - минимально допустимый период следования входных сигналов, при котором обеспечивается надежная работа счетчика. Время регистрации - интервал времени между моментами насыщения входного сигнала и окончания самого длинного переходного процесса в счетчике. Емкость счетчика - максимальное число единичных сигналов, которое может быть зарегистрировано в счетчике.

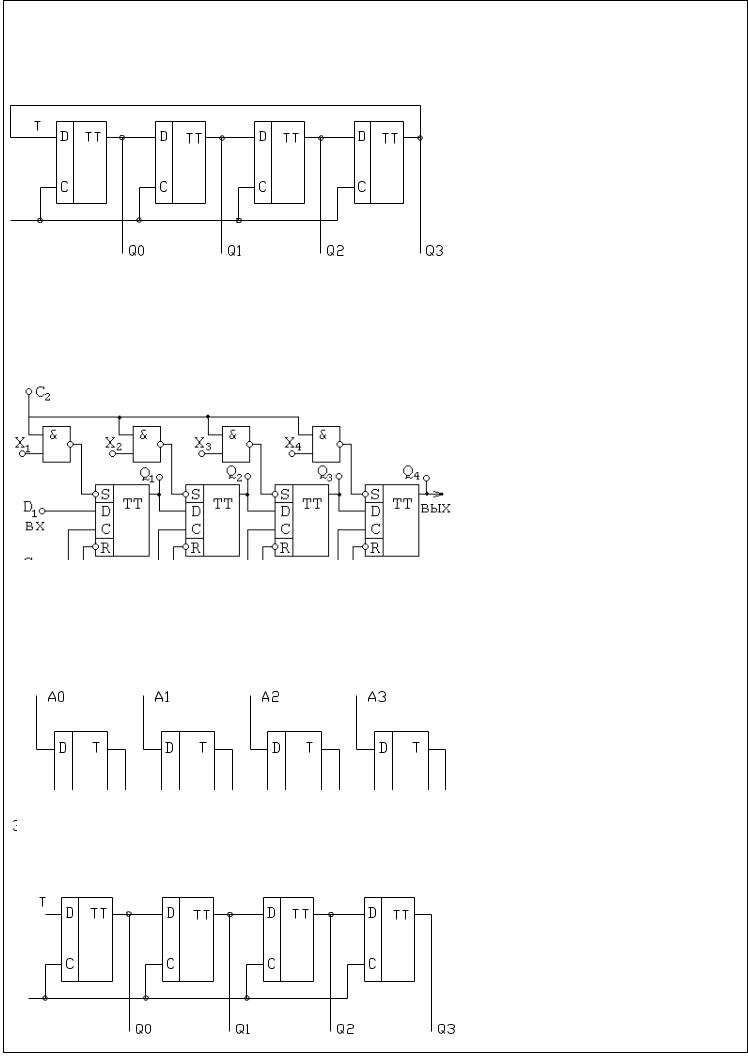

Счетчики с непосредственными связями с последовательным переносом (асинхронные)

В этих счетчиках каждый последующий триггер (i+1)-го разряда запускается от информационных выходов предыдущего триггера i-го разряда, а счетный сигнал поступает на вход триггера первого разряда.

Четырехразрядный асинхронный двоичный счѐтчик по модулю 16

Счѐтчики представляют собой цифровое устройство, которое ставит в соответствие числу импульсов на входе определѐнный двоичный код на выходе

|

z |

Q0 |

Q1 |

Q2 |

Q3 |

|

0 |

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

0 |

1 |

|

2 |

0 |

0 |

1 |

0 |

|

3 |

0 |

0 |

1 |

1 |

|

4 |

0 |

1 |

0 |

0 |

|

5 |

0 |

1 |

0 |

1 |

Схема реализации двоичного счѐтчика по модулю 16 Двух- |

6 |

0 |

1 |

1 |

0 |

|

|

|

|

|

|

тактного |

7 |

0 |

1 |

1 |

1 |

Любой двоичный счѐтчик может быть построен на 2х-тактных .. ..... ..... .... .... |

|||||

триггерах, работающих в счетном режиме. |

16 |

0 |

0 |

0 |

0 |

|

|||||

Таблица 1.Таблица истинности двоичного счѐтчика по модулю 16

38

Данный двоичный счѐтчик кроме тактового входа C имеет входы асинхронного сброса и установки R и S. Асинхронными они называются потому, что не зависят от тактового входа.

Из таблицы соответственно видно две особенности:

1)переключение более старшего разряда в 1 происходит после переключения более младшего разряда из 1 в 0. На этой особенности построен принцип действия асинхронного счѐтчика.

2)переключение более старшего разряда из 0 в 1 происходит после того, когда все младшие

разряды будут находится в состояние 1.

На второй особенности основан принцип действия синхронного сдвига.

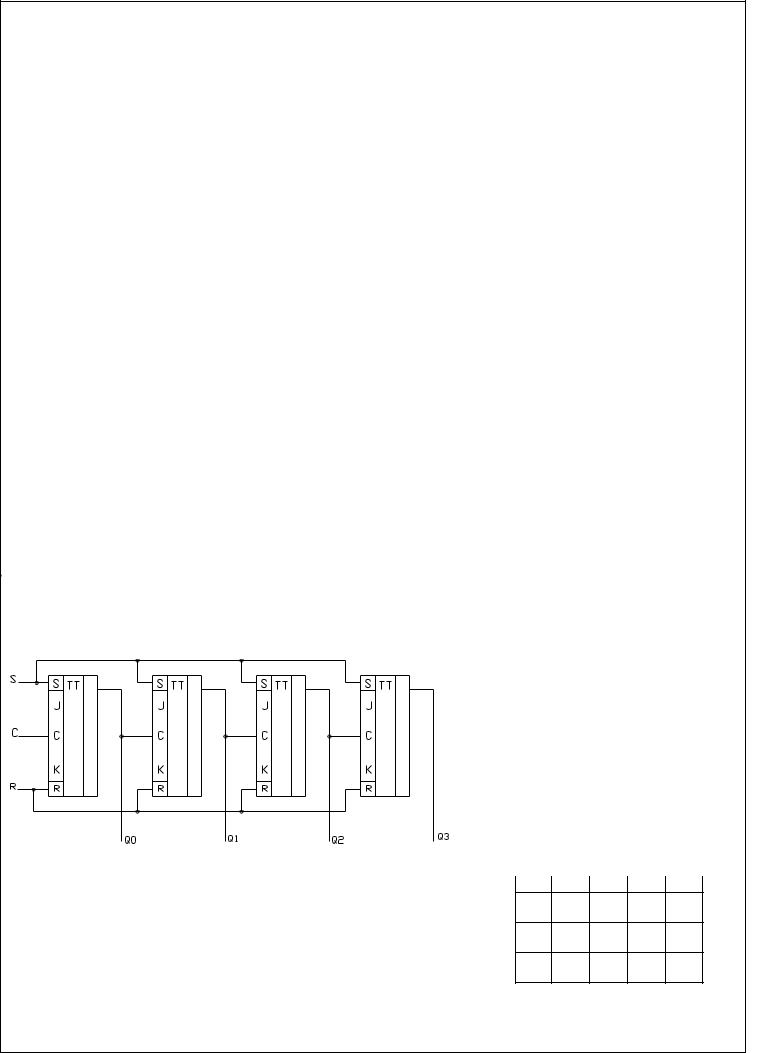

Временные диаграммы работы двухтактного двоичного счѐтчика по модулю 16

Предполагается, что предварительно счѐтчик очищен сигналом, поданным на вход сброса, т.е. выходы всех триггеров находятся в нулевом состоянии. По приходу первого тактового импульса, который поступает на тактовый вход первого триггера, первый триггер изменяет своѐ состояние на противоположное. Состояние остальных триггеров не изменяется. Приход второго тактового импульса переключает первый триггер в 0, сигнал с выхода первого триггера является тактовым для второго триггера. По приходу третьего импульса первый триггер переключается, остальные не изменяются и т.д.

Такой счѐтчик называется асинхронным потому, что тактовый импульс поступает на вход только одного триггера, а остальные триггеры переключаются по сигналам с выхода предыдущего. Причем каждый триггер вносит задержку в переключение. В итоге получаем, что с приходом одного импульса триггеры переключаются не одновременно или асинхронно. В этом состоит главный недостаток асинхронных счѐтчиков, т.к. при большой частоте тактовых импульсов возникает возможность неверной информации на выходе. От этого недостатка свободен синхронный счѐтчик. Недостаток асинхронного счетчика заключается в том, что он имеет зависимость длительности переходного процесса, определяющего время регистрации, от его разрядности. С ростом разрядности счетчика понижается предельная частота его работы. Это связано с тем, что возрастает задержка поступления сигнала на вход с некоторого i-го разряда относительно времени поступления входного сигнала на вход с младшего разряда счетчика. Из временной диаграммы видно, что такая задержка может привести к искажению информации в счетчике (t=9).

Счетчики с параллельным переносом

Для повышения быстродействия счетчики выполняются с параллельным переносом. Из схем видно, что с возрастанием порядкового номера триггера увеличивается число входов в элементах U, поэтому разрядность счетчика с параллельным переносом невелика и равна обычно четырем. Поэтому при большем числе разрядов происходит последовательное соединение (наращивание) параллельных счетчиков. Подобным способом реализуется счетчик с частичным параллельным переносом.

39

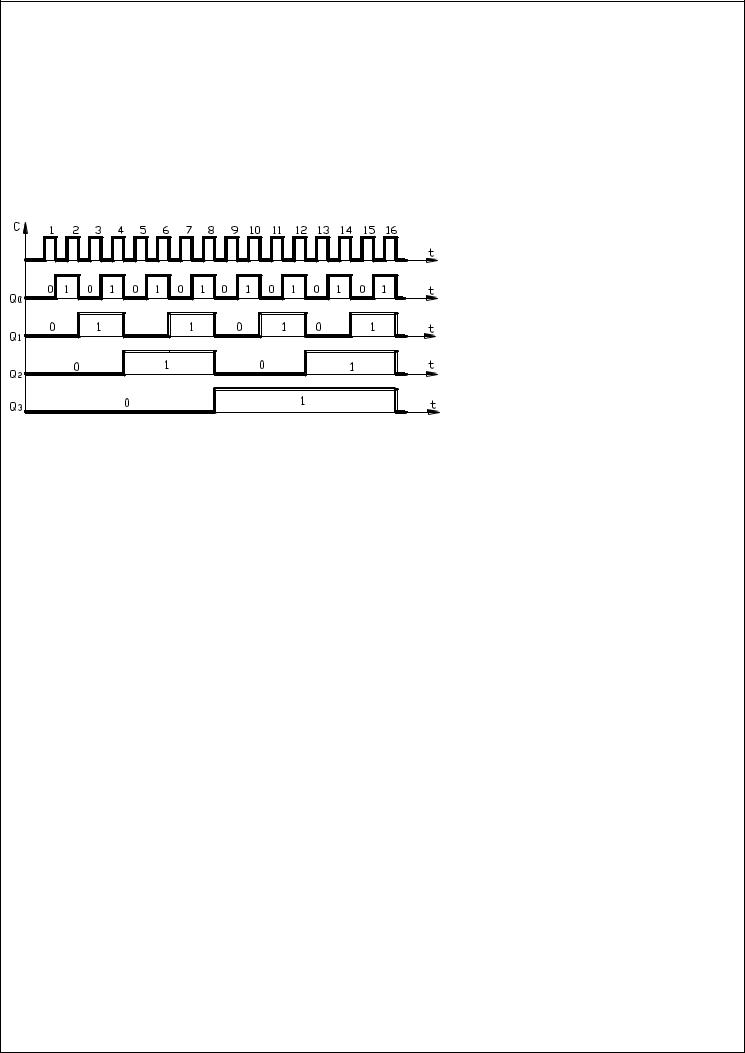

Синхронный счѐтчик |

|

|

|

|

|

Счѐтчик называется синхронным, т.к. тактовые импульсы подаются на все триггеры одно- |

|||||

временно и соответствен- |

|||||

но триггеры переключа- |

|||||

ются одновременно (син- |

|||||

хронно). Временная диа- |

|||||

грамма работы та же са- |

|||||

мая. |

|

|

|

|

|

Принцип работы: Приход |

|||||

первого |

тактового |

им- |

|||

пульса |

|

переключает |

пер- |

||

вый триггер в состояние 1. |

|||||

Этот же тактовый им- |

|||||

пульс |

поступает |

на |

вход |

||

остальных триггеров, но остальные триггеры не меняют своѐ состояние, т.к. на входах J, K |

|||||

этих триггеров до прихода импульса и в момент его действия сохранялось состояние 0. |

|

||||

Особенность 2х-тактного триггера : после спада первого импульса на выходе первого триг- |

|||||

гера появляется 1, которая подаѐтся на вход JK второго триггера, переводя его в переклю- |

|||||

чающий режим; следовательно приход второго тактового импульса изменит состояние не |

|||||

только первого триггера, но и второго. По спаду второго импульса на выходе первого триг- |

|||||

гера будет 0, на выходе второго триггера – 1. |

|

|

|

|

|

К приходу третьего тактового импульса на входах J и K второго триггера имеется состояние |

|||||

0, что соответствует режиму хранения информации. Приход третьего импульса не изменяет |

|||||

его состояние и на выходе второго останется 1. По третьему импульсу переключится пер- |

|||||

вый триггер в состояние 1 и после его спада на выходе первого и второго триггера имеется |

|||||

состояние 1. Эти две единицы, поданные на первый элемент «И», дают возможность пере- |

|||||

вести третий триггер в переключающий режим работы. |

|

|

|

|

|

Двоично-десятичный счѐтчик или счѐтчик по модулю десять |

|

|

|

|

|

Такой счѐтчик считает только 10 импульсов, т.е. после появление на выходе кода 9, сле- |

|||||

дующий импульс переводит его в исходное состояние. Код девятки –1001. Для счѐтчика ис- |

|||||

пользуется схема №1 |

|

||||

Но еѐ необходимо дорабо- |

|||||

тать: |

|

|

|

|

|

Такой |

|

способ |

наиболее |

||

простой, но он не приме- |

|||||

няется , т.к. время суще- |

|||||

ствования кода «9» очень |

|||||

мало и сразу после его по- |

|||||

явления |

осуществляется |

||||

сбрасывание, в то время |

|||||

когда |

его |

другие |

коды |

||

существуют |

в |

течении |

|||

тактового импульса . Дво- |

|||||

ично-десятичные счѐтчики применяются для счѐта ими в двоично-десятичном коде. |

|

||||

|

|

|

|

|

40 |