- •2.4.1. Классификация диодов.

- •Полевые транзисторы.

- •Тиристор. Типы, назначение, хар-ки.

- •Интегральные микросхемы. Виды, технологии.

- •Компенсационные стабилизаторы

- •Стабилизаторы тока

- •Импульсные стабилизаторы напряжения

- •Демультиплексоры

- •Дешифраторы

- •Триггеры

- •Регистры

- •Оперативные и постоянные запоминающие устройства

Стабилизаторы тока

В компенсационных стабилизаторах тока последовательно с нагрузкой включается эталон- ный резистор Rэт, напряжение на котором стабилизируется с помощью обычного стабилиза- тора напряжения. Таким образом, при изменении нагрузки Rн ток, протекающий через нее, останется неизменным.

Рис.1 Вариант схемы компенсационного стабилизато- ра тока.

Сигнал рассогласования UR Д.Т.-UОП усиливается с по- мощью усилителя постоянного тока на транзисторе VT2, и воздействует на регулирующий элемент (транзи- стор VT1).

18

Импульсные стабилизаторы напряжения

Применение импульсного режима работы регули- рующего элемента стабилизатора позволяет повысить

КПД до 80и выше.

Рис. Структурная схема импульсного стаби-

лизатора напряжения последовательного ти-

па.

В такой схеме нагрузка последовательно через сгла-

живающий фильтр Ф и ключевой регулирующий эле-

мент РЭ подключена к источнику входного напряже-

ния. Выходное напряжение сравнивается с эталонным опорным напряжением Uоп. Разност-

ный сигнал рассогласования Up, формируемый схемой сравнения СС, воздействует на схе-

му управления СУ, которая вырабатывает импульсы, управляющие временами размыкания

и замыкания ключевого регулирующего элемента.

В результате ко входу сглаживающего фильтра Ф

будет приложено импульсное напряжение Uф (см.

рис. 2.).

Среднее значение этого напряжения Uфо зависит

от соотношения времен замкнутого tз и разомкну-

того tp состояния ключа РЭ и определяется форму-

лой: Uфо=Uвх(tз/(tз+tp)=Uвхtз/Т=Uвхtзf=Uвх/Q, где

Т=tз+tp-период; f-частота переключения ключевого

элемента; Q=T/tр-скважность последовательности

импульсов.

Изменение параметров tз и f можно рассматривать как модуляцию входного напряжения

ключевым элементом РЭ.

Наибольшее распространение получили стабилизаторы с широтно-импульсной модуля-

цией, когда изменяется длительность управляющих импульсов tз (время замкнутого состоя-

ния ключевого элемента РЭ), а частота f их следования остается неизменной.

В качестве схемы управления СУ в таких стабилизаторах может использоваться генера-

тор импульсов ГИ, вырабатывающих прямоугольные импуль-

сы с постоянной f. Длительность импульсов определяется ве-

личиной сигнала рассогласования, поступающего с выхода

схемы сравнения СС.

Возможно построение стабилизатора с ШИМ на основе сле- дующей структурной схемы на рис.3. РЭ - регулирующий элемент;Ф – фильтр;Н-нагрузка;ГЛИН - генератор линейно

изменяющегося напряжения;КН - компаратор напряжения

Принцип работы схемы можно проиллюстрировать с помощью временных диаграмм (см.

рис.4.). По способу включения регулирующего транзистора и

дросселя, входящего в состав фильтра Ф, ИСН можно под-

разделить на последовательные и параллельные. Рассмотрим

варианты соединения элементов силовой части ИСН.

Если источник постоянного тока подключить к нагрузке с помощью периодически замыкаемого и размыкаемого клю- ча, то среднее значение напряжения на нагрузке:

19

Uн=(1/T)tн

0

i(t)Rнdt где tн

длительность импульса замкнутого состояния ключа; T-период

коммутации;

i(t)-

текущее

значение

тока.

Если

параллельно

нагрузке

подключить

конденса-

тор достаточно большой емкости, то переменная составляющая тока контура будет замы-

каться через него, а пульсации напряжения на нагрузке будут незначительны. Это условие

может выполняться при трех вариантах соединения силовых

элементов.

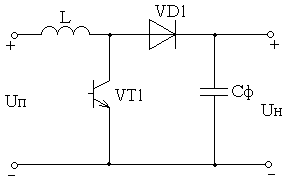

а) б) в) Рис.5.

Поясним особенности схем:

Схема с последовательным включением транзистора и дросселя (рис.5.(а)) позволяет по- лучить на нагрузке напряжение, равное или меньшее напряжения питания.

Схема с последовательным включением транзистора и параллельным включением дрос- селя (рис.5.(б)) позволяет получить напряжение, большее или меньшее напряжения пита- ния, при этом напряжение на выходе стабилизатора инвертируется.

Схема с параллельным включением транзистора и последовательным включением дрос- селя (рис.5.(в)) позволяет получить напряжение, равное или большее напряжения питания. Необходимо отметить, что известны различные варианты построения силовых цепей, одна- ко все они могут быть сведены к трем, рассмотренным выше.

Процессы, характеризующие работу импульсного стабилизатора без учета особенностей схемы форми- рования управляющих импульсов, рассмотрим на примере ИСН, построенного по схеме рис.5.(а). Вре- менные диаграммы работы такой схемы изображены на рис.6.

Рис.6 .

Предположим, что в момент времени t=0 регулирующий транзистор открыт и ток через катушку индуктивности нарастает по линейному закону: iL=IL(0)+(Uвх-Uвых)t/L где iL(0)-ток, проходящий через катушку в момент отпирания транзистора.

В момент времени t=t1 ,транзистор закрывается(т.е. ключ размыкается). Ток iL(t1) убывает также по линейному закону, протекая через открытый диод: iL=iL(t1)-Uвыхt/L

Затем в момент времени t2 снова замыкается ключ (открывается транзистор) и ток iL на- чинает увеличиваться по линейному закону. Цикл повторяется.

Режим работы стабилизатора при iL(t2) 0 называют режимом непрерывного тока.

В

этом

случае

выражение

для

определения

пульсаций

тока,

протекающего

через

катушку

индуктивности

можно

записать

так:

iL=(Uвх-Uвых)(t2-t1)/2L=(Uвх-Uвых)tзамк/2L

Пульсацию выходного напряжения Uвых определим, учитывая, что в установившемся режиме работы схемы средние значения токов, протекающих через катушку индуктивности и нагрузку, равны между собой.

Следовательно, среднее значение тока, протекающего через конденсатор, равно нулю, а изменение напряжения на нем или пульсация выходного напряжения определяется только пульсацией тока iL0;напряжение на конденсаторе Uc увеличивается. При уменьшении iL от- носительно IL0 напряжение Uc также уменьшается.

Таким образом, можно записать уравнение баланса электрических зарядов в цепи катуш- ки индуктивности и конденсатора.

iL/2*T/2=2UвыхС (*) где Т-период переключения силового транзистора,iw/2- среднее значение пульсаций тока за половину периода, т.е. Т/2; 2Uвых - изменение напря- жения на конденсаторе за половину периода.

Из выражения (*) следует: Uвых=iLT/8C=(Uвх-Uвых)tзамк/16LCf

Из данного выражения следует, что для обеспечения малой пульсации выходного напря- жения необходимо увеличивать частоту переключения f. Однако при увеличении частоты возрастают потери мощности в РЭ, катушке индуктивности, что приводит, в конечном сче- те, к снижению КПД. Обычно частота регулирования импульсных стабилизаторов напря- жения лежит в пределах 2-50 кГЦ.

Понятия цифровой электроники. Логические операции. Логические элементы

Теоретической основой проектирования цифровых устройств является алгебра логики, или алгебра Д. Буля, оперирующая двумя логическими высказываниями «истинно» и «ложно», которые обозначаются соответственно символами 1 и 0.

Сложное высказывание называется логической функцией: y=f(x1,x2...xn), в которой сама функция y и ее аргументы - двоичные числа, принимаюшие значения 0 и 1. Наиболее часто в цифровых схемах применяются логические элементы, реализующие следующие логиче- ские функции:

Логические операции

. Инверсия : Y X

Таблица истинности. Таблица истинности ставит в соответствие определенной комби-

нации входных переменных – заданное значение логической функции.

Таблица 10.1. Таблица истинности инвертора &

|

|

|

|

|

|

|

1 |

|

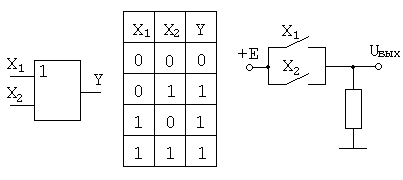

. Операция логического сложения или дизъюнкция: Y = X1 + X2

= X1UX2

Операция логического умножения или конъюнкция: Y = X1*X2 = X1&X2

1 Инвертор - реализует функцию логического отрицания или инверсии, которая часто

обозначается как НЕ.

Логические функции могут задаваться различными спосо- бами, из которых мы будем использовать 3.

аналитическое представление функции (для НЕ - y =x);

табличный способ, когда функция задается в виде таблицы истинности;

способ временных диаграмм.

Логический элемент ИЛИ - реализует функцию логического сложения (дизъюнкция).

Логический элемент И - реализует функцию логического умножения (конъюнкция).

Логический элемент И-НЕ (Штрих Шеффера).

Логический элемент ИЛИ-НЕ (Стрелка Пирса).

Логический элемент – равнозначность (исключающее ИЛИ-НЕ).

Логический элемент - Исключающее ИЛИ (неравнозначность).

Мажоритарный логический элемент или схема голосования.

|

1 |

2 |

3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

Y = 1, когда на входе единиц больше чем нулей.

24 | |||||

Основные тождества алгебры Буля

Алгебра логики (АЛ) является основным инструментом синтеза и анализа дискретных ав- томатов всех уровней. АЛ называют также Булевой алгеброй. АЛ базируется на трѐх функ- циях, определяющих три основные логические операции.

Функция отрицания (НЕ). f1 =X читается, как f1 есть (эквивалентна) НЕ Х. Элемент, реализующий функцию НЕ, называется элементом НЕ (инвертором).

Элемент НЕ имеет два состояния.

Функция логического умножения (конъюнкции). Функция логического умножения за-

писывается в виде f2=X1·X2. Символы логического умножения &, , <>, . Функция конъ- юнкции читается так: f2 есть (эквивалентна) Х1 и Х2, поскольку функция истинна тогда, ко- гда истинны 1-й и 2-й аргументы (переменные). Конъюнкцию называют функцией И, эле- мент, реализующий эту функцию, элементом И.

В общем случае функцию логического умножения от n переменных записывают так:

Количество переменных (аргументов), участвующих в одной конъюнкции, соответст- вует количеству входов элемента И.

Логическое сложение (дизъюнкция). Функция логического сложения записывается в ви- де f3=X1 + X2, и читается так: f3 есть Х1 или Х2, поскольку функция истинна, когда истин- на одна или другая переменная (хотя бы одна). Поэтому функцию дизъюнкции часто назы- вают функцией ИЛИ. Символы логического сложения +,V.

В общем случае функция ИЛИ записывается:

Используя операции (функции) И, ИЛИ, НЕ можно описать поведение любого комбинаци- онного устройства, задав сколь угодно сложное булево выражение. Любое булево выраже- ние состоит из булевых констант и переменных, связанных операциями И, ИЛИ, НЕ.

Пример булева выражения:

.

Основные

законы

алгебры

логики.

Основные

законы

АЛ

позволяют

проводить

экви-

валентные

преобразования

функций,

записанных

с

помощью

операций

И,

ИЛИ,

НЕ,

приво-

дить

их

к

удобному

для

дальнейшего

использования

виду

и

упрощать

запись.

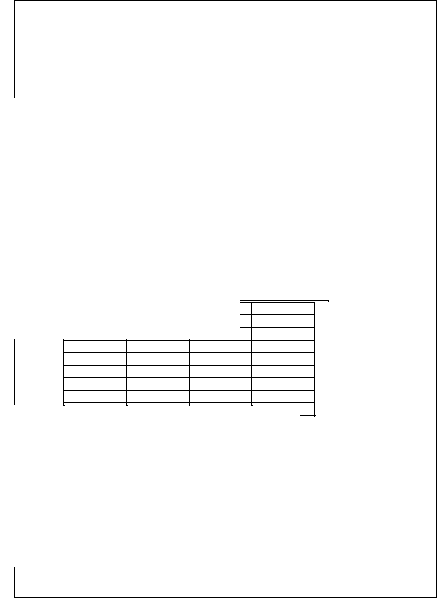

ЗАКОНЫ АЛГЕБРЫ ЛОГИКИ Таблица 1.1

|

N |

а |

|

|

б |

Примечание | ||

|

1 2 3 4 5 |

=1

X+0=X

X+1=1

X+X=X

X+

|

=0

X*1=X

X*0=0

X*X=X

X*

|

Аксиомы (тождества) | ||||

|

6 |

|

=X |

|

|

Закон двойного отрица- ния | ||

|

7 |

X+Y=Y+X |

X*Y=Y*X |

Закон коммутативности | ||||

|

8 |

X+X*Y=X |

X =X |

Закон поглощения | ||||

|

9 |

|

|

=

|

|

Правило де-Моргана (за- кон дуальности) | ||

|

10 |

|

|

+Z=X+Y+Z |

|

Закон ассоциативности | ||

|

11 |

X+ *Z= X+ Z |

|

Закон дистрибутивности | ||||

Булевой алгебре свойственен принцип двойственности, что наглядно иллюстрирован

в табл. 1.1. Как следует из табл. 1.1, только закон двойного отрицания не подчиняется этому

принципу.

Используя законы алгебры логики, можно упростить булевы выражения, в частности, пра-

вило склеивания позволяет упростить выражение типа

.

Действительно, используя законы 2, 5 и 11 можно записать исходное выражение в ви-

де Х2(Х1 +Х1 ) =Х2. Так как логическая операция Х1 +Х1 = 1 (см. з-н 5), а Х21 = Х2 (см. з- н 2б), полученное выражение истинно.

Системы исчисления

В дискретной автоматике и вычислительной технике числовая информация представ- ляется в двоичной системе счисления, при этом двоичные переменные можно рассматри- вать как элементы двоичного кода числа, то есть как цифры этой системы счисления. Дво- ичная система счисления, как и десятичная, относится к позиционным системам и является системой с основанием 2. В десятичной системе число А, имеющее n-разрядную целую часть и m-разрядную дробную часть, представляется суммой:

А=an-110n-1+an-210n-2++ai10i++a0100+a-110-1+a-210-2++a-m10-m,

где ai - десятичная цифра от 0 до 9, а основанием системы счисления является число 10.

Например, число 236.75 в десятичной системе счисления в соответствии с этим уравнением

можно записать: 236.75=2102+3101+6100+710-1+510-2.

Аналогично, в двоичной системе счисления число В можно представить в виде суммы

В=bn-12n-1+bn-22n-2++bi2i++b020+b-12-1+b-22-2++b-m2-m,

где bi - двоичные цифры 0 и 1, а основанием системы счисления является число 2 (в деся-

тичном виде). Например, то же число 236.75 в двоичном коде запишется:

236.75=127+126+125+024+123+122+021+020+12-1+12-2

Разумеется, для одного и того же числа А, количество разрядов в двоичной системе существенно больше, чем в десятичной. Например, трехразрядное десятичное число 235 в двоичной системе представляется восемью разрядами: 11101011. Перевод целой части числа из десятичной системы в двоичную производится методом последовательного деле- ния числа на 2 до тех пор, пока частное от деления не станет равным единице, например:

При этом число в двоичной системе числения записы-

|

42 |

2 |

|

|

|

|

|

|

42 |

21 |

|

2 |

|

|

|

|

0 |

20 |

|

10 |

2 |

|

|

|

|

1 |

|

10 |

5 |

2 |

|

|

|

|

|

0 |

4 |

2 |

2 |

|

|

|

|

|

1 |

2 |

1 |

|

0 | ||||||

вается в виде остатков от деления, начиная с послед-

него частного, справа налево. В рассмотренном при-

мере: 42

(10)

=

101010

(2).

Для

перевода

дробной

части

числа

последова-

тельно

умножаем

дробную

часть

на

два.

Двоичное число записывается в виде целых час- тей чисел, полученных при умножении только дробной части, начиная сверху после запя-

той. В рассматриваемом примере (0,6875) (10) = 0,1011(2).

|

0 |

6875 |

|

|

X2 |

|

1 |

375 |

|

|

X2 |

|

0 |

75 |

|

|

X2 |

|

1 |

5 |

|

|

X2 |

|

1 |

0 |

По рассмотренным правилам числа можно переводить и в другие сис- темы счисления, например в восьмеричную, шестнадцатеричную и т. д., во всех случаях умножение или деление производится на основание новой системы счисления. Для представления чисел в любой системе счисления с основанием р используется набор из р символов: для р=2 – (0,1), для р=8 – (0,1,2,3,4,5,6,7), для р=10 – (0,...,9), для р=16 – (0,...,9,A,B,C,D,E,F).

Правила перевода из восьмеричной и шестнадцатеричной систем в двоичную систему: переводим по порядку все символы - цифры, затем ну-

ли слева и справа в записи двоичного числа отбрасываем. Пример:

725,54Q = (111 010 101, 101 100) = 111010101,1011B

Обратный перевод из двоичной системы:

Для перевода в восьмеричную систему: разбиваем двоичное число на группы по 3 раз- ряда, начиная от запятой вправо и влево, добавляем недостающие нули слева и справа.

Аналогично для перевода из двоичной в шестнадцатеричную разбиваем на группы по 4 разряда. Пример: 1110101101,10111B = (001 110 101 101,101 110) = 1655,56Q

1110101101,10111B = (0011 1010 1101,1011 1000) = 3AD,B8H

Перевод числа из одной системы исчисления в другую и наоборот.

Двоичная система исчисления

516=5*10²+1*10¹+6*10º

Перевод чисел из двоичной системы в десятичную:

10000111 127

0 26

0 25

0 24

0 23

122

121 120

128

4

2

1

135

2.19 Нагрузочная способность элемента ТТЛ. Основы синтеза логических схем

Под нагрузочной способностью элемента ТТЛ понимают число входов других элемен- тов, которые можно подсоединить к выходу этого элемента.

Нагрузочная способность элемента ТТЛ определяется в элементе с открытым транзи- стором Т3, в элементе с двухтактным выходным каскадом – транзистор Т4. Iвх=1,6 mА.

Элементы с открытым коллектором можно соединить параллельно:

A &

B

A1 &

B1

+5 B

y

инципиальная параллельного соединения м коллектором

х схем можно расширять число входов ло-

Y

A

*

B*

A1*

B1

хтактным выходным каскадом соединять Если соединить параллельно:

пиальная параллельного соединения эле- ым каскадом (так соединять нельзя) верхний транзистор первого элемента и рого элемента течѐт одинаковый ток, по- туация, т.к. верхний транзистор рассчитан током, чем нижний.

схем:

аблицы истинности.

Y

1

Рис.1 Схема пр элементов с открыты

С помощью таки гических элементов.

Элементы с дву параллельно нельзя.

Рис.2 Схема принци ментов с двухтактным выходн При такой комбинации через через нижний транзистор вто этому создаѐтся аварийная си на работу с гораздо меньшим

Способы синтеза логических

Первый способ: с помощью т X1 X2 X3

0 0 0

0 0 1

1 1 1 1

Второй способ: временные диаграммы.

Рис. 3 Временные диагр

Третий способ: с помощью логического выражения.

1

0 1 0 0

0 1 1 1

1 0 0 0

1 0 1 1

1 1 0 1

аммы логических схем

x3

x2

x1

y

Y X1X2 X3 X1X2X3 X1X2X3 X1X2X3 X1X2 X3 X1X2X3

29

Четв

X3

X2 &

X1

&

X3 1 Y

ИЛИ X2 1

X1

ѐртый способ: Метод содержательного описания

Элемент ИЛИ-НЕ. Схема реализации элемента ИЛИ-НЕ

ставление логических элементов на основе базовых (на примере логического элемен НЕ»)

1 Y

Пред та

«И –

Элемент «НЕ»:

Схемотехническая реализация элемента «И – НЕ» такова, что свободный вход воспри- нимается, как логическая единица, т.е. в принципе необязательно соединять оба входа.

Элемент «И»

Элемент «ИЛИ» - реализуется на основе правила Шеннона де Моргана.

30

Элемент «исключающее ИЛИ»

Элемент «исключающее ИЛИ – НЕ»

Мультиплексоры

льтиплексора входов.

ципу кругового переключателя:

Рисунок 1 - Условное обозначение сдвоенного четырехканального селектора-мультиплексора 155КП12

Мультиплексором называется схема, имеющая m+2m входов и один выход, где m - число адресных входов, а 2m - число информаци- онных входов мультиплексора. Адреса представляются в двоичном коде и им присваивается номер j. Каждому адресу с номером j соот- ветствует свой информационный вход Аj, сигнал которого при данном адресе походит на выход.

Основным назначением мультиплексора является коммутация 2m входных сигналов на один выход.

Мультиплексоры могут использоваться в качестве устройства для

выбора соответствующего канала.

На рис.1 приведено условное обозначение сдвоенного четырехка-

нального селектора-мультиплексора 155КП12.