Синтез счётной схемы

Для определения функций возбуждения каждого триггера составляется кодированная таблица переходов. В проектируемой счётной схеме используются двухтактные JK- триггеры.

Совершаемые переходы и необходимые для их реализации значения функций возбуждения триггеров счётной схемы

Таблица 2

|

№ |

t=n |

t=n+1 |

Значение функции | ||||||||||||||||||

|

Т6 |

Т5 |

Т4 |

Т3 | ||||||||||||||||||

|

Q6 |

Q5 |

Q4 |

Q3 |

Q6 |

Q5 |

Q4 |

Q3

|

J6 |

K6 |

J5 |

K5 |

J4 |

K4 |

J3

|

K3

| ||||||

|

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

Х |

0 |

Х |

0 |

Х |

1 |

Х | |||||

|

2 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

Х |

0 |

Х |

1 |

Х |

Х |

1 | |||||

|

3 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

Х |

0 |

Х |

Х |

0 |

1 |

Х | |||||

|

4 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

Х |

1 |

Х |

Х |

1 |

Х |

1 | |||||

|

5 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

Х |

Х |

0 |

0 |

Х |

1 |

Х | |||||

|

6 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

Х |

Х |

0 |

1 |

Х |

Х |

1 | |||||

|

7 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

Х |

Х |

0 |

Х |

0 |

1 |

Х | |||||

|

8 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

Х |

Х |

1 |

Х |

1 |

Х |

1 | |||||

|

9 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

Х |

1 |

0 |

Х |

0 |

Х |

0 |

Х | |||||

На основе Таблицы 2 составляем карты Карно для определения функций возбуждения триггеров:

J6: J5:

J6= J5=

J5=

К6=

K5:

K5=

J4

= K4 =

J3= K3= 1

K3= 1

На основе произведенной по картам Карно минимизаций функций построим счётную схему:

Рис. 4 Счетная схема проектируемого дискретного устройства

Синтез делителей частоты

В качестве делителей частоты можно использовать счётные схемы с числом устойчивых состояний равным требуемому коэффициенту деления.

В соответствии с заданным вариантом необходимо разделить частоту 22000Гц до 1Гц. Очевидно, коэффициент деления n = 22000 большой. Тогда целесообразно использовать каскадное соединение нескольких делителей. В данном случае каскад будет состоять из одного делителя частоты на 11, одного на 2 и трёх делителей на 10.

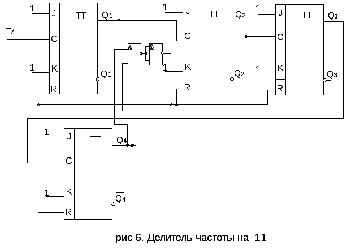

Для построения делителя частоты на 11 можно использовать 4 JK- триггера работающих в счётном режиме. Для изменения коэффициента деления после каждого третьего импульса схема должна сбрасываться в исходное, нулевое состояние и начинать отсчёт заново с каждого следующего импульса. Сброс схемы можно осуществить путём кратковременной подачи логической единицы на установочные входы R каждого триггера.

Реализованная схема представлена ниже:

Делителем частоты на 2 является единичный триггер, работающий по заднему фронту тактового импульса, в счетном режиме.

Для построения делителя частоты на 10 можно использовать 4 JK- триггера работающих в счётном режиме. Аналогично, как и с делителем на 11, схема должна сбрасываться в нулевое состояние после каждого 10 импульса.

Реализованная схема представлена ниже: