Мс ттл повышенного быстродействия.

Б

ыстродействие

МС можно повысить двумя путями: а)

уменьшая сопротивление резисторов и

паразитные емкости; б) предотвращая

насыщение транзисторов схемы, а,

следовательно, и накопление носителей

зарядов в их базах.

ыстродействие

МС можно повысить двумя путями: а)

уменьшая сопротивление резисторов и

паразитные емкости; б) предотвращая

насыщение транзисторов схемы, а,

следовательно, и накопление носителей

зарядов в их базах.

Малые сопротивления в МС серий 130 и 131 (tЗ.Р. – 12 нс при Р – 23 мВт).

Базовый элемент в принципе не отличается от аналогичных элементов других серий ТТЛ.

Выходной каскад с парой совмещенных транзисторов (схема Дарлингтона) обладает меньшим выходным сопротивлением, что способствует быстродействию.

Более результативный и перспективный путь связан с применением транзисторов с барьером Шотки.

Транзисторы шоттки

Транзисторы Шоттки отличаются от обычных тем, что они не входят в глубокое насыщение, следовательно, в их базах в открытом состоянии накапливается мало носителей заряда, и в результате время их рассасывания меньше обычного.

Эффект Шоттки снижает напряжение открывания кремниевого p–n перехода от обычных 0,5 ... 0,7 В до 0,2 ... 0,3 В и значительно уменьшает время жизни неосновных носителей в полупроводнике. Эффект Шоттки основан на том, что в p–n переходе или рядом с ним присутствует очень тонкий слой металла, богатый элементами, свободный носителями.

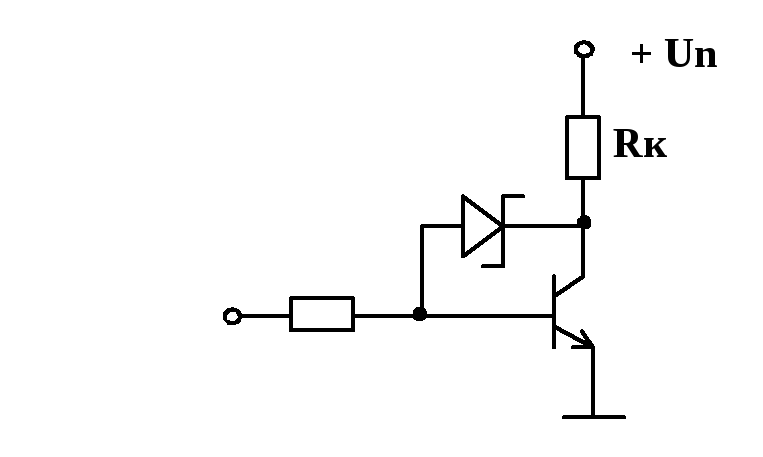

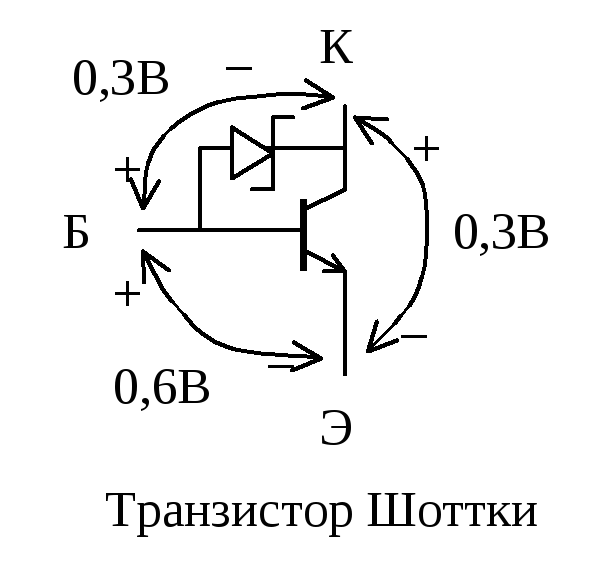

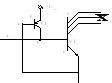

Транзистор Шоттки можно представить как обычный транзистор с диодом Шоттки, включенном между его базой и коллектором, как показано на рис. 7.1.1.

Рис. 7.1.1. Транзистор Шоттки, представленный как обычный транзистор с диодом Шоттки, включенном между его базой и коллектором

При открывании транзистора базовый ток нарастает только до значения, лежащего на границе активного режима и области насыщения, а весь избыточный базовый ток отводится через открытый диод Шоттки через коллектор и эмиттер открытого транзистора на землю.

Чем сильнее откроется транзистор, т.е. тем меньше падение напряжения коллектор–эмиттер, тем больший ток отводится через диод Шоттки, минуя базу, на землю. Это приведет к закрыванию транзистора, т.к. уменьшение тока базы закрывает транзистор. Так образуется обратная связь, саморегулирующая режим работы транзистора, удерживая его от глубокого насыщения.

Сами диоды Шоттки имеют очень малые задержки включения и выключения. Накопление заряда в диодах Шоттки не происходит, т.к. протекающий в них ток вызван переносом основных носителей.

Когда транзистор заперт потенциал коллектора выше потенциала базы, а значит диод Шоттки смещен в обратном направлении и не влияет на работу транзистора.

Если в процессе отпирания транзистора потенциал коллектора становится ниже потенциала базы, диод Шоттки открывается и на нем устанавливается прямое напряжение Uпр. Поскольку это напряжение меньше 0,5 В, то коллекторный переход практически заперт, а следовательно, не возникает режима насыщения и связанных с ним двойной инжекции и накопления избыточных зарядов. Благодаря этому при запирании транзистора исключается задержка, вызываемая рассеиванием избыточного заряда.

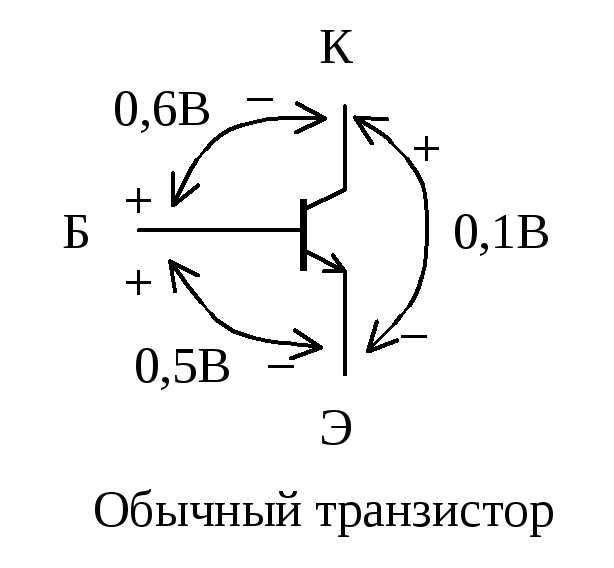

На рис 7.1.2. показана разность потенциалов между выводами обычного транзистора и транзистора Шоттки, подтверждающая большее напряжение между коллектором и эмиттером транзистора Шоттки в открытом состоянии.

Рис. 7.1.2. Разность потенциалов между выводами обычного транзистора и транзистора Шоттки

Шифраторы

Шифратор

выполняет функцию, обратную дешифратору.

Классический шифратор имеет m

входов и n

выходов, и

при подаче сигнала на один из входов

(обязательно на один, и не более) на

выходе появляется двоичный код номера

возбужденного входа. Число входов и

выходов такого шифратора связано

соотношением m=2n.

Шифратор можно использовать, например,

для отображения в виде двоичного кода

номера нажатой кнопки или положения

многозначного переключателя.

Шифратор

выполняет функцию, обратную дешифратору.

Классический шифратор имеет m

входов и n

выходов, и

при подаче сигнала на один из входов

(обязательно на один, и не более) на

выходе появляется двоичный код номера

возбужденного входа. Число входов и

выходов такого шифратора связано

соотношением m=2n.

Шифратор можно использовать, например,

для отображения в виде двоичного кода

номера нажатой кнопки или положения

многозначного переключателя.

Линии связи между схемами и блоками ТТЛ

(Транзисторная логика с непосредственной связью). Эти элементы относятся к началу разработки МС и на практике не используются. Однако идеи построения этих элементов используются в современных МС.

Основная идея этих ЛЭ заключаются в суммировании (вычитании) проводимостей (сопротивлений) В ВЫХОДНЫХ ЦЕПЯХ полупроводниковых цифровых ключей в зависимости от комбинации двоичных кодов (представленных уровнями тока или напряжения во входных цепях).

Д ля

сравнения можно вспомнить РТЛ или ДТЛ,

где суммирование происходит во входной

цепи.

ля

сравнения можно вспомнить РТЛ или ДТЛ,

где суммирование происходит во входной

цепи.

Простейшие схемы ТЛНС “И-НЕ” и “ИЛИ-НЕ” представлены на рисунке.

Простота схем приводила к тому, что их рассматривали как схемную основу цифровой полупроводниковой электроники. Однако у этих схем есть ряд недостатков:

Логический элемент И-НЕ ТЛНС имеет ИНДИВИДУАЛЬНУЮ характеристику по каждому входу. Это приводит к тому, что не обеспечивается пространство схемного интерфейса по разным логическим входам.

З

десь

должна рассматриваться передаточная

характеристика не в видеUвых=f(Uвх),

а в виде Iк=f(Iвх).

десь

должна рассматриваться передаточная

характеристика не в видеUвых=f(Uвх),

а в виде Iк=f(Iвх).При каждом включении выхода на несколько нагрузок возникает явление “ПЕРЕХВАТА ТОКА”

Из рисунка видно, что при параллельно включенных p-n – переходах на линии нагрузки (1-го каскада) установится напряжение Uбэ, определяемое транзистором с наиболее крутой ВАХ. Величины токов базы транзисторов при этом будут отличаться в десятки раз. Это явление получило название “ПЕРЕХВАТ ТОКА”.

При этом управляющие токи в нагрузке (ЛЭ 2-го каскада) будут существенно различаться вплоть до отсутствия напряжения в некоторых логических элементах.

С целью устранения этого явления в цепи базы вводят дополнительные резисторы (создают модифицированные ТЛНС (МТЛНС)).

Но резистор занимает на кристалле МС много места, а быстродействие оказывается существенно ниже, чем у ТТЛ МС.

Р ешение

проблемы “перехвата тока” нашли в

разработке ИИЛ.

ешение

проблемы “перехвата тока” нашли в

разработке ИИЛ.

Здесь приведено новое разделение предыдущей схемы.

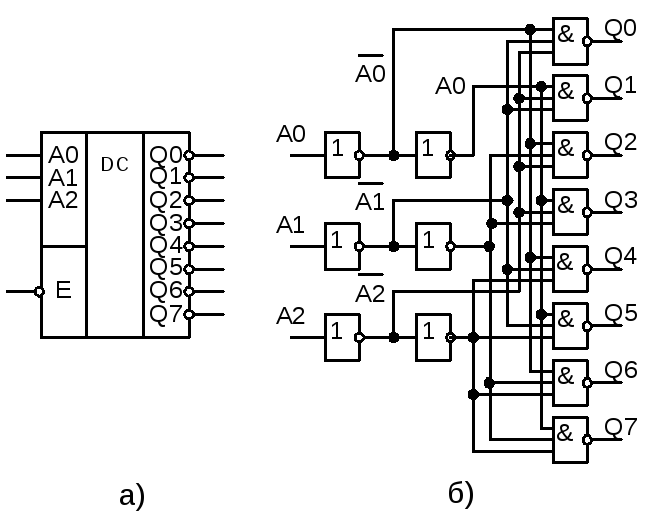

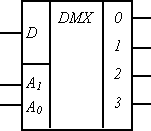

Дешифраторы

Д ешифратором

(ДШ) чаще всего называют устройство,

преобразующее двоичный код в унарный.

Из всехm

выходов дешифратора активный уровень

имеется только на одном, а именно на

том, номер которого равен поданному на

вход двоичному числу. На всех остальных

выходах ДШ уровни напряжения неактивные.

Обычно ДШ имеют инверсные выходы. При

этом на выбранном выходе 0, а на всех

остальных "1". Унарный код называют

еще кодом "1

из

m". Условное

изображение ДШ с инверсными выходами

показано на рис. 3.1,а. О входе Е будет

сказано ниже.

ешифратором

(ДШ) чаще всего называют устройство,

преобразующее двоичный код в унарный.

Из всехm

выходов дешифратора активный уровень

имеется только на одном, а именно на

том, номер которого равен поданному на

вход двоичному числу. На всех остальных

выходах ДШ уровни напряжения неактивные.

Обычно ДШ имеют инверсные выходы. При

этом на выбранном выходе 0, а на всех

остальных "1". Унарный код называют

еще кодом "1

из

m". Условное

изображение ДШ с инверсными выходами

показано на рис. 3.1,а. О входе Е будет

сказано ниже.

Если ДШ имеет n входов, m выходов и использует все возможные наборы входных переменных, то m=2n . Такой ДШ называют полным.

ДШ используют, когда нужно обращаться к различным ЦУ, и при этом номер устройства – его адрес – представлен двоичным кодом.

Адресные входы ДШ обозначают обычно А0, А1, А2,..А(n-1), где индекс буквы А означает показатель степени 2. Иногда эти входы просто нумеруют в соответствии с весами двоичных разрядов: 1, 2, 4, 8, 16,..2n-1.

Формально описать работу ДШ можно, задав список функций, обрабатываемых каждым из его выходов. Так для ДШ (рис. 3.2,а)

![]()

![]()

Реализация этих восьми выражений с помощью восьми трехвходовых ЛЭ 3И-НЕ дает наиболее простой по структуре ДШ, азываемый линейным.

Схемотехника ИС на полевых транзисторах

Интегральная МС – микроэлектронное изделие, выполняющее определенную функцию преобразования, обработки сигнала и (или) накапливания информации и имеющее высокую плотность упаковки электрически соединенных элементов и (или) кристаллов которое рассматривается как единое целое

Области применения полевых транзисторов

Значительную часть используемых в настоящий момент полевых транзисторов составляют КМОП (CMOS) транзисторы, которые в свою очередь используются повсеместно в цифровых интегральных схемах.

За счёт того, что полевые транзисторы управляются полем (величиной напряжения приложенного к затвору), а не током протекающем через базу (как в биполярных транзисторах) полевые транзисторы потребляют значительно меньше энергии, особенно в схемах ждущих и следящих устройств, а также в схемах малого потребления и энергосбережения (реализация спящих режимов).

Выдающийся пример устройства построенного на полевых транзисторах - пульт дистанционного управления для телевизора. За счёт применения полевых транзисторов пульт может работать до нескольких лет непрерывно ожидая нажатия кнопок, потому что практически не потребляет энергии.

ИС преобразователи кодов. Шифраторов и дешифраторов.

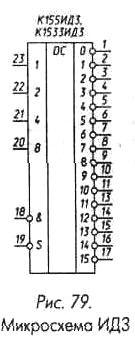

М икросхема

ИДЗ (рис. 79) имеет четыре адресных входа

1, 2,4, 8, два инверсных входа стробирования

S, объединенных по И, и 16 выходов 0-15. Если

на обоих входах стробирования лог. 0, на

том из выходов, номер которого соответствует

десятичному эквиваленту входного кода

(вход 1 - младший разряд, вход 8 -старший),

будет лог. 0, на остальных выходах - лог.

1. Если хотя бы на одном из входов

стробирования S лог. 1, то независимо от

состояний входов на всех выходах

микросхемы формируется лог. 1.

икросхема

ИДЗ (рис. 79) имеет четыре адресных входа

1, 2,4, 8, два инверсных входа стробирования

S, объединенных по И, и 16 выходов 0-15. Если

на обоих входах стробирования лог. 0, на

том из выходов, номер которого соответствует

десятичному эквиваленту входного кода

(вход 1 - младший разряд, вход 8 -старший),

будет лог. 0, на остальных выходах - лог.

1. Если хотя бы на одном из входов

стробирования S лог. 1, то независимо от

состояний входов на всех выходах

микросхемы формируется лог. 1.

Наличие двух входов стробирования существенно расширяет возможности использования микросхем. Из двух микросхем ИДЗ, дополненных одним инвертором, можно собрать дешифратор на 32 выхода (рис. 80),

Ф ункцию,

обратную функции дешифраторов, выполняют

шифраторы.

ункцию,

обратную функции дешифраторов, выполняют

шифраторы.

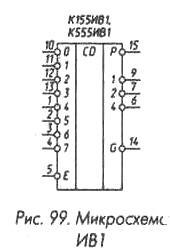

Микросхема ИВ1 - приоритетный шифратор (рис. 99). Она имеет восемь информационных входов 0-7 и вход разрешения Е. Выходов у микросхемы пять - три инверсных выходного кода 1,2,4; G -признака подачи входного сигнала и Р - переноса.

Если на всех информационных входах микросхемы лог. 1, на выходах 1,2,4, G - лог. 1, на выходе Р - лог. 0. При подаче лог. 0 на любой из информационных входов 0-7 на выходах 1,2, 4 появится инверсный код, соответствующий номеру входа, на который подан лог. 0, на выходе G'- лог. 0, что является признаком подачи входного сигнала, на выходе Р - лог. 1, которая запрещает работу других микросхем ИВ1 при их каскадном соединении. Если лог. 0 будет подан на несколько информационных входов микросхемы, выходной код будет соответствовать входу с большим номером.

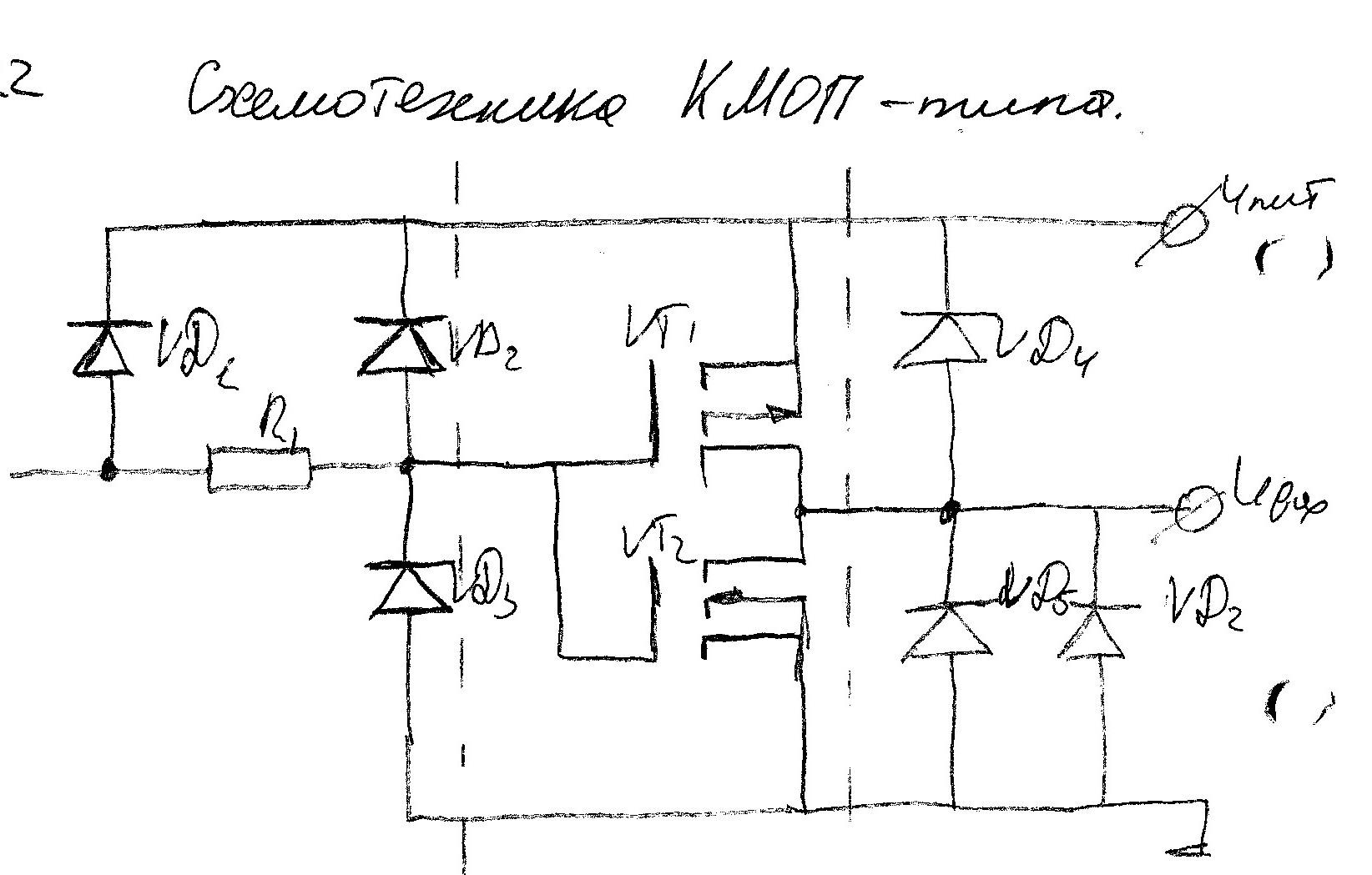

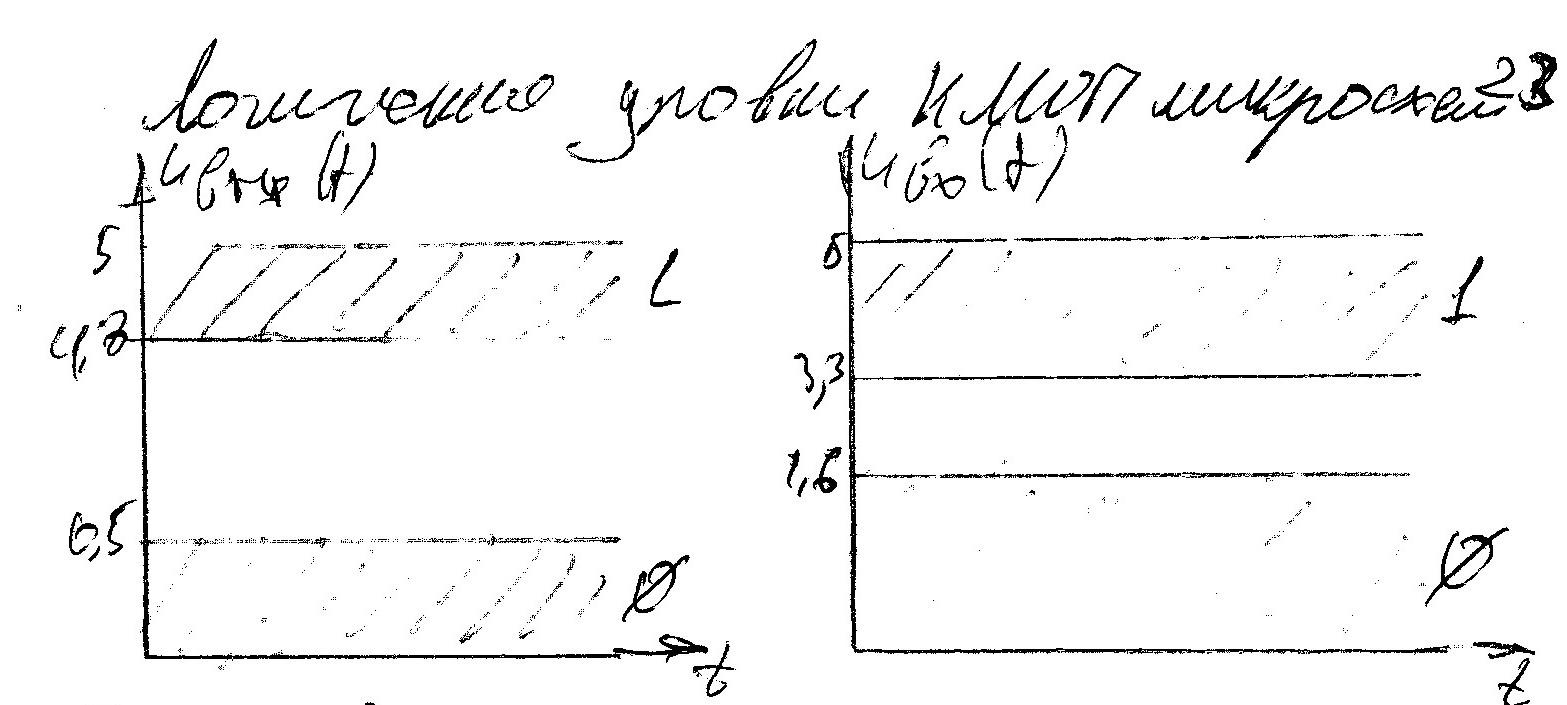

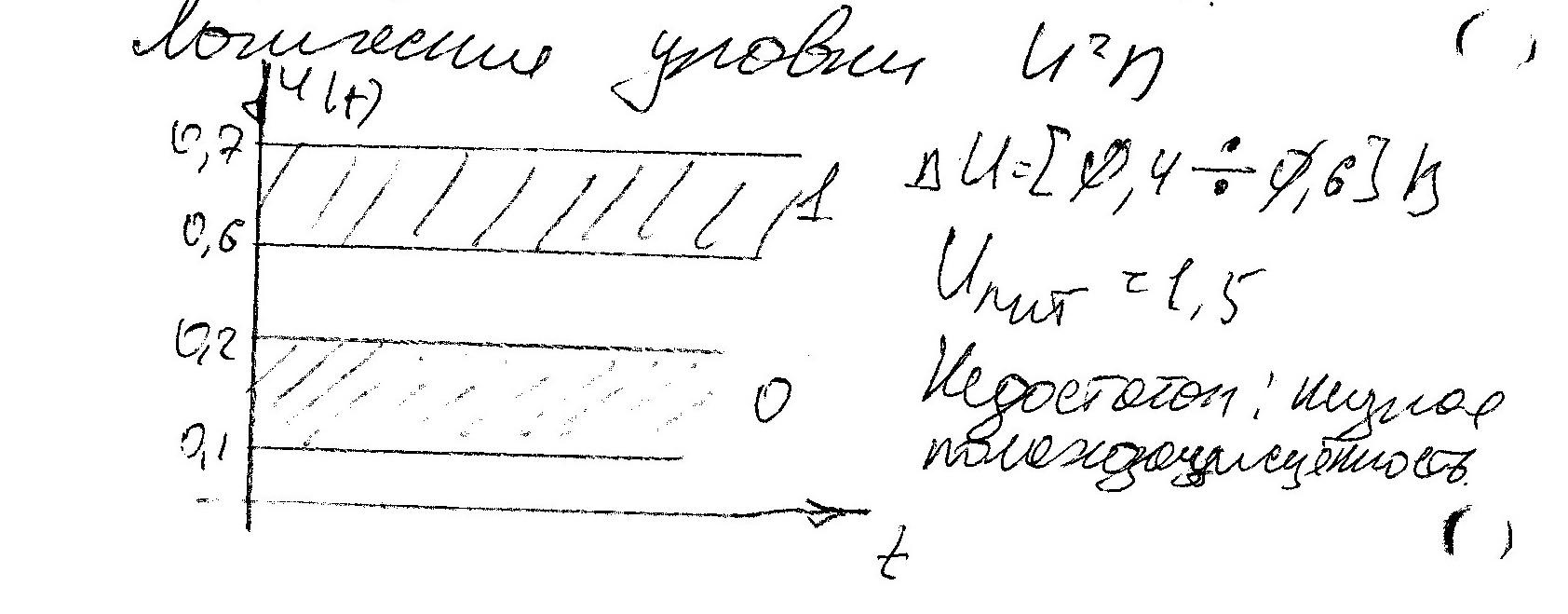

Схемотехника ИС на КМОП

Ключ на комплиментарно транзисторной логике при правильном выборе параметров входящих в него элементов в статическом режиме работы практически не потребляет мощность от источника питания

Базовая схема КМОП разбита на 3 части

Входной диодно-резисторный ограничитель напряжения

Ключи на КМОП транзисторах

Выходная диодная цепь

Основные достоинства КМОП элементов это высокая помехоустойчивость до 30-40% напряжения питания

При увеличении тока нагрузки напряжения логической 1 может уменьшится до 2,8 при 15В напряжения питания

Недостаток: невысокое быстродействие.

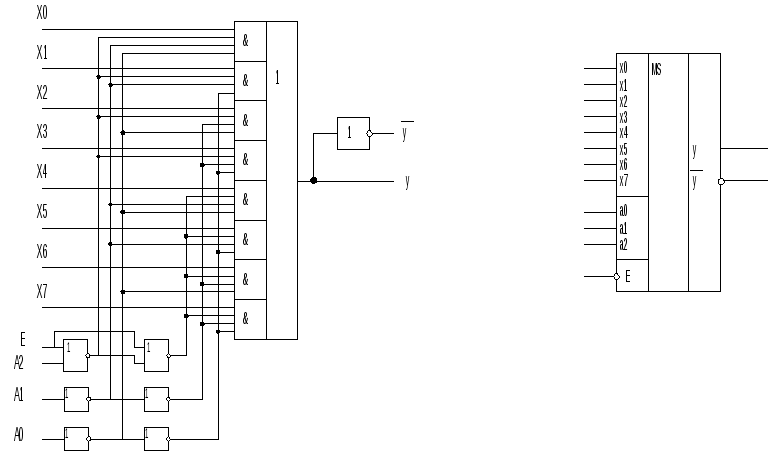

Мультиплексоры

Мультиплексор – это функциональный узел, осуществляющий подключение

( коммутацию ) одного из нескольких входов данных к выходу. С помощью мультиплексора выполняется временное разделение информации, поступающей по разным каналам.

Мультиплексоры обладают двумя группами входов и одним, реже двумя – взаимодополняющими выходами. Одни входы информационные, а другие служат для управления. К ним относятся адресные и разрешающие (стробирующие) входы. Если мультиплексор имеет n адресных входов, то число информационных входов будет 2 n. Набор сигналов на адресных входах определяет конкретный информационный вход, который будет соединен в выходным выводом.

Разрешающий (стробирующий ) вход управляет одновременно всеми информационными входами независимо от состояния адресных входов.

Запрещающий сигнал на этом входе блокирует действие всего устройства.

Наличие разрешающего входа расширяет функциональные возможности мультиплексора, позволяя синхронизировать его работу с работой других узлов.

Этот вход используется также для наращивания разрядности мультиплексора.

На рис 3.8 показаны схема и условное обозначение мультиплексора К555КП7.

Рис.3.8. Схема а) и условное обозначение б) мультиплексора К555КП7.

По функциональным возможностям мультиплексоры являются очень гибкими устройствами и помимо прямого назначения могут выполнять и другие функции.

Схемотехника ИС ИИЛ

С хема

интегральной инжекционной логики (ИИЛ),

или И2Л

– схемы, являются развитием схем с

непосредственными связями (рисунок 1).

Основные положения, на которых базируются

построения схем с непосредственными

связями, остаются в силе при построении

И2Л-схем,

выполненных на современном уровне и с

использованием всех последних достижений

интегральной технологии. Работоспособность

такой схемы зависит от выбора нагрузки,

задающей ток в боковой цепи выходного

транзистора (пунктир на рисунке).

хема

интегральной инжекционной логики (ИИЛ),

или И2Л

– схемы, являются развитием схем с

непосредственными связями (рисунок 1).

Основные положения, на которых базируются

построения схем с непосредственными

связями, остаются в силе при построении

И2Л-схем,

выполненных на современном уровне и с

использованием всех последних достижений

интегральной технологии. Работоспособность

такой схемы зависит от выбора нагрузки,

задающей ток в боковой цепи выходного

транзистора (пунктир на рисунке).

Основу схемотехники И2Л составляет инвертор (рисунок 2), работающий в насыщенном режиме и выполненный на многоколлекторном транзисторе VT2, обеспечивающим развязку выходу для исключения их взаимного влияния.

Н агрузка

для предыдущего каскада, принадлежащего

его базовой цепи, выполнена наp-n-p

– транзисторе VT1.

Схема очень технологична и занимает

минимальную площадь на кристалле.

агрузка

для предыдущего каскада, принадлежащего

его базовой цепи, выполнена наp-n-p

– транзисторе VT1.

Схема очень технологична и занимает

минимальную площадь на кристалле.

Особенности:

Отсутствие резисторов, что резко упрощает технологию изготовления.

Использование тактового принципа питания, при котором в интегральной схеме задается не напряжение, а ток, который непосредственно интегрируется в область полупроводника, образующего структуру одного из транзисторов.

Малое значение логического перепада, что позволяет максимально увеличить быстродействие

Недостаток: низкая помехозащищенность

Демультиплексоры

Демультиплексор – это функциональный узел, осуществляющий коммутацию информации с одного входа на один из нескольких выходов. Демультиплексоры в виде самостоятельных ИС не изготавливаются, т.к. их функции могут выполняться дешифратором, имеющим хотя бы один вход разрешения, который используется как информационный вход.

Если информационные входы и выходы обоих коммутаторов представляют линии, то такие коммутаторы называют линейными. Если же входы и выходы – шины, то получим шинные мультиплексоры и демультиплексоры.

Схемотехника ИС ЭСЛ

Эми́ттерно-свя́занная ло́гика (ЭСЛ) — технология построения логических элементов в цифровых интегральных микросхемах на основе дифференциальных эмиттерных каскадов. ЭСЛ является самой быстродействующей из всех типов логики. Это объясняется тем, что транзисторы в ЭСЛ работают в линейном режиме, не переходя в режим насыщения или отсечки. То есть транзисторы не используются как логические ключи.

Основная деталь ЭСЛ-логики — схема потенциального сравнения, собранная не на диодах (как в ДТЛ и ТТЛ), а на транзисторах. Схема представляет из себя транзисторы, соединённые эмиттерами и подключенные к корпусу (или питанию) через резистор. При этом транзистор у которого напряжение на базе выше пропускает через себя основной ток. Как правило один транзистор в схеме сравнения подключен к опорному уровню единицы (обычно просто стабилитрон), а остальные транзисторы являются входами. Выходные цепи схемы сравнения поступают на усилительные транзисторы, а с них — на выходные эмиттерные повторители.

Достоинства:

Высокое быстродействие

Расширенные логические возможности

Постоянство токопотребления

Большая нагрузочная способность

Стабильность характеристик

Недостатки:

Сложность схемотехники

Большая потребляемая мощность

Серии микросхем отечественного производства:100, 138, 500,1500,С1590, КС1590

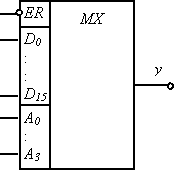

ИС Мультиплексоры и демультиплексоры

К 155

КП1. Это 16-

входовой мультиплексор. Имеет стробирующий

вход. Описание выводов К155КП1

155

КП1. Это 16-

входовой мультиплексор. Имеет стробирующий

вход. Описание выводов К155КП1

D0-D15 – входы каналов данных.

A0-A3 – адресные входы.

ER – вход стробирования. Низкий уровень на этом входе разрешает работу микросхемы, высокий - устанавливает выход в высокий уровень.

y – выход. Содержит инвертированное значение одного из каналов, выбранного кодом на адресных уровнях.

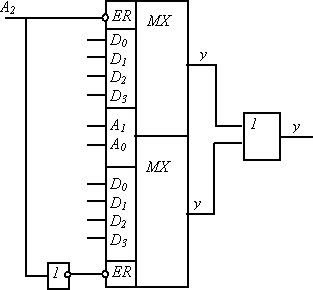

К 531КП2.

Содержит 2 мультиплексора, по 4

информационных входа на каждом с общими

адресными входами. Имеется два стробирующих

сигнала, что позволяет организовать

каскадное включение этих мультиплексоров.

При подаче сигналов на адресные входы

подключаются на выход линии данных с

верхнего мультиплексора.

531КП2.

Содержит 2 мультиплексора, по 4

информационных входа на каждом с общими

адресными входами. Имеется два стробирующих

сигнала, что позволяет организовать

каскадное включение этих мультиплексоров.

При подаче сигналов на адресные входы

подключаются на выход линии данных с

верхнего мультиплексора.

П ри

подаче на адресный входA2

-0 вкл. Верхний MX.

При A2=

1 подключаются линии данных нижнего

мультиплексора.

ри

подаче на адресный входA2

-0 вкл. Верхний MX.

При A2=

1 подключаются линии данных нижнего

мультиплексора.

Демультиплексоры Это комбинационные логические схемы, имеющие один вход и 2n выходов, которые адресуются.

Простейшие последовательные устройства. Триггеры.

Последовательностные схемы или цифровые автоматы (ЦА) с памятью составляют другой, более сложный класс преобразователей дискретной информации. В отличие от КС они имеют некоторое конечное число различных внутренних состояний. Выходные сигналы ЦА в данном такте определяются в общем случае входными сигналами, поступившими на вход ЦА в этом такте, и внутренним состоянием автомата, которое явилось результатом воздействия на автомат входных сигналов в предыдущие такты.

Комбинация входных сигналов и текущего состояния ЦА в данном такте определяет не только выходные сигналы, но и то состояние, в которое автомат перейдет к началу следующего такта.

Функции перехода и выходов могут задаваться в форме таблиц или с помощью графов. При задании в виде графов состояния автомата представляют вершинами, а переходы из состояния в состояние – дугами. На дугах указываются значения входных сигналов, вызывающих соответствующие переходы.

Примерами простейших конечных ЦА являются триггеры .

Триггер – это элемент цифрового устройства с двумя устойчивыми состояниями. Под воздействием входного сигнала триггер может переключаться из одного положения в другое, при этом напряжение на его выходе скачкообразно изменяется.

Как правило, триггер имеет два выхода прямой и инверсный(Q,Q). Число входов зависит от структуры и функций, выполняемых триггером. Входы, как и сигналы, подаваемые на них делятся на информационные и вспомогательные. Информационные сигналы через соответствующие входы управляют состоянием триггера. Сигналы на вспомогательных входах служат для предварительной установки триггера в заданное состояние и его синхронизации. Вспомогательные входы могут при необходимости выполнять роль информационного.

Входы и выходы триггера, как и соответствующие им сигналы, обозначают буквами:

S – раздельный вход установки в единичное состояние (напряжение высокого уровня на прямом входе Q);

R – раздельный вход установки в нулевое состояние (напряжение низкого уровня на прямом входе Q);

Д – информационный вход (на него передается информация, предназначенная для занесения в триггер);

С – вход синхронизации;

Т – счетный вход.

Триггеры классифицируют по ряду признаков. По функциональным возможностям выделяют триггеры: с раздельной установкой "0" и "1" (RS – триггеры); с приемом информации по одному входу (Д – триггеры); счетный Т – триггер; универсальный IK – триггер.

По способу приема информации триггеры подразделяют на асинхронные и синхронные. Асинхронные триггеры реагируют на информационные сигналы в момент их появления на входе. Синхронные – при наличии разрешающего сигнала специально предусмотренном входе С.

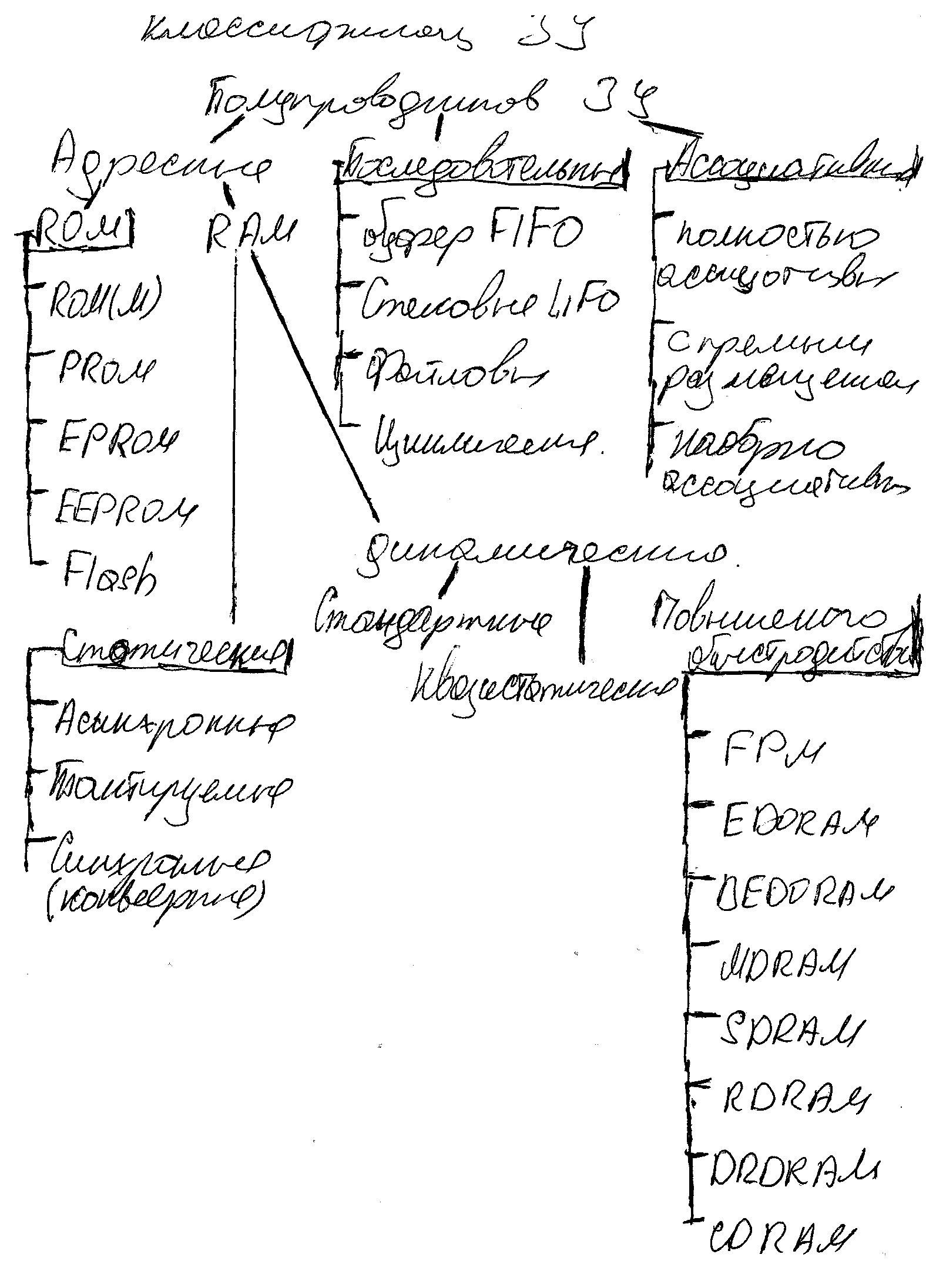

Цифровые ЗУ. Основные понятия и определения.

Это неотъемлемая часть любого современного компьютера во многом определяющая его технические характеристики.

Термины: «память» - обычно применяют к биологическим объектам, «запоминающий» – к техническим.

Под запоминающим элементам понимают физический объект, электрическую схему или их совокупность способные по внешней команде запомнить (фиксировать) некоторое входное воздействие (в цифровой или аналоговой форме представления информации), сохранять некоторое время и воспроизводить по внешней команде сохраненные значения.

Требования к идеальному запоминающему элементу:

время реакции на команду Тз0;

время реакции на команду чтения Тr0;

время хранения информации ;

возможность неограниченной, многократной смены информации;

отсутствие источника питания (энергонезависимость).

Такие характеристики получить трудно. Поэтому разработчики и технологи чаще делают не то, что необходимо, а то что получается.

Сейчас существуют:

элементы оперативных запоминающих устройств – ОЗУ (быстродействующих и сверхбыстродействующих), характеризующиеся примерно равными ТзТr, энергозависимостью, с ограниченной степенью интеграции;

элементы постоянных – ПЗУ , полупостоянных (программируемых) - ППЗУ и многократно программируемых (ре-программируемых) – РПЗУ, характеризующихся Тз>>Тr, ограничениями циклов записи, энергонезависимостью, ограничениями информационного объема;

элементы внешних ЗУ с примерно равными ТзТr, но значительно большими, чем у ОЗУ, энергонезависимостью, большими объемами хранимой информации и практически неограниченным количеством циклов записи – считывания.

Основные параметры триггерных схем

Основные параметры:

быстродействие;

Uпит;

потребляемая мощность;

коэффициент разветвленности по выходу;

коэффициент объединения по входу;

помехоустойчивость;

энергия переключения;

надежность;

стойкость к климатическим и механическим воздействиям;

Классификация ЗУ

Расчет …………

В синхронных схемах данные передаются от одного триггера к другому через некоторый комбинационный участок. Триггерами управляет сигнал тактовой синхронизации, период которого определяется задержкой передачи сигнала со входа триггера на его выход.

Время, в которое прибывает сигнал на выход может варьироваться в силу многих причин: схема может выполнять разные операции, варьируется температура окружающей среды или напряжение, изменяться под влиянием процесса производства и т. д. Главной задачей СВА в этом случае становится проверка того, что несмотря на все возможные вариации сигнал прибудет на выход схемы в заданные временные рамки, что является условием безошибочной работы схемы.

Критический путь — путь прохождения сигнала от входа до выхода схемы, имеющий наибольшую задержку.

Задержка прохождения сигнала — время, которое требуется электрическому сигналу, чтобы достичь некоторого узла в схеме.

Предельно допустимая задержка сигнала — максимальная задержка сигнала, при превышении которой необходимо увеличить длительность тактового периода.

Запас (slack) — значение, обычно рассчитываемое для каждого узла схемы, равное разности между предельно допустимой и фактической задержкой сигнала.

Основные параметры ЗУ

Основные параметры:

Информационная емкость

Организация ЗУ(произведение числа хранимых слов на их разрядность)

Быстродействие(производительность ЗУ) Оценивается временем считывания и записи.

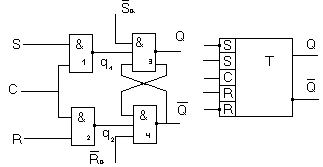

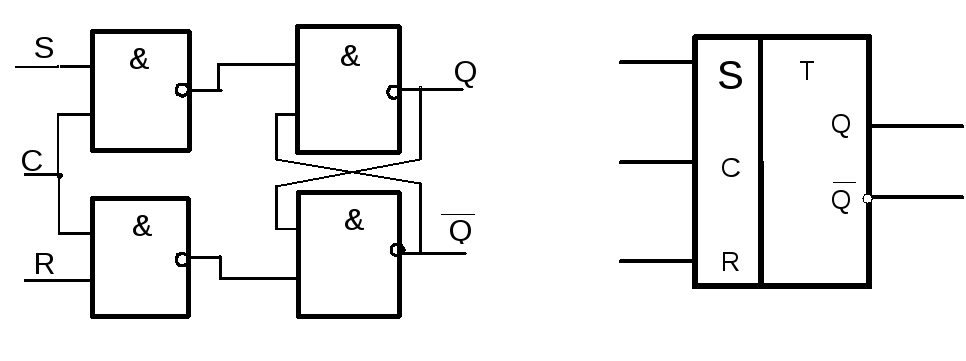

RS триггеры с установочными входами

С инхронный

(тактируемый) RS–триггер получается из

асинхронного путем подключения к его

входам схемы управления.

инхронный

(тактируемый) RS–триггер получается из

асинхронного путем подключения к его

входам схемы управления.

Здесь Sа и Ra – асинхронные входы, а S и R информационные входы. Вход С – тактовый (синхронизированный), q1 и q2 – внутренние сигналы, управляют соответственно триггером, который, как его асинхронный аналог на элементе И-НЕ, переключается сигналами нулевого уровня.Состояния синхронного RS - триггера представлены в таблице:

|

Такт n |

Такт n+1 | ||

|

С |

Rn |

Sn |

Qn+1 |

|

0 |

0 |

0 |

Qn |

|

0 |

1 |

0 |

Qn |

|

0 |

0 |

1 |

Qn |

|

0 |

1 |

1 |

Qn |

|

1 |

0 |

0 |

Qn |

|

1 |

1 |

0 |

0 |

|

1 |

0 |

1 |

1 |

|

1 |

1 |

1 |

- |

Статические ОЗУ

См 36

Синхронные RS триггеры

Основное назначение триггеров в цифровых схемах - хранить выработанные логическими схемами результаты. Для отсечения еще не установившихся, искаженных переходными процессами результатов между выходом логической схемы и входом триггера можно включить конъюнкторы, управляемые синхросигналом . Это решение оказалось очень эффективным, быстро стало типовым и побудило изготовителей триггеров ввести конъюнкторы в состав триггера. Так появились синхронные триггеры, которые переключаются в состояние, предписываемое управляющими входами, лишь по сигналу синхронизации, поступающему на вход С триггера.

а) б)

а) б)

Рис. 4.2. Синхронный RS-триггер

Схема простейшего синхронного RS-триггера показана на рис.4.2,а. При С=0 триггер 3-4 отключен от управляющих S и R входов и находится в режиме хранения ранее полученной информации. При С=1 схема функционирует как обычный RS-триггер. Условное изображение синхронного RS-триггера показано на рис.4.2,б. Синхровход С может в принципе иметь и активный низкий уровень; в этом случае он, как обычно, помечается кружочком. Характерной особенностью схемы является то, что в течение всего отрезка времени, когда синхросигнал равен 1, как сами потенциалы на управляющих S и R входах, так и любые их изменения тут же передаются на выход.

О такой схеме можно сказать, что она прозрачна по S - и R - входам при C=1. Не все схемы синхронных триггеров обладают этим свойством.

Динамические ОЗУ

Оперативная память (Random Access Memory – RAM), т.е. память с произвольным доступом, используется центральным процессором для совместного хранения данных и исполняемого программного кода. По принципам хранения информации ОЗУ можно разделить на статические и динамические.

Оперативную память можно рассматривать как некий набор ячеек, каждая из которых может хранить один информационный бит.

В статических ОЗУ ячейки построены на различных вариантах триггеров. После записи бита в такую ячейку она может сохранять его сколь угодно долго – необходимо только наличие питания. Отсюда и название памяти – статическая, т.е. пребывающая в неизменном состоянии. Достоинством статической памяти является ее быстродействие, а недостатками – высокое энергопотребление и низкая удельная плотность данных, поскольку одна триггерная ячейка состоит из нескольких транзисторов и, следовательно, занимает на кристалле немало места. К примеру, микросхема емкостью 4 Мбит состояла бы более чем из 24 млн. транзисторов, потребляя соответствующую мощность.

В динамических ОЗУ элементарная ячейка представляет собой конденсатор, выполненный по КМОП – технологии. Такой конденсатор способен в течение нескольких миллисекунд сохранять электрический заряд, наличие которого можно ассоциировать с информационным битом. При записи логической единицы в ячейку памяти конденсатор заряжается, при записи нуля – разряжается. При считывании данных конденсатор разряжается, и если его заряд был ненулевым, то на выходе схемы считывания устанавливается единичное значение. Процесс считывания (обращения к ячейке) сочетается с восстановлением (регенерацией ) заряда. Если обращения к ячейке не происходит в течение длительного времени, то конденсатор за счет токов утечки разряжается и информация теряется. Для компенсации утечки заряда периодически циклически обращаются к ячейкам памяти, т.к. каждое обращение восстанавливает прежний заряд конденсатора. К достоинствам динамической памяти относятся высокая плотность размещения данных и низкое энергопотребление, а к недостаткам – низкое быстродействие по сравнению со статической памятью.

В настоящее время динамическая память (Dynamic RAM – DRAM) используется в качестве оперативной памяти компьютера, а статическая память (Static RAM – SRAM)- для создания высокоскоростной кэш – памяти процессора.

Микросхемы динамической памяти организованы в виде квадратной матрицы, причем пересечение строки и столбца матрицы задает одну из элементарных ячеек. При обращении к той или иной ячейке нужно задать адрес нужной строки и столбца. Задание адреса строки происходит, когда на входы микросхемы подается специальный стробирующий импульс RAS (Raw Address Strobe), а задание адреса столбца – при подаче импульса CAS (Column Address Strobe). Импульсы RAS и CAS подаются последовательно друг за другом по мультиплексированной шине адреса.

Регенерация в микросхеме происходит одновременно по всей строке матрицы при обращении к любой из ее ячеек, т.е. достаточно циклически перебрать все строки.

Триггеры задержки. Д – триггеры

Правило работы: Вх. 0 -> хранение 0, вх. 1-> 1

Символ D-триггера с дополнительными асинхронными входами S и RD Q(t) Q(t+1)

0 0 0

0 1 0

1 0 1

1 1 1

D-триггер (D от англ. delay — задержка)— запоминает состояние входа и выдаёт его на выход. D-триггеры имеют, как минимум, два входа: информационный D и синхронизации С. Сохранение информации в D-триггерах происходит в момент прихода активного фронта на вход С. Так как информация на выходе остаётся неизменной до прихода очередного импульса синхронизации, D-триггер называют также триггером с запоминанием информации или триггером-защёлкой. Рассуждая чисто теоретически, D-триггер можно образовать из любых RS- или JK-триггеров, если на их входы одновременно подавать взаимно инверсные сигналы.

D-триггер в основном используется для реализации защёлки. Так, например, для снятия 32 бит информации с параллельной шины, берут 32 D-триггера и объединяют их входы синхронизации для управления записью информации в защёлку, а 32 D входа подсоединяют к шине.

ПЗУ

Постоянное запоминающее устройство (ПЗУ) — энергонезависимая память, используется для хранения неизменяемых данных.

Часто используется английский термин ROM (Read-Only Memory).

Существует несколько разновидностей ПЗУ, предназначенных для различных целей:

ROM — (англ. Read-Only Memory, постоянное запоминающее устройство), масочное ПЗУ, изготавливается фабричным методом. В дальнейшем нет возможности изменить записанные данные.

PROM — (англ. Programmable Read-Only Memory, программируемое ПЗУ (ППЗУ)) — ПЗУ, однократно «прошиваемое» пользователем.

EPROM — (англ. Erasable Programmable Read-Only Memory, перепрограммируемое ПЗУ (ПППЗУ)).

Например, содержимое микросхемы К537РФ1 стиралось при помощи ультрафиолетовой лампы. Для прохождения ультрафиолетовых лучей к кристаллу в корпусе микросхемы было предусмотрено окошко с кварцевым стеклом.

EEPROM — (англ. Electrically Erasable Programmable Read-Only Memory, электрически стираемое перепрограммируемое ПЗУ). Память такого типа может стираться и заполняться данными несколько десятков тысяч раз. Используеся в твердотельных накопителях. Одной из разновидностей EEPROM является флэш-память (англ. Flash Memory).

К ПЗУ можно также отнести:

CD-ROM

перфокарты и перфоленты.

В постоянную память обычно записывают микропрограмму управления техническим устройством: телевизором, сотовым телефоном, различными контроллерами.

Одним из видов микропрограмм, записанных в ПЗУ, является BIOS.

JK- триггеры

RS-триггер или SR-триггер

|

0 |

0 |

0 |

0 |

|

0 |

0 |

1 |

1 |

|

0 |

1 |

0 |

0 |

|

0 |

1 |

1 |

0 |

|

1 |

0 |

0 |

1 |

|

1 |

0 |

1 |

1 |

|

1 |

1 |

0 |

* |

|

1 |

1 |

1 |

* |

RS-триггер используется для создания сигнала с положительным и отрицательным фронтами, отдельно управляемыми посредством стробов, разнесённых во времени. Также RS-триггеры часто используются для исключения так называемого явления дребезга контактов.

JK-триггер

Символ JK-триггера с дополнительными асинхронными входами S и R, аналогично представлению в среде разработки Altera QuartusJ K Q(t) Q(t+1)

|

0 |

0 |

0 |

0 |

|

0 |

0 |

1 |

1 |

|

0 |

1 |

0 |

0 |

|

0 |

1 |

1 |

0 |

|

1 |

0 |

0 |

1 |

|

1 |

0 |

1 |

1 |

|

1 |

1 |

0 |

1 |

|

1 |

1 |

1 |

0 |

На базе JK-триггера возможно построить D-триггер или Т-триггер. Как можно видеть в таблице истинности JK-триггера, он переходит в инверсное состояние каждый раз при одновременной подаче на входы J и K логической 1. Это свойство позволяет создать на базе JK-триггера Т-триггер, объединив входы J и К[14].

РПЗУ

Репрограммируемые ЗУ с электрической записью информации и стиранием потоком ультрафиолетового излучения или эл. сигналом. Элемент памяти является лавинно-инжекционный МДП транзистор (ЛИПЗ/МДП), обладающий свойством переходить в состояние проводимости под воздействием импульса програмирующего напряжения и сохранять это состояние длительное время. Данный эвфект обусловлен накомпление электрического заряда под затвором диэлектрика. Если на транзистор не воздействоапли импульсом, то он сохраняет закрытое состояние для электрического тока. Для стирания необходимо вытеснить накопленный под затвором заряд. По способу стирания РПЗУ делятся на два вида:

-стирание электрическим сигналом(Flash)

-ультрофиолетовым светом через специальное окно в крышке корпуса.

М-с сохраняют инфу долгое время без питания, являются энергонезависимыми

Т- триггеры

Триггер со счетным входом. Он имеет один управляющий вход Т и два выхода Q и Q. Информация на выходе такого триггера меняет свой знак на противоположный. При каждом положительном (или при каждом отрицательном) перепаде напряжения на входе. В сериях выпускаемых МС Т-триггеров, как правило, нет. Но триггер такого типа может быть создан на базе тактируемого Д-триггера, если его инверсный выход соединить с информационным входом или на базе RS-триггера соединить выход со входом. Как видно из диаграммы, частота сигнала на выходе Т-триггера в два раза ниже частоты сигнала на входе. Поэтому такой триггер можно использовать как делитель частоты и двоичный счетчик.

Такой триггер, а также синхронный Т-триггер можно получить на основе JK-триггера (двухступенчатого универсального).

АЦП

Регистры. Регистры хранения.

Назначение регистров – хранение и преобразование много разрядных двоичных чисел. Регистры наряду со счетчиками и запоминающими устройствами являются наиболее распространенными последовательностными устройствами цифровой техники. Регистры обладают большими функциональными возможностями. Они используются в качестве управляющих и запоминающих устройств, генераторов и преобразователей кодов, счетчиков, делителей частоты, узлов временной задержки.

Элементами структуры регистров являются синхронные триггеры Д-типа, либо RS(IK)-типа с динамическим или статическим управлением.

Единичный триггер – простейший регистр (RG) используют в RG цепочке триггеров. Понятие "весовой коэффициент" к разрядам регистра неприменимо в отличие от счетчика, поэтому на условных изображениях нумерация входов и выходов идет подряд (Д1, Д2,Д3 и т.д., а не Д1, Д2, Д4, Д8).

RG в зависимости от функциональных свойств делятся на: накопительные и сдвигающие.

По способу ввода, вывода информации – параллельные, последовательные и комбинированные (//-последовательные и последовательно-//).

По направлению передачи (сдвига) информации – однонаправленные и реверсные.

Регистры памяти – простейший вид регистров – хранят двоичную информацию.

Э то

набор синхронных триггеров, каждый из

которых хранит один разряд двоичного

числа. Ввод (запись) и вывод (считывание)

производится одновременно во всех

разрядах. С приходом очередного тактового

импульса происходит обновление

информации.

то

набор синхронных триггеров, каждый из

которых хранит один разряд двоичного

числа. Ввод (запись) и вывод (считывание)

производится одновременно во всех

разрядах. С приходом очередного тактового

импульса происходит обновление

информации.

Считывание информации в прямом или обратном (с Q) коде.

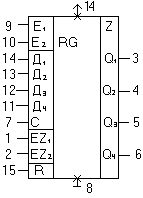

В качестве подобных регистров может быть использованы без дополнений элементов многих синхронных триггеров: К155ТМ8, ТМ5, ТМ7, 564ТМ3, 555ТМ8 и др. Наращивание разрядности регистра достигается добавлением нужного числа триггеров, тактовые выходы которых присоединяют к шине синхронизации. К1555ИР15 – регистр с тремя состояниями Д1-Д4 – информационные входы, С – синхронизированный вход, Q1-Q4 – прямые выходы, Е1, Е2 – разрешающие: запись при Е1=Е2=0(если на одном из Е "1" то это режим хранения информации), ЕZ1.EZ2 – перевод в 3-е состояние, R – установка в "0" ("1"), с приходом "1" на R вес триггера устанавливается в "0", при вводе информации на Е1, У2 и R должен быть "0". Если на EZ (любом) "1" – выходы отключаются.

ЦАП

Регистры хранения и сдвига.

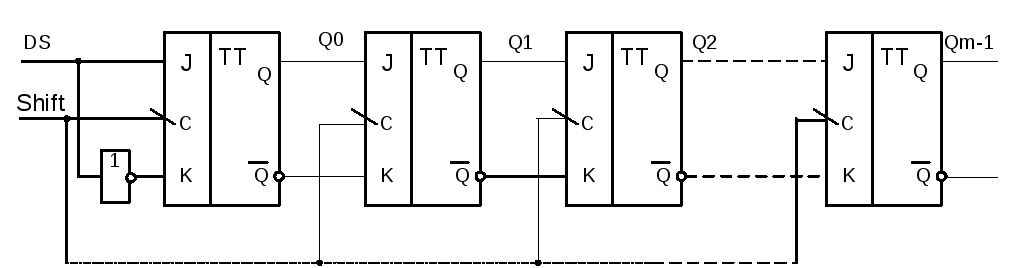

Сдвигающий, или сдвиговый регистр (shift register) это регистр, содержимое которого при подаче управляющего сигнала СДВИГ может сдвигаться в сторону старших или младших разрядов. Схема сдвигающего регистра из цепочки непрозрачных триггеров показана на рис. 4.8, а, а условное обозначение на рис.4.8, б.

а) б)

Рис.4.8. Сдвигающий регистр

Пусть на рисунке триггер Q0 – младший , Qm-1 – старший; вход каждого триггера (кроме Q0) подключен к выходу соседнего младшего триггера. Когда на все С входы триггеров поступает активный спад сигнала Shift, выход каждого триггера принимает состояние своего младшего соседа и, таким образом, информация, содержащаяся в регистре, сдвигается на один разряд в сторону старших разрядов, влево. Триггер Q0 принимает при этом состояние последовательного входа DS (data serial). Информация, поступившая на вход DS во время какого-либо такта, появится на выходе Qm-1 через m тактов.

Существенно, что в схеме использованы именно непрозрачные триггеры. Если поставить прозрачные защелки, то при активном уровне сигнала Shift все триггеры становятся прозрачными, и сигнал DS успеет пройти столько триггеров, сколько позволит длительность сигнала Shift .

Часто требуются более сложные регистры: с параллельной синхронной записью информации, реверсивные, с параллельно-последовательной записью. Такие регистры называются универсальными. Примером такого регистра служит ИМС К155ИР11. Регистр может работать в четырех режимах: параллельное занесение данных, сдвиг влево, сдвиг вправо, хранение данных.

Применения сдвиговых регистров очень разнообразны.

В арифметике сдвиг числа на один разряд влево соответствует умножению его на 2, сдвиг вправо – делению пополам.

В аппаратуре передачи данных универсальные регистры преобразуют параллельный код в последовательный и обратно. Передача данных последовательным кодом по сравнению с передачей параллельным существенно экономит число линий связи. Это покупается ценой увеличения времени обмена.

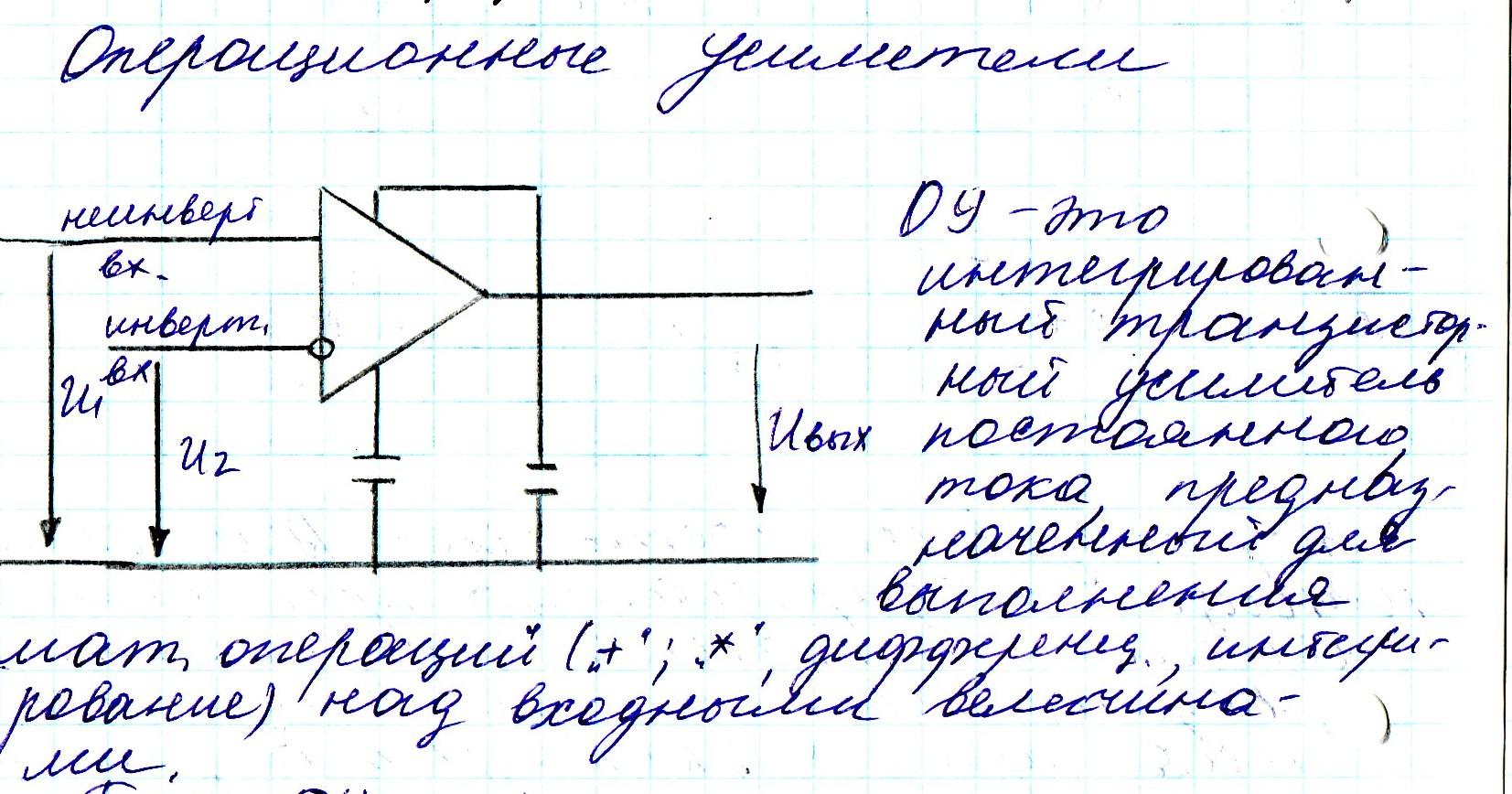

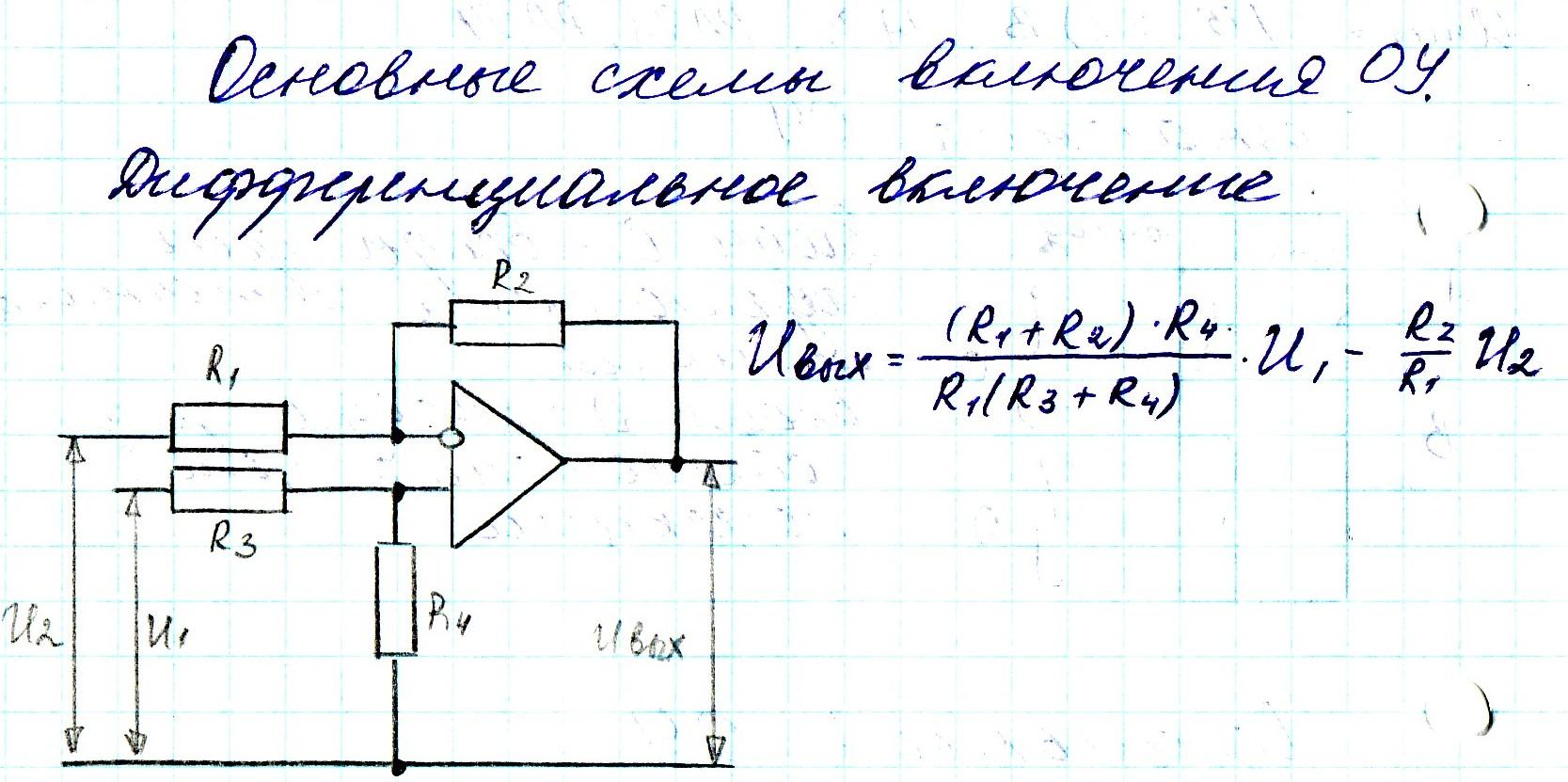

ОУ. Схемы вкл

С

умматор.

Полусумматор.

умматор.

Полусумматор.

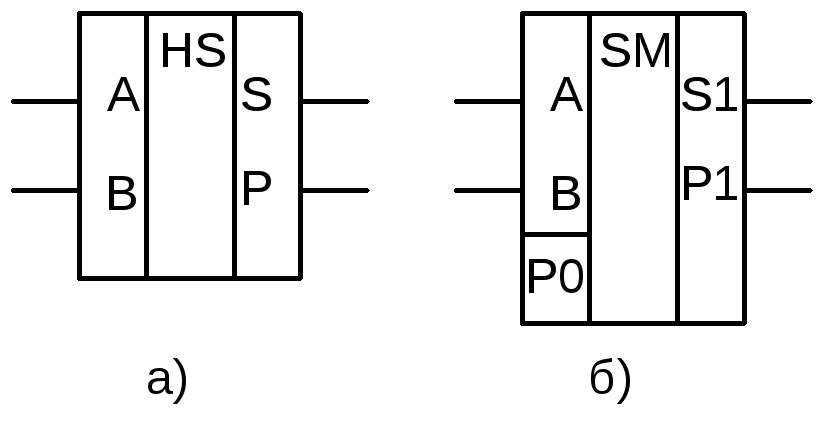

Простейшим суммирующим элементом является полусумматор. Он имеет два входа А и В и два выхода: S (cумма ) и P (перенос) (рис. 3.11,а).

Обозначением полусумматора служат буквы НS (Нalf Sum). Его работа описывается уравнениями.

П![]() роцедуру

сложения двухn

– разрядных двоичных чисел можно

представить следующим образом. Сложение

цифр А0 и В0 младшего разряда дает бит

суммы S0

и бит переноса P1.

В следующем разряде производится

сложение цифр А1, В1, и Р1, которое формирует

бит суммы S1

и перенос Р2.

роцедуру

сложения двухn

– разрядных двоичных чисел можно

представить следующим образом. Сложение

цифр А0 и В0 младшего разряда дает бит

суммы S0

и бит переноса P1.

В следующем разряде производится

сложение цифр А1, В1, и Р1, которое формирует

бит суммы S1

и перенос Р2.

Полный одноразрядный сумматор имеет три входа (рис.3.11,б): два для слагаемых А и В и один для сигнала переноса с предыдущего разряда.

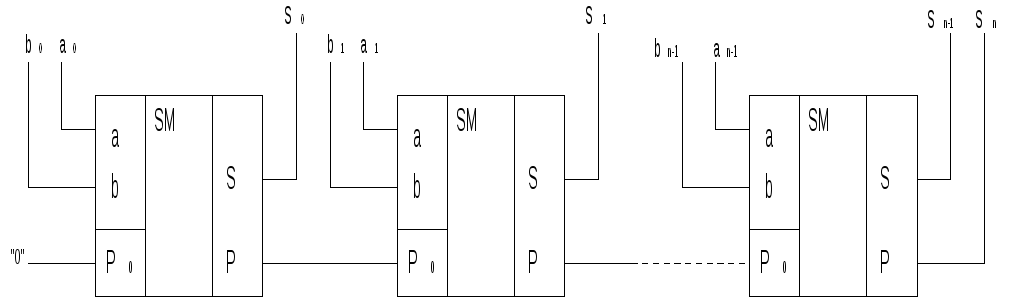

На рис. 3.12 показана схема, поясняющая принцип действия n- разрядного сумматора с последовательным переносом. Число сумматоров здесь равно числу разрядов. Выход переноса Р каждого сумматора соединен со входом переноса следующего, более старшего разряда. На входе переноса сумматора младших разрядов установлен “0”, так как сигнал переноса сюда не поступает.

Рис. 3.12 Сумматор с последовательным переносом.

Слагаемые А i и Bi складываются во всех разрядах одновременно, а перенос Р поступает с окончанием операции сложения в предыдущем разряде.

Быстродействие многоразрядных сумматоров подобного вида ограничено задержкой переноса, так как формирование сигнала переноса на выходе старшего разряда не может произойти до тех пор, пока сигнал переноса младшего разряда не распространится последовательно по всей схеме.

Время переноса можно уменьшить, вводя параллельный перенос, для чего применяют специальные узлы – блоки ускоренного переноса. Они имеют достаточно сложную схему даже для n = 4 и с увеличением числа разрядов сложность настолько возрастает, что изготовление их становится нецелесообразно.

В виде отдельных микросхем выпускаются одноразрядные, двухразрядные и четырехразрядные сумматоры. В семействе ТТЛ это микросхемы соответственно К155ИМ1, ИМ2 и ИМ3.