- •1.Система счислений

- •1.2.Предоставление данных в 2 формате.

- •1.3. Арифметические операции.

- •1.4.Логические операции.

- •2.1. Oбщая организация эвм. Организация по фон Нейману и Гарвардская.

- •2.2. Структурная блок схема пэвм-состав

- •2.3. Понятие чипсета системной платы

- •2.4.Общая шина, характеристика, назначение, разрядность

- •3.4 Струкурная блок-схема. Назначение блоков.

- •3.5 Блок шинного интерфейса. Состав. Назначение регистров cs, ds,ss,es, ip.

- •3.6. Понятие логического и физического адреса памяти (сегмент-смещение).

- •3.9.Назначение регистра флагов. Состав.

- •3.11. Алгоритм выполнения команды процессором.

- •3.12. Способы адресации данных. Базовая, индексная, базово-индексная.

- •4 .Память.

- •4.1 Память. Назначение. Классификация.

- •4.2. Внутренняя память. Классификация. Назначение

- •4.4 Rom. Назначение технологии (Колесниченко гл. 7,9). Bois.

- •4.3. Dram. Организация. Назначение ras, cas. Понятие «тайминга»

- •4.5 Cmos. Назначение. Основные функции (Колесниченко гл.31). Настройки cmos Setup.

- •4.6. Sram. Назначение. Организация. Режим работы.

- •4.7. Логическое распределение оп ( основная, расширенная, дополнительная).

- •4.8. Назначение драйверов emm386. Exe и himm.Sys.

- •5Ввод/ Вывод

- •5.2. Системные ресурсы. Понятие интерфейса. Назначение контролера

- •5)Назначается высокоскоростного канал dma

- •6)Адрес контроллера

- •7)Адрес dram,куда данные должны перейти

- •5.3 Прерывание

- •Шаги которые выполн.Привыполнение прерыв.

- •Приоритеты бывают 2 вида:

- •5.4. Алгоритм выполнения команды int Шаги которые выполн.Привыполнение прерыв.

- •5.5. Контролер прерываний. Структурная схема.

- •5.6 Алгоритм выполнения аппаратных прерываний. Работа контролера 8259.

- •Шаги которые выполн.Привыполнение прерыв.

- •5.7. Dma. Назначение. Структурная схема контролера

- •6.1. Отказоустойчивые системы. Принципы построения.

- •Система контроля и диагностики

- •6.3. Аппаратные средства контроля. Контроль по чету нечету.

- •6.4.Аппаратные средства контроля. Код Хемминга.

- •6.5. Аппаратные средства контроля. Crt.

- •6.6. Аппаратно-программные средства контроля. Post

3.4 Струкурная блок-схема. Назначение блоков.

1)Устройство шинного интерфейса – преобразование логического адреса в физический и согласования процессора с общей шиной(буфер адреса буфер данных)

2)Операционное устройство – РОНы ,алу(регистр флагов F хранит текущее состояние процессора)

3)Устройство управление – предназначено для того, что бы производить управление на микрокомандном уровне.(принимает и выдает из шины управления управляющие сигналы).

4)6-байтный буфер(очередь команд) – хранит команду из памяти,считанную из оперативной памяти.

3.5 Блок шинного интерфейса. Состав. Назначение регистров cs, ds,ss,es, ip.

Назначение блока шинного интерфейса – предназначен для преобразования логического адреса в физический.

Конструкция логического адреса состоит:

1)Сегментов

2)Смещения

Устройство шинного интерфейса:

CS - командный блок (хранит только комнанды(адрес смещения в котором хранятся команды)

SS – стек блок (хранит адрес стекового сегмента. Стек – область памяти для хранения данных и состояния процессора на момент выполнения программы)

DS – блок данных (определяет адрес сегмента, где хранятся данные)

ES- регистр дополнительного сегмента (для данных)

IP – для хранения смещения команд адреса памяти, где находятся команды.

Сегментные регистры CS, DS, SS, ES, FS, GS служат для хранения значений, интерпретация которых зависит от режима работы процессора.

3.6. Понятие логического и физического адреса памяти (сегмент-смещение).

Логический адрес адресует ячейку памяти. Состав:

Сегмент:Смещение

Сегмент(seg) организует определенный участок памяти, а смещение(offset) ячейку внутри этой памяти.

Логический адрес находится в процессоре в регистрах: CS, DS, SS, ES.

На выходе из процессора – физический адрес.Физический адрес поступает в шину адреса.а потом в память.

Max FFFF0 – физический адрес.

53D0:7F00 - логический

53D00

+ 7F00 = 5BC00 - физический

Операционное устройство. Состав.

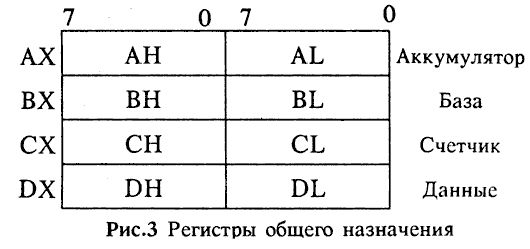

Операционное устройство состоит из РОН(регистров общего назначения)

AX,DX,CX,DX - могут быть представлены независимыми однобайтными регистрами.

AX – аккумулятор(умножение, деление, ввод – вывод слов)

BX – базовый регистр (адресация по базе памяти)

СX – счетчик (подсчет циклов и элементов цепочек)

DX – регистр данных (умножение, деление слов(результат) косвенно – ввод, вывод – (результат))

Структура команды POH.

3.9.Назначение регистра флагов. Состав.

Регистр флагов – предназначен для хранения текущего значения процессора.

Ариф./логич. флаги, меняющиеся по результату выполненной ариф-логич. операции.

Mov Ax Dx – не влияет на флаги(пересылка)

Add Ax Bx – влияет на флаги.

Регистр флагов:

(Арифм./логич. флаги)

CF – флаг переноса. Фиксирует значение переноса(заема),возникающего при сложении(вычитании) байтов или слов,а так же значения выдвигаемого бита при сдвиге операций.

PF

- флаг четности(паритета).Фиксирует

наличие четного количества единиц в

младшем байте результата операции, и

используется для контроля правильности

передачи данных.

AF

– флаг вспомогательного переноса.

Фиксирует перенос(заем) из младшей

тетрады (т.е из бита

в старшую (при сложении\вычитании).

ZF

– флаг нуля. Сигнализирует

о получении нулевого результата

операции.

SF

- флаг знака. Фиксирует

знаковый бит(7 или 15).

OF

- переполнение

в старшую (при сложении\вычитании).

ZF

– флаг нуля. Сигнализирует

о получении нулевого результата

операции.

SF

- флаг знака. Фиксирует

знаковый бит(7 или 15).

OF

- переполнение

DF- флаг направления.(команды LTD и STD) от меньших адресов или от больших.

Флаги управления:

IF –флаг прерывания (команда CLI b STI) запрещает маскировать прерывания IF=0 на внешние прерывания процессор не реагирует)

TF – флаг транссировки Переходит в командно-тестируемый режим (пошаговый с прерыванием)

Структура команды INTEL.

Код Оператор Оператор Оператор

Операции 1 2 3

Адрес данных, Адрес 2

с которыми

будут работать

Ассемблеры INTEL двухадресовые.

Длина команды – 1-6 байт.

Результат операции помещается в первый операнд.

Виды адресации:

-прямая

-память(косвенная)

сегмент:смещение ,указывается только смещение, для адреса данных используются сегментные регистры – DS,SS,ES смещение может указываться как базовое, индексное и базово-индексное.

|

Add

|

[Bx+Si]

, |

Ax |

|

Код операции |

Адрес памяти(по умолчанию DS) |

Содержимое

|

DS [Bx+Si]

Сюда запоминаем