- •5.1.Функции системы прерывания и общие решения по реализации

- •7. Организация системы прерывания в pdp 11

- •Глава 8. Организация виртуальной памяти

- •8.2. Основные задачи виртуальной памяти

- •8.3. Страничная организация виртуальной памяти

- •8.3.1. Страничная организация памяти

- •8.3.2. Виртуальная память на основе таблицы математических страниц

- •8.3.3. Упрощенная схема виртуальной памяти на основе таблицы физических страниц

- •Глава 9. Организация кэш-памяти

- •9.1. Назначение и общая схема подключения кэш-памяти

- •9.2. Системы адресации кэш-памяти

- •9.3. Режимы работы кэш-памяти

- •9.4. Иерархическая структура кэш-памяти и средства управления кэш-памятью

Министерство образования и науки Российской Федерации

КАЗАНСКИЙ ГОСУДАРСТВЕННЫЙ ТЕХНИЧЕСКИЙ УНИВЕРСИТЕТ

им. А.Н. ТУПОЛЕВА

В.М. Трусфус

Организация ЭВМ и систем

Программные модели процессоров и управление

периферийными устройствами

Конспекты лекций

Казань 2009

1-я неделя Лекция 1 (Вводная),

Назначение курса. Программа курса (количество лекций 17, практических занятий 17, содержание и количество лабораторных работ (4), тематика и особенности выполнения курсовой работы.

2-я неделя Лекция 2.

ЭВМ. Основные понятия.

ЭВМ (компьютеры) в настоящее время являются основными средствами реализации информационных технологий. При помощи ЭВМ осуществляют сбор, обработку, хранение и передачу информации, представленной в дискретной форме. Очень часто информационные технологии, ориентированные на обработку данных в дискретной форме, называют компьютерными технологиями.

Структурно ЭВМ представляет собой взаимодействующую совокупность двух компонентов: системы аппаратных средств (hardware) и системы программного обеспечения (software). Для предусмотренного функционирования ЭВМ в ней должны протекать определенные процессы. Управление этими процессами может быть реализовано как аппаратными, так и программными средствами.

Как правило, для управления ЭВМ используется иерархическая система аппаратно-программных решений. При этом на самом нижнем уровне управления используются аппаратные средства, на верхних уровнях – программные.

Основой системы программного обеспечения является операционная система (ОС). ОС может наращиваться программными инструментальными средствами, сервисными программами (утилитами) и другими системными программами.

Аппаратные решения, как правило, приводят к уменьшению временных затрат, но программные решения более динамичны в реализации. Развитие программных средств требует непрерывного увеличения объема памяти ЭВМ и существенного увеличения быстродействия, как памяти, так и процессора, стимулируя непрерывное совершенствование аппаратных средств.

Для уменьшения временных затрат часть программных решений заменяется на аппаратные, поэтому граница "полномочий" программных и аппаратных средств в разных моделях ЭВМ может не совпадать.

Центральным устройством ЭВМ является процессор. Процессор - это программно-управляемое устройство обработки информации. Обработка информации производится в соответствии с алгоритмом обработки.

Алгоритм - это точное предписание, определяющее порядок действий для достижения результата. Программа - это алгоритм обработки информации в грамматике конкретного языка программирования.

Программу, написанную на машинном языке, называют исполняемой программой или машинным кодом. Среди языков программирования имеется язык программирования, ориентированный на человека, но максимально приближенный к машинному языку. Это язык ассемблера или ассемблер (assembler).

Программы в машинных кодах получают путем трансляции (перекодировки) соответствующих программ, написанных на языках высокого уровня или на ассемблере. Трансляция производится специальными программами – компиляторами или интерпретаторами. Компиляторы выполняют перекодировку команд языка высокого уровня в машинные исполняемые коды до выполнения программы. Интерпретаторы используются реже. В этом случае перекодировка команд языка высокого уровня в машинные команды производится с использованием аппаратуры процессора в процессе выполнения программы.

Обычно программная совместимость сочетается с конструктивной совместимостью. Соблюдение программной совместимости усложняет модификацию и эволюцию ЭВМ, удорожает модели семейства, но ее придерживаются в силу сложности разработки программ.

Семейство ЭВМ - это ряд программно совместимых моделей ЭВМ различной производительности и стоимости. Обычно, кроме программной совместимости, для всех моделей семейства соблюдается и конструктивная совместимость. Это позволяет всем моделям семейства использовать и общий парк периферийных устройств. Программно-совместимые ЭВМ могут выпускаться не только одной фирмой.

По словам разработчиков первого семейства программно-совместимых моделей IBM/360, создание семейства стало возможным благодаря осознанию того, что в ЭВМ полезно различать две независимые структуры: физическую и логическую.

Логическая структура - это структура ЭВМ с точки зрения пользователя и программного обеспечения. Это набор и структура команд, форматы данных, регистры и т.д.

Физическая структура - это то, что видит в ЭВМ инженер по электронике, разработчик микросхем.

Логическая и физическая структуры ЭВМ могут не совпадать. Осознание возможности независимости логической и физической структур позволило специалистам IBM в рамках единой логической структуры создать ряд моделей ЭВМ с различной производительностью и физической структурой, что и обеспечивало их программную совместимость.

В настоящее время часто вместо терминов логическая и физическая структуры используют термины, соответственно, архитектура и микроархитектура.

Многоплатформенность программных продуктов

Платформой называется сочетание аппаратных средств ЭВМ и операционной системы. Многоплатформенность означает наличие программных продуктов, идентичных на уровне исходных текстов для разных программно-несовместимых ЭВМ.

Многоплатформенность программных продуктов направлена на решение проблем программной несовместимости при организации сложных многомашинных информационных систем, допускающих наращивание вычислительной мощности.

Традиционная классификация ЭВМ

Это первое поколение ЭВМ - это ЭВМ на электронных лампах. Возможности ламповых ЭВМ были ограничены из-за эксплуатационных параметров ламповых элементов.

Второе поколение ЭВМ – это ЭВМ на полупроводниковых дискретных компонентах.

Появление ЭВМ третьего поколения, а конкретно семейства IBM/360, стало этапным. Это было семейство программно-совместимых ЭВМ, производительностью от 10 тысяч операций для младших моделей и до одного миллиона – для старших. Эту тенденцию нарушило появление нового класса ЭВМ – миникомпьютеров или мини-ЭВМ. Главной особенностью мини-ЭВМ была их ориентация не на вычисление, а на управление. Это были программируемые устройства управления – контроллеры. Слово "мини" в названии класса ЭВМ означало скорее не "миниатюрная", а "минимальная" (ограниченная, урезанная). В мини-ЭВМ урезывались вычислительные возможности (набор арифметических команд и точность вычисления). Для мини-ЭВМ была разработана своя упрощенная архитектура. С появлением мини-ЭВМ модели традиционных семейств ЭВМ с "нормальными" вычислительными возможностями получили название «ЭВМ общего назначения».

Появился новый класс ЭВМ на основе микропроцессоров – микро-ЭВМ.

Микро-ЭВМ ориентированы на управление объектами с малым количеством управляемых параметров. По этой причине основное "урезание возможностей" в микро-ЭВМ сводилось к ограничению по количеству точек управления и, возможно, разрядности данных.

Успехи микроэлектроники создали условия для возникновения нового продукта массового применения: ЭВМ типа "one on one - один для одного", т.е. персонального компьютера ПК (PC – Personal Computer).

РС появились в результате эволюции микро-ЭВМ после перехода элементной базы от интегральных схем с малой и средней степенью интеграции к большим и сверхбольшим интегральным схемам. Архитектура РС имеет существенные отличия от архитектуры микро-ЭВМ.

Структуры ЭВМ

ЭВМ определяется как программно-управляемое устройство обработки данных в числовой форме. Имеется несколько программных моделей (концепций реализации вычислений на ЭВМ). В большинстве современных ЭВМ реализована классическая концепция, предложенная ученым фон Нейманом

Это архитектура ЭВМ, поддерживает следующие принципы:

двоичного кодирования,

программного управления,

однородности памяти,

адресуемой памяти.

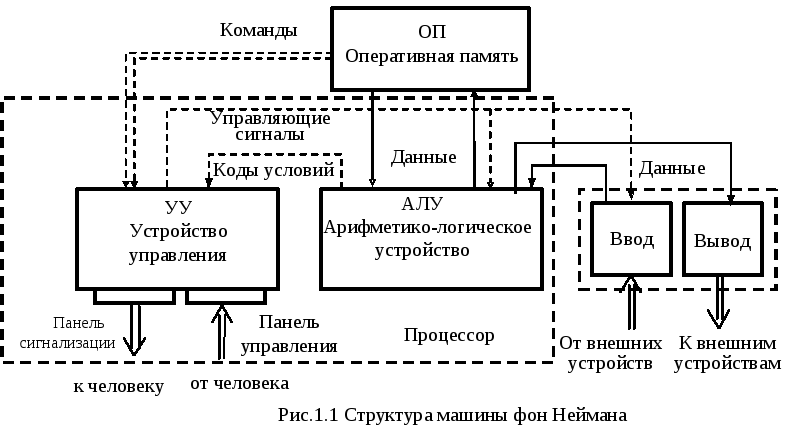

Классический вариант этой машины по концепции фон Неймана должен содержать следующие блоки (рис.1.1.):

оперативную память,

арифметико-логическое устройство,

устройство управления,

устройства ввода-вывода,

внешние запоминающие устройства.

Оперативная память предназначена для хранения, как команд программы, так и данных. По концепции фон Неймана принципиально важно, чтобы команды и данные в оперативной памяти были неразличимы. Это позволяет иметь общую оперативную память с единой адресацией, что упрощает программирование ветвлений программ и более эффективное использование ячеек памяти.

Блок устройства управления предназначен для формирования сигналов управления (микроопераций) для выполнения команд программы. Основными блоками устройства управления являются: регистр указателя адреса очередной команды (счетчик команд), регистр команд, блок дешифрации команды, блоки формирования микроопераций, регистр состояния (программы).

Команды поступают из оперативной памяти на регистр команд устройства управления по шинам передачи команд.

Для непосредственной связи с человеком устройство управления содержало пульт управления и панель сигнализации. В классической схеме ЭВМ предусмотрены устройства ввода и вывода. К устройствам ввода/вывода относятся устройства хранения информации вне ЭВМ и переноса на другие ЭВМ. Внешними устройствами могут быть устройства:

внешней памяти,

ввода/вывода

Многомашинные комплексы.

В многомашинных комплексах каждая ЭВМ использует свою операционную систему, а одна из них – дополнительно программу организации совместной работы ЭВМ в комплексе. Схема двухмашинного комплекса на основе моделей IBM/360 представлена на рис.1.2.

Каждая модель комплекса содержит процессор, модули памяти и систему ввода/вывода (каналы в/в). Обмен данными производится через систему ввода/вывода.

Многомашинные комплексы в настоящее время определяются как асимметричные, слабосвязанные многопроцессорные системы; системы с неоднородным доступом к памяти (NUMA – Non-Uniform Memory Access).

Многопроцессорные системы

Многопроцессорные системы определяются как симметричные мультипроцессорные системы (SMP системы – Summitries Multiprocessor). Все процессоры системы работают в едином виртуальном и физическом пространстве оперативной памяти. Любой из процессоров может обслуживать внешние прерывания. Это сильно связанные системы.

Эволюция режимов работы ЭВМ

На формировании структур ЭВМ, кроме особенностей развития элементной базы и смены областей использования, значительный след оставила эволюция их режимов работы. Основными режимами были следующие:

непосредственного доступа,

однопрограммной пакетной обработки,

мультипрограммной пакетной обработки,

коллективного доступа,

клиент-сервер.

Кластерные структуры.

Это наиболее перспективные структуры эксплуатации современных ЭВМ.

Кластер – это совокупность объединенных компьютеров (узлов), управляемых и используемых, как единое целое. Каждый узел кластера может быть однопроцессорным или многопроцессорным.

Основными целями кластера являются обеспечение:

высокой доступности и отказоустойчивость,

распределением нагрузки,

повышения производительности.

Высокая доступность и отказоустойчивость обеспечивается избыточными процессорами, гарантирующими доступность при отказе отдельных серверов.

Grid системы. Название системы Grid трактуется как решетка (сеть). Имеется в виду об"единение вычислительных кластеров разных фирм в сеть, с использованием интернет-технологий.

Вопросы и/или темы для проверки:

Программная совместимость ЭВМ.

Физическая структура ЭВМ.

Характеристика режимов обработки

Основной признак смены поколения ЭВМ.

Особенности мини-ЭВМ.

Особенности микро-ЭВМ.

Особенности и предназначение PC.

Основные блоки устройства управления.

Определение кластера.

Определение Grid-системы

3 неделя Лекция 3

Программная модель процессора

Программная модель процессора – это базовая совокупность систем и характеристик процессора, видимая программистам, работающим на нижних, "машинных" уровнях программирования, например на языке ассемблера.

Обычно к программной модели процессора относят:

виды используемых структур памяти по принципам размещения и поиска информации,

организацию оперативной памяти,

структуру и типы команд,

состав программно-доступных регистров,

режимы адресации,

структуру и типы данных,

наборы реализованных операций.

Кроме этого в программную модель включают ряд схемно-программных систем, видимых программистам, работающим на нижних уровнях программирования.

Это:

система прерывания,

организация ввода/вывода,

организация памяти.

Виды используемых структур памяти по принципам размещения и поиска информации

В традиционных ЭВМ используется иерархическая система памяти. Непосредственно в процессоре могут быть интегрированы регистры общего назначения (РОНы), первые ступени кэш-памяти, дополнительные устройства памяти, иногда – программно недоступные. Это устройства сохранения адресов возврата, аппаратные таблицы переадресации, буферы предсказаний ветвлений и т.д.

Основной памятью, на работу с которой ориентирован процессор, является оперативная память. Остальные системы памяти для процессора, как правило, являются внешними устройствами.

Особый статус имеют уровни кэш-памяти. Это элементы системы "оперативная память – процессор"

По принципам размещения и поиска информации устройства оперативной памяти разделяются на:

адресные,

ассоциативные,

стековые.

Адресная память

В адресных устройствах памяти массив элементов хранения информации разбивается на отдельные нумерованные последовательности. Номер конкретной последовательности является ее адресом, по которому происходит обращение для записи или чтения информации. Это модель плоской (двухкоординатной) памяти. Иногда используются наборы плоских устройств памяти для получения структурированных систем памяти.

Обычно для хранения информации в ЭВМ используются двоичные элементы (хранимые значения – биты), а минимально адресуемой последовательностью бит является байт.

Байт – это количество бит, необходимое для кодирования символов в используемых стандартных кодах. В настоящее время байт – это 8 бит.

Байты укрупняются в слова. Для РС и мини-ЭВМ слово – это два байта, для полноразрядных ЭВМ корпорации IBM – четыре байта. В качестве программных объектов могут использоваться биты, байты, слова и более крупные объекты, кратные двоичной степени байта.

Ассоциативная память

В ассоциативных системах памяти массив элементов хранения информации, как и в адресных системах, разбивается на отдельные последовательности, но нумерация последовательности необязательна.

Кроме функций записи и хранения, в таких системах памяти аппаратно реализуются функции ассоциативного поиска информации. В простейшем случае – это поиск информации по совпадению входного "эталона" –ключа с частью последовательности хранимой информации. Результаты ассоциативного поиска используются в операциях чтения или записи для поиска искомых строк данных.

Ассоциативный поиск реализуется сравнением входной информации со всеми хранимыми объектами (байтами, словами и т.д.).

Стековая память

Стековая память –это список со стратегией работы "последний вошел – первый вышел". Стековая память обычно реализуется на основе обычной линейной адресной памяти с использованием специального регистра – указателя стека (SP). Для стековой памяти определены две операции: занесение единицы данных в стек и удаление единицы данных из стека.

Организация оперативной памяти

Оперативная память – это основная память, на работу с которой ориентирован процессор, точнее программа, выполняемая процессором. Это адресная память.

Множество адресов, которые могут использоваться в командах процессора, составляют его адресное пространство.

Современные ЭВМ ориентированы на работу с "наращиваемым" объемом физической памяти. При этом:

адресное пространство программиста и памяти могут не совпадать,

размещение программы и данных в физической памяти может не совпадать с их размещением по адресам в адресном пространстве прогрпммиста,

прикладные программы вместо прямой адресации физической памяти используют обращение к некоторой модели (отображению) памяти,

обращение к физической памяти производится при помощи диспетчера памяти, согласующего модель математической памяти с динамикой распределения программ и данных в физической памяти.

Диспетчер памяти может быть реализован программно или схемно-программно. В последнем случае говорят о реализации виртуальной памяти.

Размер адресного пространство процессора определяется разрядностью адресных шин, которая ограничена разрядностью процессора. Это случай плоской модели математической памяти.

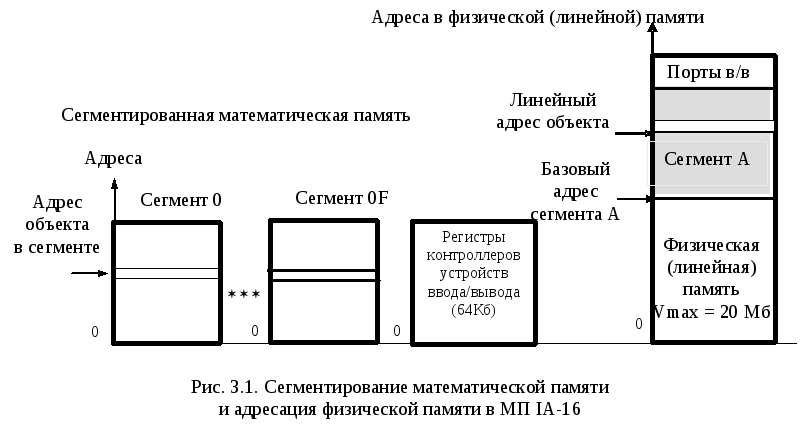

Для снятия этого ограничения некоторые процессоры, например МП Intel, допускают использование множества адресных пространств. В этих случаях говорят о структурированной (сегментированной) математической памяти.

Использование сегментированной памяти увеличивает адресное пространство процессора, но усложняет адресацию. В сегментированной памяти адреса операндов и команд задаются вектором: указанием используемого сегмента (например, через базовый адрес сегмента в линейной памяти) и адреса данных в сегменте. Но, так как оперативная память остается не сегментированной (линейной), требуется пересчет сегментированного адреса в линейный адрес. Эта процедура называется трансляцией сегментов.

Структура и типы команд

При компиляции программ производится декомпозиция процедур программ до уровня операций обработки двух или одного операндов. В первом случае команда является двухместной, во втором – одноместной.

В любом случае команда должна задавать операцию и операнды. Обычно операция задается номером (кодом) операции во множестве операций, определенных для операционного устройства. Если операнды, используемые в операции, являются результатами ранее выполненных операций (тип операндов – переменная), то они задаются номерами (адресами) зарезервированных для них ячеек памяти. Если операнд известен до выполнения операции, то он может задаваться в команде своим значением (непосредственный операнд).

В случае двухместной операции команда должна задавать

1. операцию,

2. адрес или значение первого операнда,

3. адрес или значение второго операнда,

4. адрес сохранения результата,

5. адрес следующей команды (или двух альтернативных адресов команды для реализации ветвлений).

Задание операции

Операция задается полем кода операции. По этому номеру коду или выбирается специализированное исполнительное устройства, или универсальное исполнительное устройство настраивается на заданный вид обработки. Возможны комбинации этих решений.

Кроме исполняемой операции, код операции часто задает формат и тип обрабатываемых данных. Под форматом здесь понимается размерность операндов (байт, слово, двойное слово и т.д.), а под типом – тип арифметики (целочисленные операции, с плавающей точкой, векторные операции и т.д.).

Поле адресов

Если все перечисленные адреса задаются явно (соответствующими полями), то команда имеет четырех- или пяти-адресную структуру. Два альтернативных адреса следующей команды необходимы для реализации ветвлений.

-

Код операции

Адрес 1

Адрес 2

Адрес 3

Адрес 4 (4,5)

Структура четырехадресной команды

Четырехадресная структура определяет необходимый набор адресов для задания двухместной операции. Но все указанные адреса задавать в явном виде необязательно. Здесь возможны различные варианты.

Трехадресная система команд

Адрес следующей команды связывает отдельные команды в программу, определяющую всю последовательность операций, т.е. процедуру обработки. Но этот адрес можно не задавать явно в каждой команде. Вместо этого, команды программы можно располагать в ячейках памяти в той последовательности, в которой они должны выполняться, а в схеме процессора предусмотреть специальное устройство – счетчик команд (указатель команд), назначение которого – вычисление адреса следующий команды. Команда становится трехадресной. Вычисление адреса следующей команды производится путем прибавления длины выполняемой команды (например, в байтах) к её адресу. Но отдельные смежные фрагменты программы могут размещаться и в несмежных участках памяти. Для их соединения в единую программу используются команды передачи управления, содержащие указание на начало следующего линейного участка программы.

Например, команда безусловного перехода:

Jmp (переход) <адрес передачи управления>.

В адресной части этих команд указывается адрес первой команды следующего фрагмента программы. Команды передачи управления могут быть и условными, когда передача управления производится с учетом кода условия, хранящегося в регистре состояния ЭВМ.

Команды условной передачи управления позволяют разрабатывать разветвляющиеся и циклические программы. Разновидностью команд передачи управления являются команды передачи управления с возвратом (команды переходов на подпрограммы). При выполнении этих команд перед передачей управления на подпрограмму запоминается адрес возврата (содержимое счетчика команд до передачи управления). Адрес возврата используется другой разновидностью команд передачи управления – командами выхода из подпрограммы. Таким образом, переход к трехадресной системе команд сопровождается:

отказом от независимости в расположении отдельных команд в программе,

введением в состав процессора специального устройства (счетчика команд), вычисляющего адрес следующей команды,

введением в состав команд процессора специальных команд для задания точек нарушения выполнения команд в естественном порядке и указания адресов переходов. Это команды задания условного и безусловного переходов (с возвратом или без возврата).

Двухадресная система команд

В качестве адреса результата операции можно использовать адрес одного из исходных операндов. При этом результат операции записывается "поверх" одного из операндов, значение которого теряется, но команда становится компактнее .

Это двухадресные команды. В двухадресных командах один адрес рассматривается как адрес-источник, а другой – как адрес-приемник.

Естественно, что в этих командах только операнд-источник можно задавать непосредственным значением.

Неизбежная потеря значения одного из операндов при использовании двухадресных команд потребовала введения в состав команд процессора команды пересылки (копирования) объекта-источника в ячейку приемника. Примером такой команды может служить команда пересылки MOV:

MOV А1, А2.

Необходимость такого копирования данных в некоторых случаях значительно удлиняла программный код.

Одноадресная система команд

Дальнейшее уменьшение количества адресов, явно заданных в команде, приводит к одноадресной структуре команд.

В процессоре с одноадресной структурой команд предусматривается специальный регистр – аккумулятор. Это регистр, в котором находится один из операндов, и в который записывается результат операции (поверх исходного операнда).

Возможно и дальнейшее упрощение команд. Это безадресная система команд. Такая система существует, но она ориентирована на использование стековой памяти. В этих командах указываются или код операции или данные. Одни команды загружают данные в стек или выводят из стека результаты, другие команды задают операции над данными из вершины стека. Такая система команд использовалась в некоторых калькуляторах, но широкого применения не нашла.

Дальнейшее совершенствование структуры команд связано с отставанием роста быстродействия памяти по сравнению с ростом быстродействия процессора. Это отставание стало серьезным препятствием в развитии вычислительной техники.

Статистика обращений к памяти показала, что на каждое обращение по записи приходится, в среднем, 13 обращений по чтению, Это означает, что каждый полученный в процессоре результат или выбранный из памяти операнд с большой вероятностью будет использоваться в последующей команде.

Следовательно, временные потери процессора на ожидание данных из памяти можно уменьшить введением в состав процессора не одного аккумулятора, а множества регистров для сохранения и повторного использования данных. Появление дополнительного множества регистров в процессоре и необходимость их адресации существенно повлияли на дальнейшее развитие структуры команд.

Дальнейшее усовершенствование системы команд привело к усложнению системы адресации ячеек оперативной памяти. Адреса оперативной памяти стали задавать не явно, а компонентами. Для хранения компонентов адреса стали использовать те же регистры. Появилась дополнительная индексная (адресная) арифметика для вычисления адреса по компонентам. Дополнительные регистры стали использоваться для хранения как операндов, так и компонентов адреса. А регистры получили название "регистры общего назначения" ( РОНы).

Многие фирмы (Intel,DEC) для гибкости системы программирования стали использовать множество формул (режимов адресации) для вычисления адресов.

С появлением РОНов команды снова стали двухадресными. Один – адрес оперативной памяти, другой – РОНа, или оба адреса – номера используемых РОНов.

В случае использования РОНов команды, в зависимости от расположения исходных операндов, разделяются на типы: регистр-регистр, регистр-память.

Команды типа регистр-регистр являются наиболее компактными по размерам и быстрыми по выполнению. Они используют короткие адреса и независимы от задержек при обращении к памяти. Как исключение, некоторые ЭВМ (например, IBM/370) сохранили команды и типа память-память.

Кроме РОНов, современные процессоры содержат ряд других программно доступных регистров, которые образуют регистровый файл процессора.

Режимы адресации

С появлением РОНов появилось два типа команд:

команды структуры регистр/регистр (r/r): Коп R1, R2,

команды структуры регистр/память (r/m): Коп R1, М2,

где:

R1, R2 – номера (адреса) РОНов.

M2 – полноразрядный адрес оперативной памяти.

Первый тип команд по отношению к данным является двухадресным (задаются адреса двух РОНов), но по отношению к памяти – безадресным.

Второй тип команд по отношению к данным тоже двухадресный, но по отношению к памяти – одноадресный (первый адрес является адресом РОНа).

Адреса памяти в современных процессорах задаются в большинстве случаев отдельными компонентами с указанием (явно или "по умолчанию") способа вычисления адреса. Способы вычисления адреса определяются режимами адресации. Задание операнда в команде его непосредственным значением (непосредственный операнд), прямым значением адреса (непосредственный адрес) или номером РОНа – это частные случаи режимов адресации.

Адреса операндов в командах задаются через компоненты по двум причинам:

1. для уменьшения разрядности поля адреса в команде,

2. для упрощения процедур обработки массивов.

Вопросы и/или темы для самопроверки:

Двухместные операции.

Назначение четвертого адреса в четырехадресной команде.

Основные преимущества одноадресной системы команд.

Причины использования задания адреса в сегменте тремя компонентами.

Причины введения в состав процессора РОНов.

4 неделя. Лекция 4.

Программная модель процессоров семейства PDP-11

Отображение оперативной памяти

Семейство ЭВМ PDP-11 – это первый ряд 16-битных программно совместимых моделей ЭВМ от микро до супер-мини. Для многих последующих высокопроизводительных ЭВМ архитектура PDP-11 стала стартовой. Корпорация DEC, развивая эту архитектуру, стала лидирующей на рынке мощных 64-битных рабочих станций на базе VAX-кластеров и моделей МП серии Alpha.

Максимальный размер математической памяти моделей ЭВМ PDP-11 – 216 = 65 536 байт (64 Кбайт) или 215= 32 768 двухбайтных слов (32 К). Но максимальный размер физической памяти в четыре раза больше и может достигать до – 218 = 262 144 байта (256 Кбайт) или 131 072 слова (256 К).

Нумерация бит в байтах и словах – обратная (с младших разрядов), слова и двойные слова адресуются по номеру байта в слове (двойном слове).

Структура и нумерация бит в байте и адресация слов в физической памяти представлена на рис. 4.1.

|

|

Слова |

|

|

Байты |

| ||||

|

номера байт |

15 |

8 |

7 |

0 |

номера байт |

|

7 |

0 |

номера байт |

|

1 |

старший |

младший |

0 |

|

младший |

0 | |||

|

3 |

старший |

младший |

2 |

|

старший |

1 | |||

|

5 |

старший |

младший |

4 |

|

* * * |

| |||

|

7 |

старший |

младший |

6 |

|

* * * |

| |||

|

* * * |

* * * |

|

|

* * * |

| ||||

|

65 533 |

старший |

младший |

65 532 |

|

* * * |

| |||

|

65 535 |

старший |

младший |

65 534 |

|

* * * |

| |||

|

|

|

|

|

|

* * * |

| |||

|

|

|

|

|

|

* * * |

| |||

|

|

|

|

|

|

младший |

65 534 | |||

|

|

|

|

|

|

старший |

65 535 | |||

|

Рис. 4.1. Структура и адресация бит в байте и слов в памяти | |||||||||

Трансляция математических адресов производится с помощью диспетчера памяти (вариант реализации виртуальной памяти). Превышение объема физической памяти над математической памятью позволяет реализовать многопрограммные режимы работы.

Особенностью адресации памяти является то, что в пространство адресов математической и физической памяти отображаются не только адреса ячеек памяти, но и все пространство программно доступных регистров устройств ввода/вывода (номера портов).

Под адреса портов выделены 4 Кбайт старших адресов пространства памяти.

Регистровый файл

В регистровый файл входят:

регистры общего назначения (РОНы),

регистр слова состояния процессора.

Регистры общего назначения (РОНы)

Это – восемь шестнадцатибитных регистров, шесть из них используются только при явной адресации, два (R6 и R7) специализированы и, кроме явной адресации, могут использоваться по умолчанию.

R6 – шестнадцатибитный регистр указателя аппаратного стека SP (Stack Pointer). Используется аппаратурой процессора при прерываниях и передаче управления для сохранения адреса и состояния программы.

R7– шестнадцатибитный счетчик команд PC (Program Counter). Вычисляет адрес следующей команды. Доступен программам пользователя по записи и чтению.

Регистр слова состояния процессора

Шестнадцатибитный регистр слова состояния процессора PS (Processor Status) (рис. 4.2) содержит поля:

Текущего и предыдущего режима работы (биты с 12 по 15 Поле задает режимы: пользователь/система. Используется механизмом защиты программ. В режиме «пользователь» запрещено использование ряда "привилегированных" команд.

Приоритет процессора (биты с пятого по седьмой). Задает приоритет процессора. Процессор может иметь приоритет от 0 до 7. Приоритет процессора используется в арбитраже системного интерфейса как уровень маскирования запросов прерывания от внешних устройств.

Бит слежения Т (Trap, четвертый бит). При включенном бите T после выполнении каждой команды (кроме RTT) производится процедура прерывания.

Четыре бита кода условий (биты с нулевого по третий):

С – "перенос",

V – "переполнение",

Z – "результат нулевой",

N – "результат отрицательный".

Коды условий используются при выполнении команд ветвления.

|

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

Текущий Режим |

Послед. режим |

|

Приоритет процессора |

T |

N |

Z |

V |

C | |||||||

|

Рис. 4.2. Структура регистра слова состояния процессора | |||||||||||||||

Структура данных

Данные представляются в двух видах: данные со знаком и данные без знака. Данные со знаком могут быть в форме с фиксированной запятой или в форме с плавающей запятой. Данные без знака – это адреса или алфавитно-цифровые символы.

Данные со знаком с фиксированной запятой – это целые числа в виде байтов, слов или двойных слов. Старший бит числа – знаковый. Отрицательные числа представлены в дополнительном коде.

Данные со знаком с плавающей запятой обрабатываются специальным сопроцессором обработки чисел с плавающей запятой (ППЗ). В ППЗ определены два формата:

одинарной точности – двойное слово: знак мантиссы (1бит), сдвинутый порядок (1 байт), мантисса (3 байта),

двойной точности – учетверенное слово: знак мантиссы (1бит), сдвинутый порядок (1 байт), мантисса (7 байт).

В обоих случаях, мантисса – это нормализованная дробь, в которой первая цифра после запятой должна быть единицей. При хранении в памяти первая цифра мантиссы является скрытым битом (всегда равным единице), не хранимым в памяти. Поэтому в двойное или учетверенное слова памяти помещаются: знак, байт сдвинутого порядка и, соответственно, два или семь байтов мантиссы. Отрицательные значения мантиссы заданы в прямом коде.

Структура команд

Существенной новацией структуры команд ЭВМ PDP-11 является всесторонне развитая система адресации и использование стека при обращении к подпрограммам и при обслуживании прерываний. Эти механизмы стали нормой для многих последующих ЭВМ различных корпораций.

По количеству адресов операндов ЭВМ PDP-11 использует безадресные, одноадресные и двухадресные команды. Основной (полный) формат имеют двухадресные команды (рис.4.3). Они содержат поля:

кода операции,

адреса операнда источника,

адреса операнда приемника.

-

15

12

11

9

8

6

5

3

2

0

Код операции

адрес источника

адрес приемника

режим

РОН

режим

РОН

Рис.4.3. Структура двухадресной команды

Код операции. Код операции задает операцию, структуру команды и размер операнда.

Двухадресные команды – это, в основном, команды работы с битами. Исключения составляют команды пересылки и две команды арифметических операций (сложения и вычитания слов в форме фиксированной запятой).

Из возможных 16 кодов для кодирования операции используются только четыре. Остальные коды используются для обозначения других дополнительных команд. Эти дополнительные форматы команд представлены на рис. 4.4.

Все рассмотренные команды являются шестнадцатибитными, т.е. занимают одно слово, но в зависимости от типов используемых адресаций они могут включать в себя дополнительные поля длиной одно или два слова. Второе и третье слова команды это или адреса, или непосредственно заданные значения операндов.

|

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

3 |

2 |

0 |

| |

|

Код операции (6 бит) |

R– источник (3 б) |

адрес приемника (6 бит) |

a | ||||||||||||

|

Код операции (6 бит) |

R– источник (3 б) |

Смещение (6 бит) |

b | ||||||||||||

|

Код операции (10 б) |

адрес приемника (6 бит) |

c | |||||||||||||

|

Код операции (13 бит) |

R– источник(3 б) |

d | |||||||||||||

|

Код операции (16 бит) |

e | ||||||||||||||

|

Код операции (8 бит) |

Смещение (8 бит) |

f | |||||||||||||

|

Рис.4.4. Дополнительные структуры команд |

| ||||||||||||||

Адресация операндов

В двухадресных командах первый адрес после кода операции является адресом источника, второй адрес является адресом приемника, т.е. адресом, по которому выбирается второй операнд, и в который записывается результат операции.

Для задания полного адреса в команде предусмотрены два смежных трехбитных поля. Первое поле – это поле режима адресации, второе поле – поле РОНа, используемого для задания компоненты адреса.

Для обозначения содержимого полей в архитектуре PDP-11 используется восьмеричная система счисления.

Адресные поля команд всех структур могут быть расширены одним или двумя дополнительными словами в зависимости от используемых режимов адресации.

Команды структуры "a" и "b" – это тоже двухадресные команды, но в качестве одного из операндов используется содержимое РОНа. В команде структуры «b» второй адрес задается смещением относительно счетчика команд. Это структура команды выхода из цикла. Содержимое указанного в команде РОНа автоматически уменьшается на размер выполненной команды. Пока содержимое РОНа не равно нулю, происходит передача управления на команду по адресу, равному содержимому счетчика команд плюс удвоенное смещение (в словах), которое рассматривается как число со знаком.

Команды со структурой "с" – это одноадресные команды, операнд адресуется и в памяти и в РОНах.

Команды со структурой "d" – это одноадресные команды. Адрес задается РОНом. Это могут быть команды обработки данных из стека, в этих случаях указанный в команде РОН является указателем стека.

Команды структуры "е" – это безадресные операции.

Команды структуры "f" – это команды условной передачи управления, условие передачи управления задается кодом операции, а адрес перехода задается удвоенным смещением относительно счетчика команд. Смещение рассматривается как число со знаком.

Набор команд

Все возможные коды операций двухадресной команды представлены в табл. 4 (команды с суффиксом В – байтовые)

|

№ |

Код |

№ |

Код |

Описание |

|

0000 |

– |

1000 |

|

В двухместных полноадресных командах не используется |

|

0001 |

MOV |

1001 |

MOVB* |

Пересылка содержимого источника в приемник |

|

0010 |

CMP |

1010 |

CMPB |

Сравнение источника с приемником, установка кода условий |

|

0011 |

BIT |

1011 |

BITB* |

Тестирование битов (по маске**), установка кода условий |

|

0100 |

BIC |

1100 |

BICB* |

Сброс битов (по маске**). |

|

0101 |

BIS |

1101 |

BISB* |

Установка битов (по маске**) |

|

0110 |

ADD |

1110 |

SUB |

Сложение – 0110 или вычитание 1110 с записью результата |

|

0111 |

– |

1111 |

|

В двухместных полноадресных командах не используется |

|

Примечания: *– команды с суффиксом В – байтовые **маска задается вторым адресом | ||||

Кроме команд сложения и вычитания, все коды в этом формате по отношению к размерам операндов симметричны. На каждую операцию предусмотрено два кода операции: один для обработки полных операндов (слов), другой – для обработки байт. На языке ассемблера коды обработки байт содержат суффикс B. Пример:

MOV А1 А2 ;переслать слово,

MOVВ А1 А2 ;переслать байт,

где: А1 и А2 – адреса памяти или РОН, заданные в команде.

Режимы адресации

Режимы адресации задаются трехразрядным полем режима адресации. Если команда содержит два адреса, то режимы адресации для каждого операнда задаются независимо друг от друга, каждый своим полем режима.

Трехразрядное поле режима адресации позволяет задать 8 основных режимов адресации. Режим адресации – это правило вычисления адреса операнда по заданному РОНу и, возможно, одному из дополнительных слов команды. Использование дополнительных слов команды также определяется режимом адресации. Но не все РОНы в МП ЭВМ PDP-11 равнозначны. Регистр R7– это счетчик команд. Использование этого регистра для задания режима адресации или бессмысленно или, для четырех режимов, дает эффекты новых режимов.

Таким образом, программист, меняя режимы и используя как обычные РОНы, так и счетчик команд, может задавать операнды в командах двенадцатью режимами адресации. Основные режимы адресаций представлены в табл.5.

Таблица 5 Основные режимы адресаций

|

| |||

|

№ |

Мнем. |

Название |

Описание |

|

0 |

R |

Регистровая |

В регистре–операнд |

|

1 |

(R) |

Регистровая косвенная |

В регистре – адрес операнда |

|

2 |

(R)+ |

Автоувеличение |

В регистре – адрес операнда. После использования, адрес увеличивается на длину операнда |

|

3 |

@(R)+ |

Автоувеличение косвенная |

В регистре – адрес адреса операнда. После использования, адрес увеличивается на 2. |

|

4 |

– (R) |

Автоуменьшение |

Содержимое регистра уменьшается на длину операнда, результат используется как адрес операнда |

|

5 |

@ – (R) |

Автоуменьшение косвенная |

Содержимое регистра уменьшается на 2, результат используется как адрес адреса операнда |

|

6 |

X(R) |

Индексная |

Сумма содержимого регистра и индекса используется как адрес операнда, в качестве индекса используется второе или третье слово команды |

|

7 |

@X(R) |

Индексная косвенная |

Сумма содержимого регистра и индекса используется как адрес адреса операнда, в качестве индекса используется второе или третье слово команды |

Вопросы и/или темы для самопроверки:

Максимальный размер математической памяти в PDP-11.

Максимальный размер физической памяти в PDP-11.

Особенности использования РОН.

Биты кодов условия регистра состояния процессора.

Количество разрядов кодирования полного адреса данных в команде PDP-11.

Основные поля в команде PDP-11, задающие адреса операндов.

Основные режимы адресации в PDP-11.

Режимы адресации с использованием счетчика команд в PDP-11

5 неделя. Лекция 5.

Программная модель МП Intel

Режимы работы

Корпорация Intel для использования в РС выпускала микропроцессоры различной разрядности. Наиболее известные из них:

шестнадцатиразрядные микропроцессоры (МП i8086),

двадцатичетырехразрядные микропроцессоры (МП i8286),

тридцатидвухразрядные микропроцессоры (от МП i8386 – до Pentium IV),

шестидесятичетырехразрядные микропроцессоры (Itanium.). Но это уже принципиально новая модель архитектуры EPIC (Explicitly Parallel Instruction Computing – вычисления с явным параллелизмом команд).

Имеется еще расширение архитектуры МП до 64 бит, совместимых c IBM PC, (модели МП Hammer (К-8) корпорации АМD), но это расширение коснулось только формата данных и РОН.

Программная модель 16-ти битового микропроцессора МП IA-16

Модель памяти

Одна из особенностей МП Intel – это использование сегментированной памяти. 16-разрядная адресация позволяла адресовать только 216 = 65 536 байт (64 Кбайт). Вероятно, по этой причине была выбрана модель структурированной математической памяти, состоящая из 16 сегментов по 65 536 байт (64 Кбайт). Этот прием позволил увеличить адресное пространство математической памяти в реальном режиме до 220 = 1 048 576 (1 Мбайт).

При каждом обращении к физической памяти необходима процедура преобразования адреса обращения из адреса сегментированной математической памяти в адрес линейной физической памяти. Это процедура трансляции сегмента – вычисление адреса линейной, плоской физической оперативной памяти по адресу сегмента и смещению в сегменте.

При каждом обращении к физической памяти необходима процедура преобразования адреса обращения из адреса сегментированной математической памяти в адрес линейной физической памяти. Это процедура трансляции сегмента – вычисление адреса линейной, плоской физической оперативной памяти по адресу сегмента и смещению в сегменте.

Регистровый файл

Регистровый файл МП IA-16 содержит 14 пользовательских регистров:

регистры общего назначения (РОНы) – 8 регистров,

сегментные регистры – 4 регистра,

указатель команд – 1 регистр,

регистр состояния (флагов) – 1 регистр.

Все эти регистры в той или иной степени доступны программам пользователей.

Регистры общего назначения

регистры данных – ax, cx, dx и bx (по возрастанию адресов),

регистры адресов – sp, bp, si и di (по возрастанию адресов).

Регистр bx, хоть его и относят к группе регистров данных, является и одним из регистров адреса базы данных (для сегмента DS).

Регистр dx может использоваться в качестве адресного регистра портов в командах ввода/вывода.

Регистры cx, si и di по умолчанию используются при обработке строк.

|

|

15 |

8 |

7 |

0 |

|

|

ax |

ah |

al |

Аккумулятор | ||

|

cx |

ch |

cl |

Счетчик | ||

|

dx |

dh |

dl |

Данные | ||

|

bx |

bh |

bl |

База (для DS) | ||

|

|

sp |

Указатель стека | |||

|

|

bp |

База кадра стека SS) | |||

|

|

si |

Индекс источника | |||

|

|

di |

Индекс приемника | |||

|

|

Рис. 3.2 РОНы | ||||

Сегментные регистры и трансляция сегментов

Адрес объекта в сегментированной памяти задается двумя компонентами: базовым адресом сегмента и смещением в сегменте. В команде задается только смещение в сегменте. Базовый адрес сегмента задается содержимым одного из четырех сегментных регистров

МП IA-16 содержали четыре 16-разрядных сегментных регистра:

ES – регистр дополнительного сегмента данных,

CS – регистр сегмента кода,

SS – регистр сегмента стека,

DS – регистр сегмента данных,

Преобразование адреса сегментированной памяти в адрес линейной (плоской) памяти производится процедурой трансляции сегмента: сложением базового адреса сегмента с адресом операнда в сегменте.

Но сегментные регистры 16-битные, а базовые адреса должны быть 20- битными. Поэтому при использовании сегментных регистров их содержимое умножается на 16 добавлением четырех нулей после младшего разряда.

Таким образом, адрес в сегменте математической памяти МП IA-16 задается тремя компонентами: B (база), X (индекс) и disp (смещение).

Для вычисления адреса обращения к физической памяти (при сегментированной структуре математической памяти) требуются, по крайней мере, две процедуры:

вычисление прямого адреса в сегменте по компонентам (В), (Х) и disp,

преобразование адреса в сегменте сегментированной памяти в адрес линейной физической памяти.

Результатом первого преобразования адреса является получение одного компонента логического адреса – смещения в сегменте, результатом второго преобразования – получение смещения в линейной памяти.

Для уменьшения неопределенности при использовании вышеописанных смещений используют термины:

disp – для обозначения смещения в кадре сегмента,

offset – для обозначения смещения в сегменте,

линейный адрес – для обозначения адреса (смещения) в линейной (не сегментированной) памяти.

Указатель команд IP

Это 16-битный регистр -счетчик, вычисляющий адрес следующей команды (в кодовом сегменте) по числу байт в текущей команде.

Регистр состояния (флагов) FLAGS

Это 16-разрядный регистр, в котором сгруппированы управляющие сигналы режимов работы основных систем процессора и флаги кодов условий для условных команд передач управления.

Структура команд

На языке ассемблера команды содержат символьный код операции и один или два адреса. Команды могут быть одноадресными или двухадресными. Первый адрес в команде – адрес приемника, второй – источника. Оба адреса могут быть адресами РОНов, адресом оперативной памяти может быть только один.

Исключением являются:

команды обработки строк (адреса приемника и источника задаются парами регистров – сегментный регистр:индексный регистр)

команды работы со стеком, которые перемещают данные из памяти в стек, который также находится в памяти.

Адрес оперативной памяти может задаваться прямым адресом (offset) или компонентами (D, X, disp).

Машинная кодировка команд IA – 16

МП IA-16 используют команды переменного формата от 1 до 7 байт. Кодировка команд производилась с учетом частоты использования команды в типовых программах.

Команда может иметь :

возможно, префикс (1 или 2 однобайтных префикса),

код операции (1 байт),

возможно, постбайт (1байт),

возможно, байты смещения – disp (1 или 2 байта),

возможно, байты непосредственного операнда (1 или 2 байта).

|

0, 1 или 2 байта |

1 байт |

0 или 1 байт |

0,1 или 2 байта |

0,1 или 2 байта |

|

префикс |

код операции |

постбайт |

байты смещения |

непосредственный операнд |

|

| ||||

Элементы команды:

Префикс

Это необязательный байт, модифицирующий процедуру выполнения команды.

МП IA -16 предусматривает использование двух префиксов:

повторения,

замены сегмента памяти, используемого по умолчанию (только для данной команды).

Код операции

Это единственный из обязательных элементов команды (1 байт), задающий операцию. Возможны операции, заданные одним кодом операции. Это одноадресные команды, операнд для которых задается по умолчанию. Поле кода операции может содержать собственно код операции и от одного до 3 специальных битов:

w– размер операнда (7-й бит), приw= 0 размер операнда – байт, приw= 1 размер операнда – слово.

d– направление передачи результата для двухместной команды (6-й бит).

при d = 1 – адресом приемника является РОН, заданный полемregпостбайта,

при d= 0 – адресом приемника является адрес памяти;

В одноместной команде используется только источник и 6-й бит байта кода операции (s=1)определяет автоматическое расширение байта данных до размера слова.

Постбайт

Это необязательный элемент команды. Задает один (для одноадресной команды) или два адреса операндов, один из которых используется и как адрес результата.

-

7

6

5

3

2

0

md

reg

r/m

Рис. 3.6. Структура постбайта

Постбайт (рис. 3.6) содержит 3 поля:

md– поле режима адресации,

reg– поле адреса регистра,

r/m– поле адреса второго регистра или кода, определяющего способ вычисления адреса ячейки памяти.

Программная модель 32-битового микропроцессора

В программной модели МП IA-32 от МП IA-16 с поправками на разрядность ширины обработки данных сохранились следующие решения:

модель сегментированной математической памяти,

задание адресов в сегменте компонентами, но с расширением возможностей по заданию адреса в массиве (использование возможности индексирования элементов массива в произвольном порядке),

выделение адресного пространства для портов (программно-доступных регистров контроллеров устройств ввода-вывода).

Основной особенностью программной модели МП IA-32, кроме расширения разрядности адресов данных и команд, индексирования элементов массива в произвольном порядке и многократного расширения адресного пространства математической памяти, является встроенная аппаратная система защиты программ от взаимных помех.

Эта система предусматривает:

использование специальных программных структур:

дескрипторов сегментов, определяющих сегменты (данных, программ),

дескрипторов шлюзов (точек входов в программные сегменты).

введение :

1.системных и пользовательских таблиц дескрипторов,

2.новой процедуры программных переходов "переключение задач".

3.набора системных регистров дескрипторов.

Структура команд и режимы адресации

Команда в защищенном режиме (рис. 3.17) может содержать от 1 до 17 байт:

|

0, 1,2,3,4 или 5 байта |

1 байт |

0 или1 байт |

0 или1 байт |

0,1,2 или 4 байта |

0,1,2 или 4 байта |

|

префикс |

код операции |

постбайт |

SIB - байт |

байты смещения |

байты операнда |

1. Префиксы (0,1,2,3 или 4 байт):

префикс блокировки шины реализует блокировку шин к общим ресурсам.

префикс замены сегмента в явной форме указывает сегментный регистр, используемый программой,

префикс переключения разрядности адреса изменяет принятую по умолчанию разрядность адреса на альтернативную (с 2-х байт на 4 или наоборот),

префикс размера операнда изменяет разрядность операнда, принятую по умолчанию.

префикс повторения используется с командами обработки строк, задает условие окончания операции.

Байт SIB (scale-index-base – масштаб-индекс-база) – может отсутствовать; если присутствует – является дополнением к постбайту, модифицирующим процедуру базово-индексной адресации; присутствие байта SIB определяется полем постбайта r/m =100.

Режимы адресации МП IA-32 с использованиемSIB-байта (r/m= 100) означают, что следующий байт команды являетсяSIB-байтом, а адрес операнда в упорядоченных массивах данных памяти (таблицах) вычисляется по формуле:

(B) + 2S (I) + Disp,

где: B, I и S – поля байта SIB.

постбайта в МП IA-32.

Структура данных

Архитектура IA-32 предполагает наличие не менее двух процессоров, даже если они интегрированы в одном блоке. В поздних моделях МП их называют не процессорами, а модулями обработки данных. Здесь речь идет, скорее, о множестве структур данных в зависимости от реализованных в процессоре "арифметик".

Основным модулем обработки данных является модуль обработки чисел с фиксированной запятой (точкой). В настоящее время – это целочисленная арифметика, обработка двоично-десятичных чисел и строк символов.

Дополнительным модулем является модуль обработки чисел с плавающей запятой (модуль обработки вещественных чисел).

В МП, начиная с Pentium MMX, используется дополнительный мультимедийный модуль обработки векторных данных.

Мультимедийный модуль обработки векторных данных. Этот модуль, появившись в МП Pentium Pro в варианте 57 команд обработки векторных 64-битных данных с фиксированной запятой, в последующих моделях непрерывно совершенствовался.

В моделях МП Pentium 4 стало использоваться второе поколение потоковых команд расширения SSE2 (Streaming SIMD Extensions 2). Набор из 144 команд SSE2 поддерживает новые форматы упакованных данных с использованием 128-разрядных регистров (XMM-регистров) как при операциях с плавающей запятой, так и при операциях с фиксированной запятой.

Вопросы и/или темы для самопроверки:

Понятие сегментированной памяти.

Место хранения базовых адресов сегментов.

Термин "линейный адрес" при задании адреса в МП IA.

Процедура трансляции сегмента при обращении к памяти в МП IA-16.

Структура команд в МП IA-16.

Назначение префикса в командах МП IA-16.

Назначение постбайта в командах МП IA-16.

Поля и назначение SIB-байта в МП IA-32.

6 лекция. 6 неделя (1 тестирование перед началом лекции – 10 мин.)

Система прерывания

5.1.Функции системы прерывания и общие решения по реализации

Система прерывания появилась в процессорах ЭВМ второго поколения, которые использовались, в основном, в качестве программных устройств управления различными объектами.

Основными причинами появления системы прерывания являются:

желание разработчиков уменьшить простои ЭВМ при возникновении внештатных ситуаций в процессоре (попытки деления на ноль, использование несуществующей команды, сбой в устройстве и т.д.),

желание разработчиков загрузить полезной работой процессор во время, когда он ожидает сигнал от управляемого объекта, т.е. желание реализовать фоновую работу ЭВМ.

Несмотря на то, что система прерывания появилась для разрешения двух разных по сути проблем, в современных ЭВМ используется единый механизм прерывания. Но, несмотря на единый механизм прерывания, различают особенности процедуры обработки прерываний при внештатных ситуациях в процессоре и при приходе сигналов прерывания от внешних устройств.

С переходом на многопрограммные режимы работы система прерывания стала обязательным компонентом всех ЭВМ. Система прерывания – это эффективный способ реализации контрольных и управляющих функций операционной системы для поддержки заданных режимов работы ЭВМ как аппаратно-программного комплекса.

С этой точки зрения система прерывания является интерфейсным слоем между аппаратными и программными средствами ЭВМ.

Процедура прерывания заключается в переходе на подпрограмму обработки прерывания с возможностью возврата в основную программу.

В этом изложении процедура прерывания совпадает с процедурой вызова подпрограммы с возвратом, например при выполнении команды Call. Но эти процедуры имеют существенные различия в реализации возможности возврата в основную программу.

Проблема заключается в том, что команды имеют определенное последействие, которое влияет на выполнение последующих команд. Например, выполнение команды условного перехода может зависеть от результата выполнения предыдущей команды.

Каждая команда (кроме NOP) меняет контекст программы (имеет последействие), записывая результат выполнения в память, РОН или в регистр состояния.

Команды вызова процедуры с возвратом расставляются программистом с учетом такого последействия. Но прерывание – событие, в общем случае, случайное по отношению к программе. Программа обработки прерывания может изменить контекст программы, что может привести к нарушению корректности выполнения последующих команд основной программы.

По этой причине в процедуру прерывания включают этап сохранения контекста программы, а при возращении из процедуры – этап его восстановления.

Сохранение контекста может быть реализовано схемными, программными или схемно-программными способами. Наиболее часто используют схемно-программное сохранение контекста. При этом контекст делится на основную часть и дополнительную.

В основную часть входят коды условий и биты управления, собранные в регистр состояния программы (PSW – Program Status Word или PS). Для МП Intel – это регистр флагов (EFLAGS).

В дополнительную часть входит содержимое РОН и ячеек памяти.

Основная часть контекста сохраняется аппаратно, обычно в стек. Содержимое РОНов сохраняется и восстанавливается программой обработки прерывания, причем сохраняются и восстанавливаются только РОНы, используемые программой обработки прерывания.

Так как адресные пространства программ обработки прерывания и основной программы всегда разделяются, сохранение ячеек памяти в процедуре прерывания не предусмотрено.

В зависимости от причин, прерывания делятся на исключения (ловушки) и собственно прерывания.

Ловушка (Trap)– это реакция системы на появление в работе процессора нештатных ситуаций: попытка деления на ноль, выявление несуществующего адреса и т. д. К ловушкам относятся также специальные команды программируемого прерывания.

Прерывание (Interrupt)– это реакция системы на запрос внешнего устройства (сигнал прерывания) по выполнению процессором определенной процедуры управления.

Таким образом, ловушки выявляются схемами фиксации особых ситуаций в процессоре (штатных или нештатных), требующих контроля со стороны операционной системы. При этом с каждой схемой фиксации особых ситуаций связаны определенные программы обработки прерывания.

Сигналы прерывания – это сигналы от внешних по отношению к процессору устройств в моменты, требующие управляющих действий со стороны операционной системы.

Основными вопросами реализации системы прерывания являются:

прием сигналов прерывания и ловушек и выделение приоритетного сигнала,

определение момента выполнения процедуры прерывания,

выбор процедуры прерывания (модели сохранения контекста и перехода на программу обработки прерывания),

выбор процедуры возврата из процедуры прерывания (модели восстановления контекста и перехода на основную программу).

Прием сигналов прерывания и ловушек и выделение приоритетного сигнала

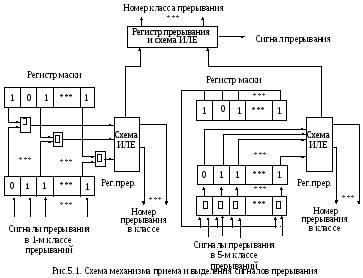

Прием сигналов (запросов) прерывания производится для определения конкретной программы обработки прерывания. В большинстве ЭВМ система прерывания предусматривает 256 программ обработки ситуаций, вызвавших запрос на прерывание. Каждая программа обработки прерывания связана с определенным источником прерывания и определяется номером прерывания. На рис.5.1. представлена обобщенная схема приема и приоритетного выделения сигналов прерывания. Выбор сигнала прерывания определяет номер источника прерывания и программу обработки этого прерывания.

Однопроцессорная система не может выполнять программы обработки прерывания одновременно по нескольким запросам. Поэтому используется приоритетное выделение принимаемых сигналов прерывания. Здесь возможны варианты.

Прием сигналов может производиться по общему проводу. В этом варианте, для выявления источников сигналов прерывания производится последовательный опрос процессором всех возможных источников сигнала прерывания.

Последовательность опроса определяет приоритет сигнала прерывания устройства.

При опросе все устройства, пославшие сигналы прерывания, в своих ответах определяют программы обработки прерывания.

Альтернативным способом приоритетного определения источника сигнала прерывания является прием сигналов прерываний от внешних устройств по индивидуальным проводам и фиксация их на отдельном регистре прерывания.

В этом случае в систему прерывания вводится схема приоритетного анализа поступивших сигналов. Для этого используется комбинационная схема, так называемый искатель левой единицы (ИЛЕ).

Эта схема задает жесткий приоритет сигналов прерывания. Но важность первоочередной обработки причин прерываний может меняться. Для этого в систему прерывания вводят регистр маски на те прерывания, приоритеты которых желательно менять. В том случае, изменяя значения бит регистра маски, отмечают сигналы прерываний, видимых искателю левой единицы. Примером может служить система прерывания семейства IBM 360.

В моделях этого семейства сигналы прерываний разделены на 5 классов. В каждом классе имеется своя схема приема и выделения сигналов прерывания, учитывающая специфику причин сигналов прерываний.

На рис 5.1 представлена упрощенная схема механизма системы прерывания. В этой схеме рассматривают только два крайних (по реализации выделения сигналов) класса системы прерывания.

В этой схеме производится параллельное определение самого приоритетного источника сигнала прерывания в схемах приема и выделения сигналов прерывания по отдельным классам и между классами. Источник прерывания (номер программы) определяется конкатенацией (сцепление литерных или битовых строк) номера класса прерывания с номером прерывания в выбранном классе прерываний.

Определение момента выполнения процедуры прерывания

Сигнал прерывания, в общем случае, не является сигналом немедленного действия. Обычно сигнал прерывания (от внешних устройств) или ловушки (от схем контроля выполнения операций) просто фиксируется в соответствующем разряде регистра прерывания.

Выполнение перехода на программу обработки ситуации всегда происходит с определенной задержкой (время реакции системы прерывания).

Здесь возможны несколько вариантов в выборе момента начала процедуры прерывания:

Программы состоят из последовательностей автономных участков (процедур) с минимальным набором передаваемой информации. Обычно это содержимое памяти или РОН. Это точки с минимумом контекста. Программист может отмечать эти точки особыми командами для использования их в качестве команд прерывания. Но это решение значительно увеличивает среднее время реакции системы прерывания.

Среднее время реакции системы прерывания значительно (в разы) сокращается, если процедуру прерывания производить сразу после окончания текущей команды.

Имеется еще возможность уменьшения времени реакции системы прерывания, если процедуру прерывания начинать сразу после окончания не команды, а текущей части команды (микрооперации), во время которой появился запрос прерывания. Но при этом приходится дополнительно сохранять результат текущей микрооперации.

В подавляющем большинстве архитектур ЭВМ процедура прерывания производится по окончании текущей команды.

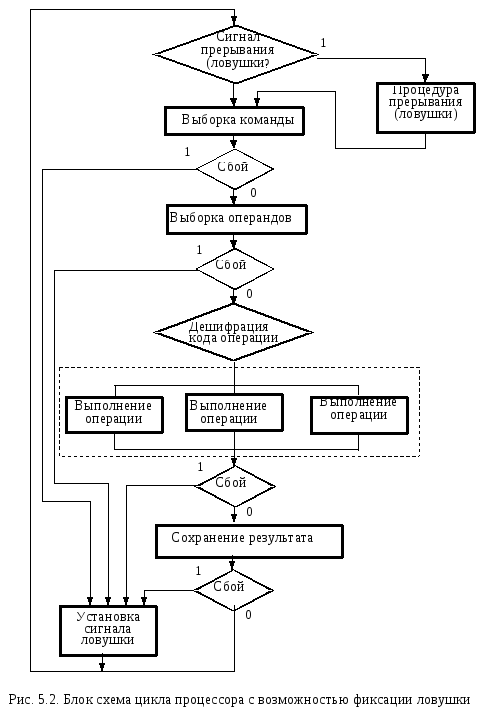

На рис. 5.2 представлена упрощенная схема цикла выполнения команды с фиксацией ловушки (внештатной ситуации) и проверкой сигнала прерывания.

Выполнение команд в процессоре является циклическим. Начинаем рассмотрение с процедуры выборки команды. Это начало цикла. Результатом этого этапа является выборка и анализ полей команды, адресов операндов и результата. Следующим этапом является этап выборки операндов. Последующие этапы производят дешифрацию кода операции и передачу команды в блоки выполнения. Последним этапом является этап сохранения результата и записи признака результата в регистр состояния.

На всех этапах этой микропрограммы работает встроенная аппаратная система непрерывного контроля безошибочности работы аппаратуры. При обнаружении ошибок (сбоев) на любом этапе выполнения команды система производит фиксацию ошибки. Перед началом каждого следующего этапа производится проверка корректности выполнения предыдущего этапа. В случае обнаружения ошибки, она фиксируется в специальном регистре как исключительная ситуация (ловушка), и управление передается (в обход всех последующих этапов) на блок проверки наличия сигналов прерывания или ловушки (см. рис 4.1).

В случае обнаружения прерывания или ловушки производится соответствующая процедура прерывания или ловушки.

Процедура прерывания или ловушки

Процедура прерывания или ловушки заключается в сохранении контекста программы и передаче управления на программу обработки прерывания.

Процедура возврата из прерывания или ловушки

Процедура возврата из прерывания заключается в восстановлении контекста прерванной программы и передаче управления на эту программу.

Вопросы и/или темы для самопроверки:

Две причины появления в ЭВМ системы прерывания.

Определение процедуры прерывания.

Основная часть контекста программы и дополнительная часть контекста программы.

Механизм сохранения основной части контекста.и механизм сохранения дополнительной части контекста

Основные вопросы реализации системы прерывания.

Основные этапы приема и выделения сигналов прерывания.

Момент реализации процедуры прерывания.

Процедура возврата из прерывания.

7 неделя 7 лекция