- •Оглавление.

- •§1.2. Режим реального времени

- •Глава 2. Вычислительные системы §2.1. Классификация вс.

- •§2.2. Показатели качества вс.

- •§2.3. Классификация вс по организации структуры.

- •Глава 3. Распределение ресурсов процессора. §3.1. Принципы упорядочивания ресурсов вс методами теории расписаний.

- •§3.2. Общая постановка задачи упорядочивания.

- •§3.3. Задачи и критерии детерминированного распределения производительности вычислительных систем.

- •Глава 4. Распределение памяти в вс. §4.1. Оптимизация распределения памяти по иерархическим уровням.

- •§4.2. Управление замещением страниц в двухуровневой памяти.

- •§4.3. Класс многоуровневых алгоритмов замещения.

- •§4.4. Модели поведения программ и критерии качества.

- •Глава 5. Классические архитектуры многомашинных и многопроцессорных комплексов. §5.1. Многомашинные комплексы.

- •§5.2. Многопроцессорные комплексы.

- •§5.3. Типы структур мпвк.

- •Глава 6. Примеры многомашинных и многопроцессорных систем. §6.1. Вк на базе ес эвм (ibm).

- •§6.2. Вк на базе см эвм (dec).

- •§6.3. Комплексы на основе микро-эвм и микропроцессоров.

- •Глава 7. Особенности организации вычислительных процессов.

- •Глава 8. Системы параллельной обработки данных. §8.1. Классификация систем параллельной обработки данных.

- •Глава 9. Кластерные системы. §9.1. Кластерная архитектура.

- •§9.2. Проблемы выполнения сети связи процессоров в кластерной системе.

- •Глава 10. Принципы построения коммуникационных сред. §10.1. Коммутаторы для многопроцессорных вычислительных систем.

- •§10.2. Простые коммутаторы.

- •Алгоритмы арбитража. Статические приоритеты.

- •Динамические приоритеты.

- •Фиксированные временные интервалы.

- •Очередь fifo.

- •Особенности реализации шин.

- •Простые коммутаторы с пространственным разделением.

- •§10.3. Составные коммутаторы.

- •Коммутатор Клоза.

- •Распределенные составные коммутаторы.

- •Глава 11. Примеры построения коммуникационных сред. §11.1. Когерентный интерфейс sci.

- •§11.2.Коммуникационная среда myrinet.

- •Глава 12. Сосредоточенные вычислительные системы высокой производительности. §12.1. Конвейерные системы.

- •§12.2. Иерархия памяти.

- •§12.3. Управление и организация конвейеров.

- •§12.4. Статические конвейеры.

- •§12.5. Диаграмма состояний.

- •§12.6. Генерирование таблиц занятости на основе циклов.

- •§12.7. Конвейеры с динамической конфигурацией.

- •§12.8. Функции управления в конвейерных системах.

- •§12.9. Архитектура конвейерных систем.

- •§12.10. Примеры конвейерных систем.

- •§12.11. Матричные вычислительные системы.

- •Резюме.

- •Список литературы.

Глава 6. Примеры многомашинных и многопроцессорных систем. §6.1. Вк на базе ес эвм (ibm).

На базе Единой Системы ЭВМ (ЕСЭВМ) в СССР были построены

различные многомашинные комплексы.

Первым двухмашинным комплексом был ВК-1010, построенный на базе ЕС-1030. В этом комплексе были использованы почти все существующие способы организации связи между ЭВМ: прямое управление , адаптер канал- канал, связь на уровне общих ВЗУ.

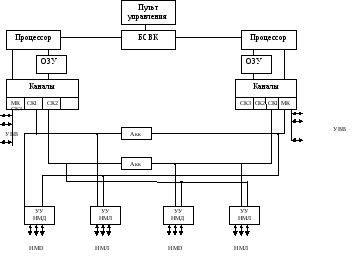

В ВК-1010 нет лишь связи между ЭВМ через общую ОП. Структурная схема ВК-1010 осталась практически без изменения и для последующих двух машинных ВК: ВК-1033, ВК-2Р-35(ЕС-1035),ВК-2Р-45(1045), ВК-2Р-60(ЕС-1060). Эта схема (рисунок 6.1) является типовой для ЕС.

Рисунок 6.1.

Обмен управляющей информацией между ЭВМ осуществлялся с помощью средств прямого управления, к которым относятся стандартный интерфейс прямого управления, специальный механизм ПРЯМАЯ ЗАПИСЬ и ПРЯМОЕ ЧТЕНИЕ, и механизм внешних прерываний. Эти средства позволяют осуществлять быструю связь между процессором и обычно используют для передачи небольших объемов информации.

Через канал прямого управления к ВК подключается блок состояния вычислительного комплекса (БСВК) и пульт управления, которые вместе образуют устройство управления вычислительным комплексом. Блок состояния включает в себя блок управления и регистры состояния, которые определяют режим работы ВК. Запись в эти регистры осуществляется либо оператором с пульта, либо по команде ПРЯМАЯ ЗАПИСЬ. С помощью команды ПРЯМОЕ ЧТЕНИЕ содержание этих регистров может быть переписано в ОП.

Интерфейс прямого управления включает в себя : входные и выходные линии информации, линии синхронизации, линии внешних сигналов, линии записи и чтения.

Блок состояния совместно с пультом управления ВК позволяет осуществить ручное переключение ВК и ЭВМ в требуемый режим работы: начальную загрузку программ, внешнее прерывание, включение и выключение питания. Кроме того, на пульте управления осуществляется индикация состояний ЭВМ, а также необходимая сигнализация об аварийных ситуациях.

АКК работает в монопольном режиме с высокой пропускной способностью. Для каждой ЭВМ АКК является внешним устройством, который реагирует на все запросы каналы, только команды и сигналы используются не для управления ПУ, а для передачи информации между каналами и синхронной их работы. В структуру АКК входят 2 блока управления обменом, связанных непосредственно с помощью нескольких сигнальных линий, а также через общий буферный регистр.

Третье средство комплексирования – связь ЭВМ через ВЗУ. Все УУ НМЛ и НМД имеют двухканальные переключатели, которые позволяют подключение УУ либо к двум каналам, либо к каналам двух ЭВМ. В первом случае это приводит к повышение надежности, во втором – к организация общего поля внешней памяти. Аппаратные средства дополняются соответствующими программными средствами. Для обращения одного процессора к другому по интерфейсу прямого управления служит команда ПРЯМАЯ ЗАПИСЬ. Предусмотрена также программная проверка правильности информации, передаваемой через АКК, с помощью контрольной суммы.

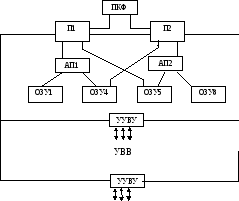

Первым двухпроцессорным комплексом в ЕС ЭВМ был комплекс ВК 2П45, структура которого является типовой для двухпроцессорного комплекса в ЕС (рисунок 6.2). Тип структурной организации – это МПВК с многовходовой памятью. Процессоры имеют доступ к модулям ОП через адаптеры памяти (АП), которые осуществляют необходимую коммутацию.

Рисунок 6.2.

Оба процессора могут обращаться в ОЗУ одновременно, конфликты возникают при обращении двух процессоров к одному АП. Для их разрешения предусмотрена схема, организующая очередь запросов. Схема работает таким образом, что при наличии запросов от двух процессоров обращение их к ОЗУ производится попеременно, обращение дважды подряд одного процессора запрещено.

Реконфигурация комплекса осуществляется со специального пульта реконфигурации, который имеет соответствующие органы. С их помощью любой модуль ОЗУ может подключить к любому процессору или к обоим процессорам, а также задать любой диапазон адресов в пределах установленной емкости ЗУ, соблюдая непрерывность адреса. Кроме того, с пульта осуществляется подключение и реконфигурация УВВ и устанавливается один из трех режимов работы ВК:

1) однопроцессорный, когда комплекс работает как вторая самостоятельная ЭВМ;

2) двухпроцессорный;

3) полудуплексный, когда работает один процессор, использующий всю оперативную память, а второй может быть отключен.

В двух процессорном, как и в двухмашинном комплексе существует непосредственная связь может процессорами для обмена управляющей информацией, потребности в этом обмене может возникнуть при необходимости запуска или остановки одного процессора другим, при взаимном контроле состояния.

Кроме команд ПРЯМАЯ ЗАПИСЬ и ПРЯМОЕ ЧТЕНИЕ в двухпроцессорном режиме для прямого управления используется также специальная команда СИГНАЛ ПРОЦЕССОРУ. Эта команда определяет адрес процессора, с которого осуществляется связь и код приказа. В адресуемом процессоре могут возникнуть условия, препятствующего выполнению того или иного приказа. Эти условия формируют соответствующие биты байта состояния. Байт состояния передается в выдающий приказ процессор в качестве ответа на приказ. В двухпроцессорном ВК ЕС предусмотрено 12 таких приказов.

Все указанные аппаратные средства, поддерживаются специальным вариантом ОС ЕС.

МПВК «Эльбрус».

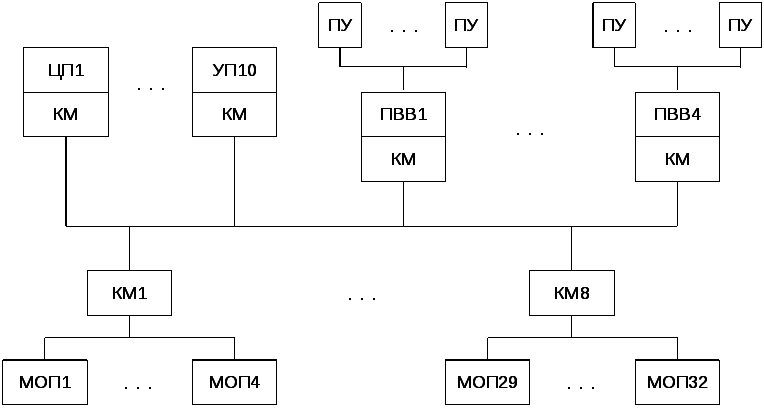

При создании МПВК «Эльбрус» ставилась задача обеспечения высокой производительности и надежности при решении задач, требующих большого объема вычислении. Наилучшим образом такая комплексная цель может быть достигнута путем создания МПВК с однородной организацией во всех процессорах. Комплекс содержит до 10 процессоров. При увеличении числа процессоров резко возрастает число конфликтов из-за ресурсов и увеличиваются затраты ресурсов используемых ОС, в результате чего производительность растет медленно (рисунок 6.3).

Рисунок 6.3.

Для уменьшения этого эффекта увеличивается число модулей ОП, ВЗУ и УВВ, процессоры снабжается быстрым буфером ЗУ, отдельные модули ОС реализуется техническими средствами. Включение в состав комплекса большого числа модулей с независимым управлением и ПУ позволяют свести к минимуму конфликты из-за ресурсов.

Многовходовая память построена следующим образом. Четыре модуля памяти (МОП) объединяются одним общим коммутационным модулем (КМ), который подключает любой МОП к 10 центральным процессорам (ЦП) и четырем процессорам ввода/вывода (ПВВ). Число КМ – до 8, а МОП – до 32. Центральные процессоры (ЦП) взаимодействуют с ОП и ПВВ через КМ. Все ПУ (ленты, диски, барабаны, УВВ и передачи данных) подключены к центральной части через ПВВ, которые являются специализированными, имеют буферное ЗУ, АЛУ и работает по заявкам ЦП. ПВВ реализует аппаратно функции ОС по управлению УВВ. При этом ПВВ определяет пути обмена информацией (каждое ПУ имеет несколько путей доступа к ПВВ), осуществляет подключение и резервирование устройств.

В качестве УВВ используется весь комплекс устройств ЕС ЭВМ. Все устройства комплекса работают параллельно и независимо и охвачены аппаратным контролем. Все задания и процессы находятся в одной общей очереди, ожидая освобождения процессоров. Как только процессор освободится, то обращается к этой очереди и берет первый в очереди процесс. Производительность в максимальной комплектации достигала 12 млн. оп/с.

Комплекс Эльбрус-2 в максимальной конфигурации обеспечивал производительность свыше 100 млн. оп/с. Архитектура его такая же, как и у комплекса Эльбрус-1, но на более совершенной элементной базе.