- •Цель работы

- •Постановка задачи

- •1 Мультиплексор 4-1

- •1.1 Таблица истинности

- •1.2 Формула

- •1.3 Функциональная схема

- •1.4 Моделирование функциональной схемы

- •1.6 Схема из rtl viewer для кода hdl

- •1.7 Моделирование устройства, описанного кодом hdl.

- •1.8 Таблица истинности масштабируемого устройства

- •1.9 Функциональная схема масштабируемого устройства

- •1.10 Моделирование масштабируемого устройства

- •1.11 Код на hdl масштабируемого устройства

- •1.12 Схема из rtl viewer для кода hdl масштабируемого устройства

- •1.13 Моделирование масштабируемого устройства, описанного кодом hdl

- •2 Демультиплексор 1-8

- •2.1 Таблица истинности

- •2.2 Формула

- •2.3 Функциональная схема

- •2.4 Моделирование функциональной схемы

- •2.6 Схема из rtl viewer для кода hdl

- •2.7 Моделирование устройства, описанного кодом hdl

- •2.8 Таблица истинности масштабируемого устройства

- •2.9 Функциональная схема масштабируемого устройства

- •2.10 Моделирование масштабируемого устройства

- •2.11 Код на hdl масштабируемого устройства

- •2.12 Схема из rtl viewer для кода hdl масштабируемого устройства

- •2.13 Моделирование масштабируемого устройства, описанного кодом hdl

- •3 Реализация функции на основе мультиплексора

- •3.1 Таблица истинности

- •3.2 Функциональная схема

- •3.4 Моделирование функциональной схемы

- •4 Реализация функции на основе дешифратора

- •4.1 Таблица истинности

- •4.2 Функциональная схема

- •3.4 Моделирование функциональной схемы

3.2 Функциональная схема

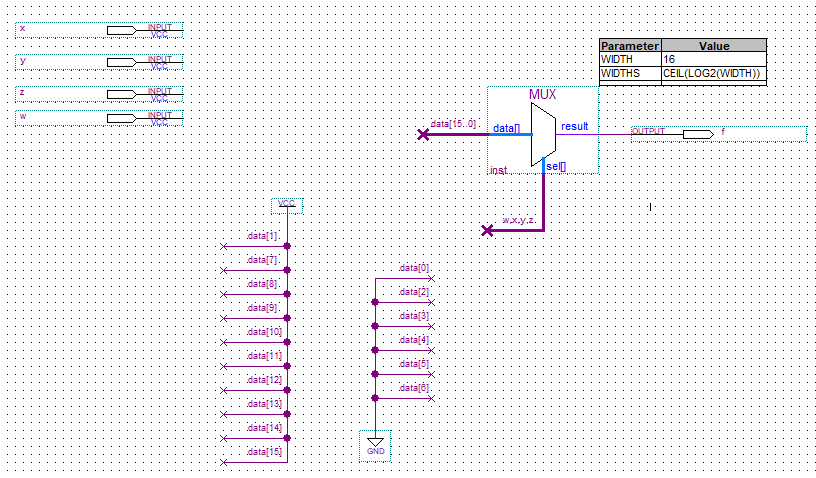

На рисунке 27 представлена функциональная схема логической функции на основе мультиплексора.

Рисунок 27 – Функциональная схема логической функции на основе мультиплексора

3.4 Моделирование функциональной схемы

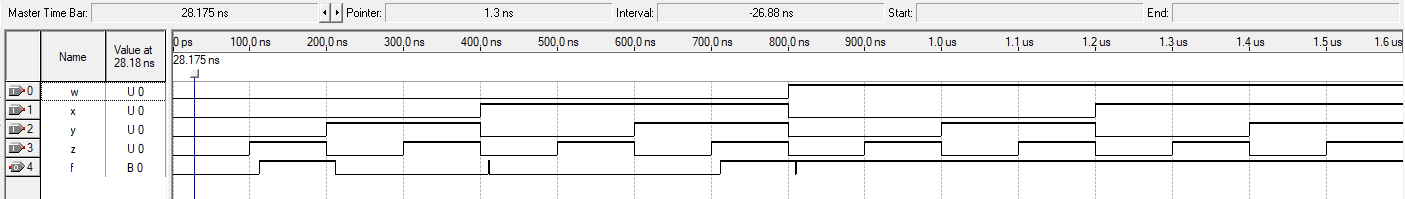

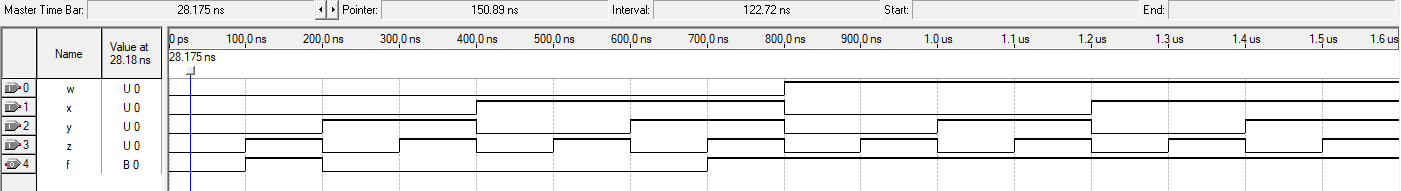

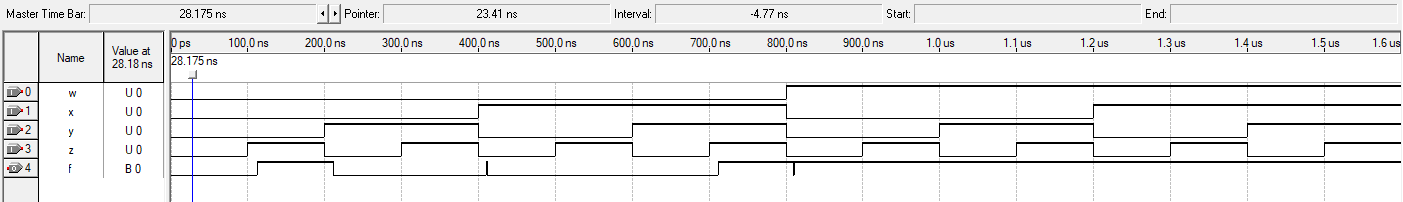

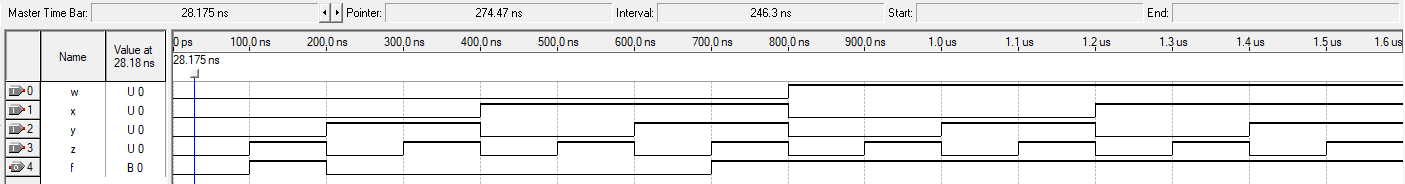

На рисунке 28 - 29 представлены результаты временного и функционального моделирования логической функции на основе мультиплексора.

Рисунок 28 – Результат временного моделирования логической функции на основе мультиплексора

Рисунок 29 – Результат функционального моделирования логической функции на основе мультиплексора

Результат временного и функционального моделирования совпадает со значениями из таблицы истинности, представленной в таблице 5.

4 Реализация функции на основе дешифратора

4.1 Таблица истинности

В таблице 5 представлена таблица истинности для логической функции F = .

Таблица 6 – Таблица истинности для функции

Входы |

Выход |

||||

W |

X |

Y |

Z |

F |

|

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

0 |

1 |

1 |

|

0 |

0 |

1 |

0 |

0 |

|

0 |

0 |

1 |

1 |

0 |

|

0 |

1 |

0 |

0 |

0 |

|

0 |

1 |

0 |

1 |

0 |

|

0 |

1 |

1 |

0 |

0 |

|

0 |

1 |

1 |

1 |

1 |

|

1 |

0 |

0 |

0 |

1 |

|

1 |

0 |

0 |

1 |

1 |

|

1 |

0 |

1 |

0 |

1 |

|

1 |

0 |

1 |

1 |

1 |

|

1 |

1 |

0 |

0 |

1 |

|

1 |

1 |

0 |

1 |

1 |

|

1 |

1 |

1 |

0 |

1 |

|

1 |

1 |

1 |

1 |

1 |

|

4.2 Функциональная схема

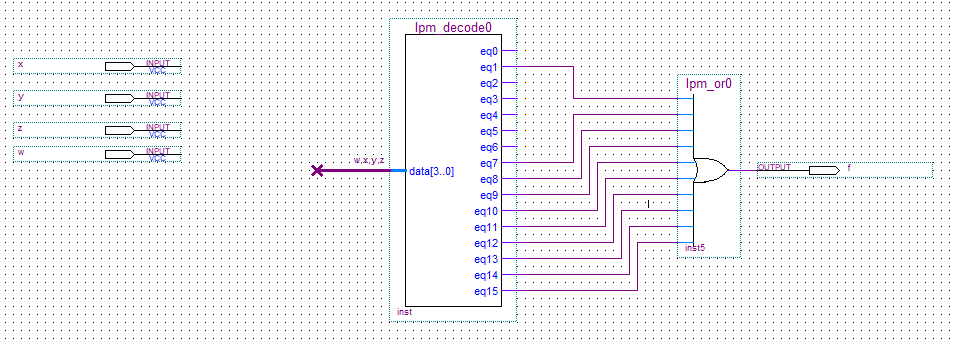

На рисунке 30 представлена функциональная схема логической функции на основе дешифратора.

Рисунок 30 – Функциональная схема логической функции на основе дешифратора

3.4 Моделирование функциональной схемы

На рисунке 31 - 32 представлены результаты временного и функционального моделирования логической функции на основе дешифратора.

Рисунок 31 – Результат временного моделирования логической функции на основе дешифратора

Рисунок 32 – Результат функционального моделирования логической функции на основе дешифратора

Результат временного и функционального моделирования совпадает со значениями из таблицы истинности, представленной в таблице 6.

ВЫВОДЫ

В ходе данной лабораторной работы были созданы мультиплексоры и демультиплексоры на разных базисах, а также реализована функция на мультиплексоре и дешифраторе.

Для начала был реализован мультиплексор 4-1 в базисе И, ИЛИ, НЕ на холсте .bdf, также он был описан на VHDL. После чего этот мультиплексор был промоделирован в двух режимах: функциональном и временном. Полученные результаты совпали с результатами в таблице истинности, составленными для мультиплексора 4-1. После этого было произведено масштабирование мультиплексора до 8-1 на основе созданного символа. Мультиплексор с наращиванием также был описан на VHDL и промоделирован в двух режимах. Результаты также совпали с таблицей истинности.

Затем был реализован демультиплексор 1-8 в базисе ИИЛ-НЕ на холсте .bdf, также он был описан на VHDL. После чего этот демультиплексор был промоделирован в двух режимах: функциональном и временном. Полученные результаты совпали с результатами в таблице истинности, составленными для демультиплексора 1-8. После этого было произведено масштабирование демультиплексора до 2-16 на основе созданного символа. Демультиплексор с наращиванием также был описан на VHDL и промоделирован в двух режимах. Результаты также совпали с таблицей истинности.

И в конце были реализованы схемы логической функции F = : одна схема на основе мультиплексора, а вторая схема на основе дешифратора на холсте .bdf. После они были промоделированы в двух режимах: функциональном и временном. Полученные результаты совпали с результатами в таблице истинности, составленными для данной функции.

Отчет был оформлен согласно требованиям ОС ТУСУР 2013.