- •Цель работы

- •Постановка задачи

- •1 Мультиплексор 4-1

- •1.1 Таблица истинности

- •1.2 Формула

- •1.3 Функциональная схема

- •1.4 Моделирование функциональной схемы

- •1.6 Схема из rtl viewer для кода hdl

- •1.7 Моделирование устройства, описанного кодом hdl.

- •1.8 Таблица истинности масштабируемого устройства

- •1.9 Функциональная схема масштабируемого устройства

- •1.10 Моделирование масштабируемого устройства

- •1.11 Код на hdl масштабируемого устройства

- •1.12 Схема из rtl viewer для кода hdl масштабируемого устройства

- •1.13 Моделирование масштабируемого устройства, описанного кодом hdl

- •2 Демультиплексор 1-8

- •2.1 Таблица истинности

- •2.2 Формула

- •2.3 Функциональная схема

- •2.4 Моделирование функциональной схемы

- •2.6 Схема из rtl viewer для кода hdl

- •2.7 Моделирование устройства, описанного кодом hdl

- •2.8 Таблица истинности масштабируемого устройства

- •2.9 Функциональная схема масштабируемого устройства

- •2.10 Моделирование масштабируемого устройства

- •2.11 Код на hdl масштабируемого устройства

- •2.12 Схема из rtl viewer для кода hdl масштабируемого устройства

- •2.13 Моделирование масштабируемого устройства, описанного кодом hdl

- •3 Реализация функции на основе мультиплексора

- •3.1 Таблица истинности

- •3.2 Функциональная схема

- •3.4 Моделирование функциональной схемы

- •4 Реализация функции на основе дешифратора

- •4.1 Таблица истинности

- •4.2 Функциональная схема

- •3.4 Моделирование функциональной схемы

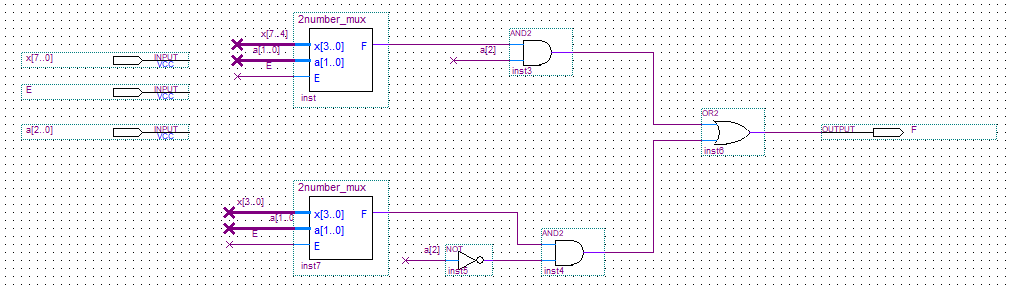

1.9 Функциональная схема масштабируемого устройства

На рисунке 8 представлена функциональная схема мультиплексора 8-1 на основе мультиплексора 4-1.

Рисунок 8 – Функциональная схема мультиплексора 8-1 на основе мультиплексора 4-1

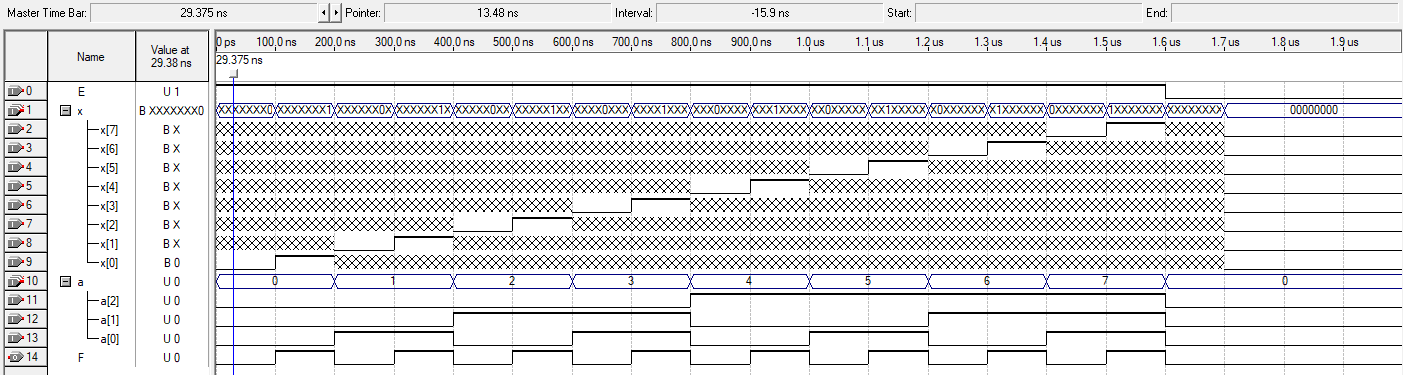

1.10 Моделирование масштабируемого устройства

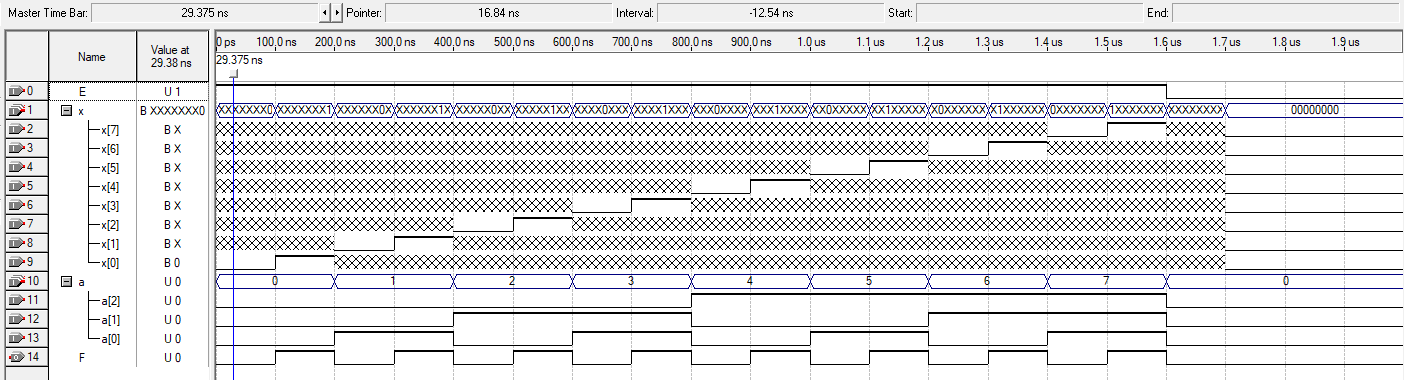

На рисунке 9 - 10 представлены результаты временного и функционального моделирования мультиплексора 8-1.

Рисунок 9 – Результат временного моделирования мультиплексора 8-1

Рисунок 10 – Результат функционального моделирования мультиплексора 8-1

Результаты совпадают со значениями из таблицы истинности представленной в таблицей 2.

1.11 Код на hdl масштабируемого устройства

Ниже представлен код описания мультиплексора 8-1 на VHDL, в котором используется модульное подключение.

library IEEE; use IEEE.STD_LOGIC_1164.all;

use IEEE.STD_LOGIC_UNSIGNED.all;

use IEEE.NUMERIC_STD.ALL;

entity mux8_1 is

port (x: in STD_LOGIC_VECTOR (7 downto 0);

a: in STD_LOGIC_VECTOR (2 downto 0);

E: in STD_LOGIC;

F: out STD_LOGIC);

end;

architecture synth of mux8_1 is

component mux4_1

port(

E: in std_logic;

x: in std_logic_vector(3 downto 0);

a: in std_logic_vector(1 downto 0);

F: out std_logic);

end component;

signal F1,F2:std_logic;

begin

MUX1: mux4_1

port map(E,x(7 downto 4),a(1 downto 0),F1);

MUX2: mux4_1

port map(E,x(3 downto 0),a(1 downto 0),F2);

F <= (F1 and a(2)) or (F2 and not a(2));

end;

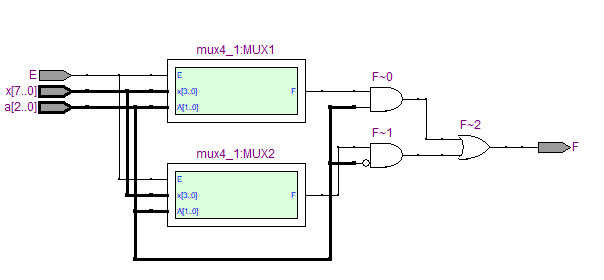

1.12 Схема из rtl viewer для кода hdl масштабируемого устройства

На рисунке 11 представлена схема из RTL viewer для VHDL кода мультиплексора 8-1. Данная схема соответствует функциональной схеме, составленной ранее.

Рисунок 11 – Схема из RTL viewer для кода мультиплексора 8-1

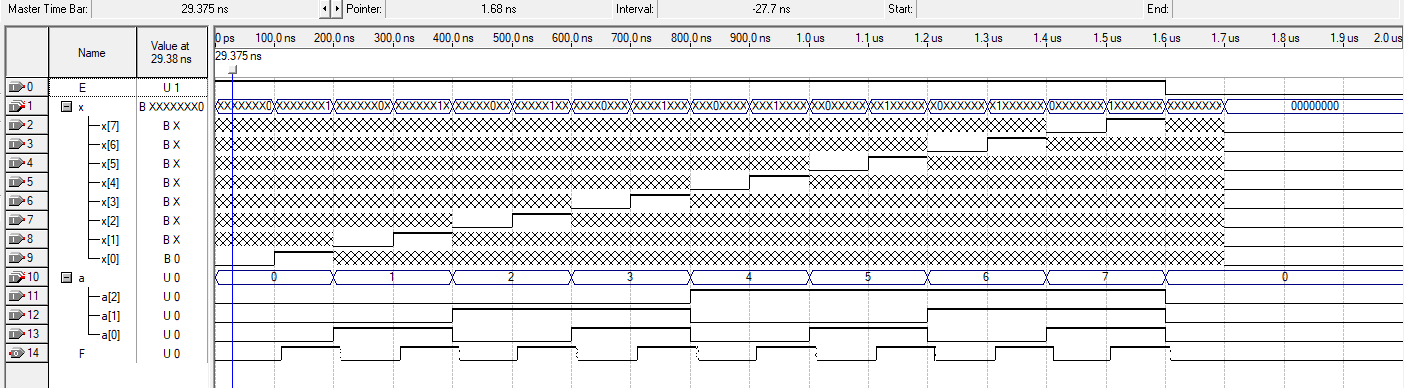

1.13 Моделирование масштабируемого устройства, описанного кодом hdl

На рисунке 12 - 13 представлены результаты временного и функционального моделирования мультиплексора 8-1, описанного на VHDL.

Рисунок 12 – Результат временного моделирования мультиплексора 8-1, описанного на VHDL

Рисунок 13 – Результат функционального моделирования мультиплексора 8-1, описанного на VHDL

Результат временного и функционального моделирования совпадает со значениями из таблицы истинности, представленной в таблицей 2.

2 Демультиплексор 1-8

2.1 Таблица истинности

В таблице 3 представлена таблица истинности для демультиплексора 1-8.

Таблица 3 – Таблица истинности для демультиплексора 1-8

Демультиплексор 1-8 |

|||||||||||||

Входы |

Выходы |

||||||||||||

E |

a2 |

a1 |

a0 |

X |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

|

1 |

0 |

0 |

0 |

b0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

b0 |

|

1 |

0 |

0 |

1 |

b1 |

0 |

0 |

0 |

0 |

0 |

0 |

b1 |

0 |

|

1 |

0 |

1 |

0 |

b2 |

0 |

0 |

0 |

0 |

0 |

b2 |

0 |

0 |

|

1 |

0 |

1 |

1 |

b3 |

0 |

0 |

0 |

0 |

b3 |

0 |

0 |

0 |

|

1 |

1 |

0 |

0 |

b4 |

0 |

0 |

0 |

b4 |

0 |

0 |

0 |

0 |

|

1 |

1 |

0 |

1 |

b5 |

0 |

0 |

b5 |

0 |

0 |

0 |

0 |

0 |

|

1 |

1 |

1 |

0 |

b6 |

0 |

b6 |

0 |

0 |

0 |

0 |

0 |

0 |

|

1 |

1 |

1 |

1 |

b7 |

b7 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

x |

x |

x |

x |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|